3.1高级语言和机器指令中的运算

- C中涉及的基本运算类型:算术运算,按位运算,逻辑运算,移位运算,位扩展和位截断运算。

1.按位运算:符号|表示按位or运算;符号&表示按位and运算;符号~表示按位not运算;符号^表示按位xor运算.

2.逻辑运算:符号||表示按位or运算;符号&&表示按位and运算;符号!表示按位not运算。

3.移位运算:移位操作有逻辑移位和算术移位。逻辑移位不考虑符号位,总是把高(低)位移出,低(高)位补0.对于无符号整数的逻辑左移,如果最高位移出的是1,则发生溢出。对于带符号整数使用补码算术移位方式。左移时,高位移出,低位补0,若左移前后符号位不同则发生溢出;右移时,低位移出,高位补符号。

4.位扩展和位截断运算:短数向长数转换时需要进行位扩展运算,扩展后的数值应该保持不变。扩展方式:0扩展和符号扩展。0扩展用于无符号数,只要在短的无符号数前添加足够的0即可;符号扩展用于补码表示的带符号整数,通过在短的带符号整数前添加足够多的符号位来扩展。 - MIPS指令系统涉及的运算有按位逻辑运算,逻辑移位,算术移位,有无符号整数的加减乘除带符号整数的符号扩展,无符号数的0扩展,单双精度浮点数的加减乘除等。

3.2基本运算部件

- 基本的运算部件是加法器、ALU和移位器,ALU的核心部件是加法器。

串行进位加法器

串行进位(又称行波进位)加法器,逻辑电路比较简单,但是最高位的加法运算,一定要等到所有低位的加法完成之后才进行,低位的进位要逐步的传递到高位,逐级产生进位,因此运算速度较慢。

并行进位加法器

- 为了提高运算速度,减少延迟时间,可以采用并行进位法,也叫超前进位或先行进位。

- 并行进位加法器的运算速度很快,形成最高进位输出的延迟时间很短,但是以增加硬件逻辑线路为代价。

- 对于长字长的加法器,往往将加法器分成若干组,在组内采用并行进位,组间采用串行进位或并行进位。

带标志加法器

要能够进行无符号整数的加减运算和带符号整数的加减运算,还需要在无符号数加法器的基础上增加相应的逻辑门电路,使加法器不仅能计算和差还能生成相应的标志性息。

算术逻辑部件

- ALU电路:利用集成电路技术可将若干位全加器,并行进位链、输出选择电路等部分集成在一块芯片上,称为多功能算术、逻辑运算部件ALU。

定点数运算

补码的加减运算

加法:[X]补+[Y]补=[X+Y]补(mod 2^n)

减法:[X]补+[-Y]补=[X-Y]补=[X+(-Y)]补(mod 2^n)

溢出

- 符号相异的数相加、符号相同的数相减,不可能发生溢出。

- 符号相同的数相加、符号相异的数相减,可能发生溢出。

- 判断是否发生溢出:

1.符号位判断:两正数相加得到负数,或两负数相加得到正数时发生溢出。

2.进位位相异或:次高位进位和最高位进位进行异或,结果为1,则表示溢出。

3.扩充运算位数:将运算数的符号位设置为00(正数)或11(负数),如果结果的符号位不是00或11,而是01或10则可判断发生溢出。

原码的加减运算

- 比较两个操作数的符号,对加法实行“同号求和,异号求差”,对减法实行“异号求和,同号求差”。

- 求和时,数值位相加,若最高位产生进位则结果溢出,和的符号位取被加数(被减数)的符号。

- 求差时,被加数(被减数)数值位加上加数(被减数)数值位的补码。

移码的加减运算

- 移码的和、差等于和、差的补码。

原码的乘法运算

原码一位乘法

- 确定乘积的符号位,由两个乘数的符号异或得到。

- 计算乘积的数值位,乘积的数值部分为两个乘数的数值部分之积。

原码二位乘法

- 对乘数的每两位取值情况进行判断,使每步求出对应于该两位的部分积,则可将乘法速度提高一倍。

补码的乘法运算

补码一位乘法

- 布斯乘法:将符号位和数值位合在一起参与运算,直接得出用补码表示的乘积,且正数和负数同等对待。

- 与推导无符号乘法算法一样,可以不考虑小数点的位置。只要最终的乘积约定好小数点位置即可。

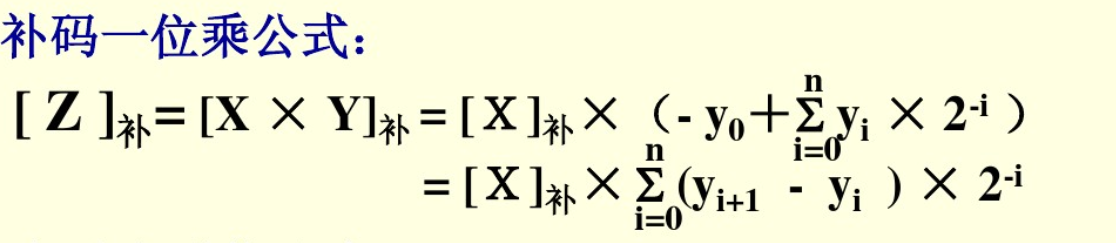

- 补码乘法运算规则:【()内表下标】

(1)乘数最低位增加一位辅助位Y(-1)=0

(2)根据Y(i) Y(i-1)的值,决定是“+[x]补”、“-[x]补”还是“+0”

(3)每次加减后,算术右移一位,得到部分积

(4)重复第(2)(3)步n次,结果得[x×y]补

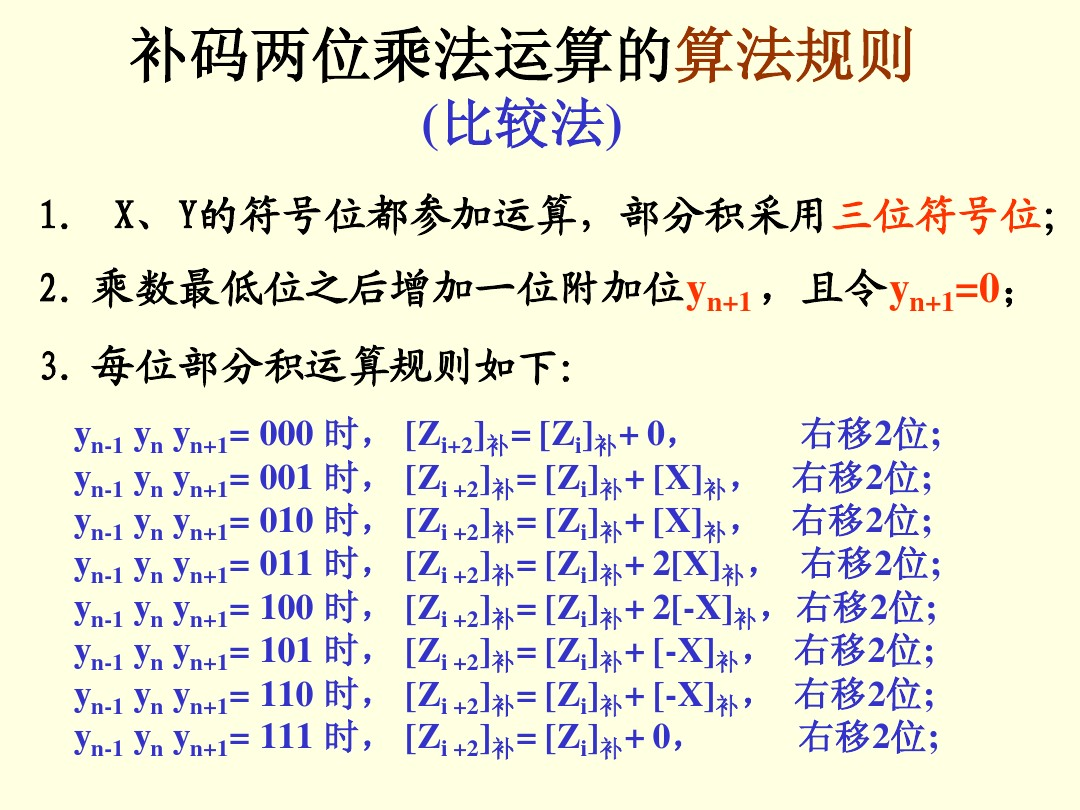

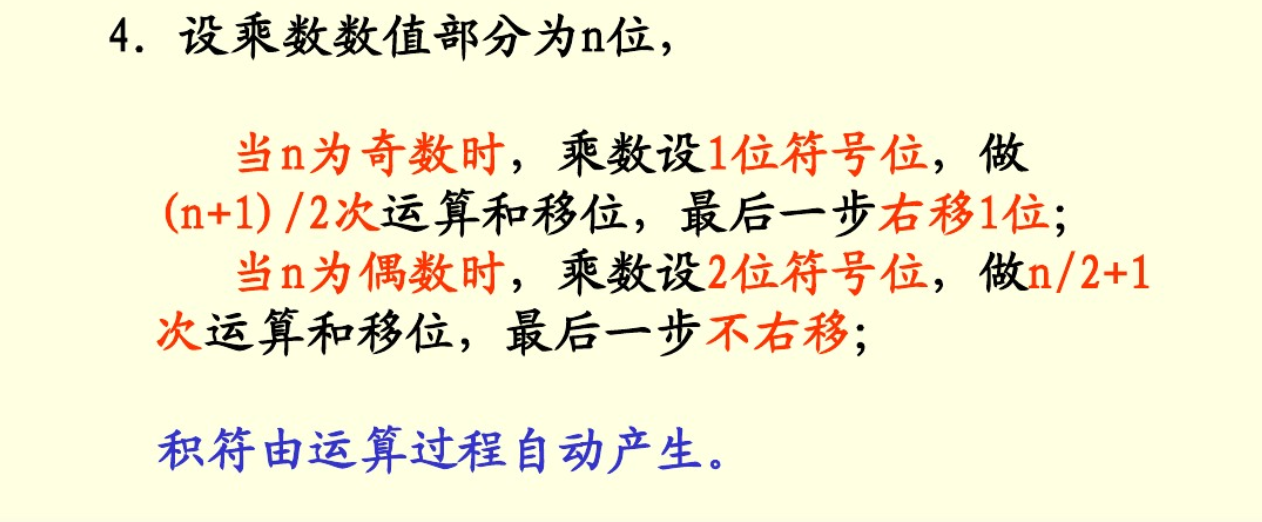

补码二位乘法

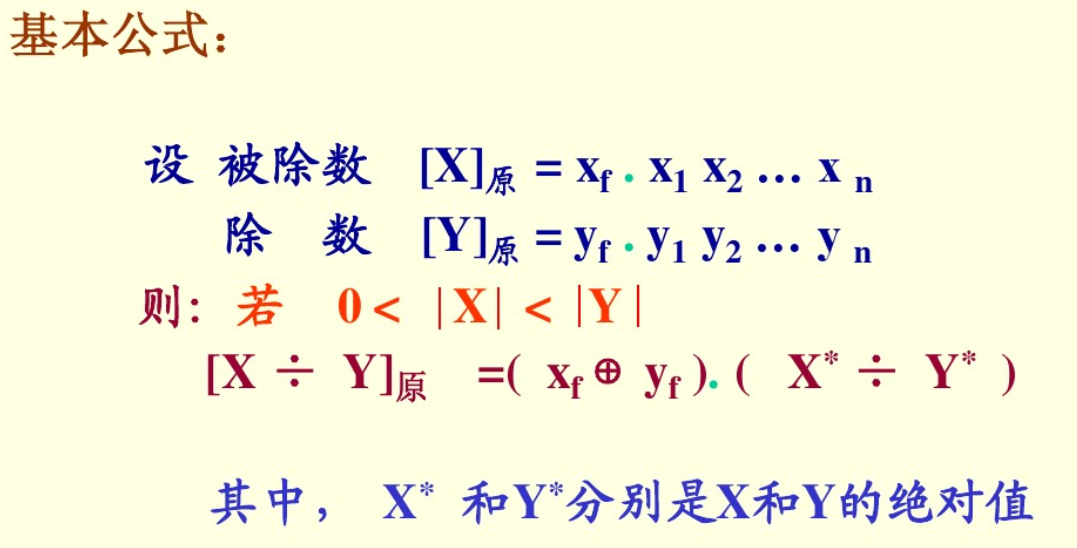

原码除法运算

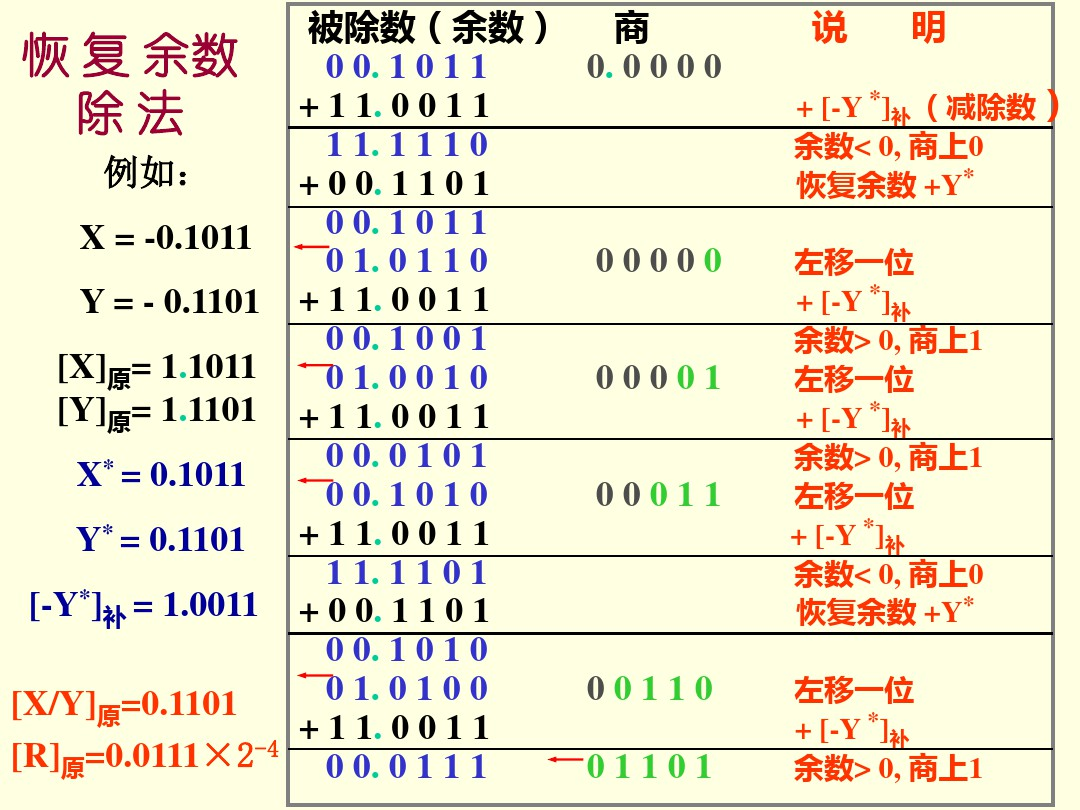

原码恢复余数除法

原码不恢复余数除法

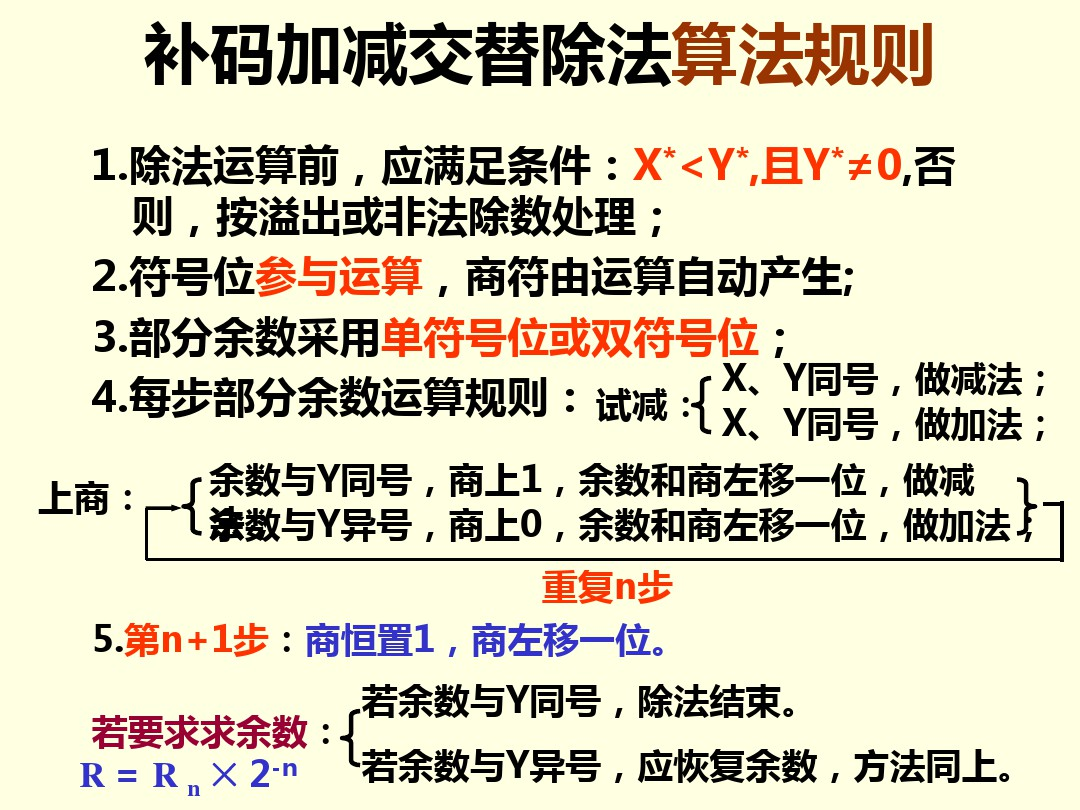

- 除法运算前,应满足条件:X<Y,且Y*≠0,否则,按溢出或非法除数处理

- 符号位不参与运算,单独处理:qf=xf⊕yf

- 部分余数采用单符号位或双符号位;

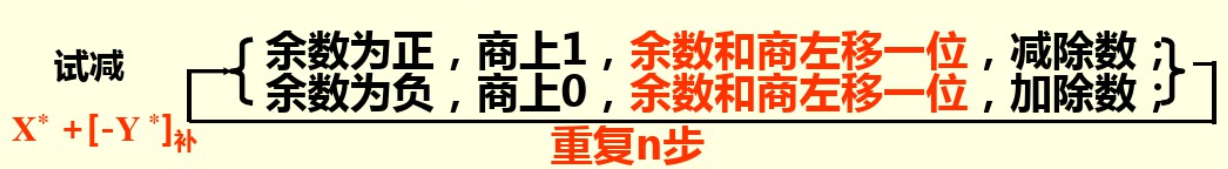

- 每步部分余数运算规则:

- 第n+1步:若余数为正,商上1,商右移一位;若余数为负,商上0,商左移一位,但当结果需要余数时,恢复余数,R=Rn×2^(-n).

补码码除法运算

3.4浮点数运算

浮点数加减运算

1.对阶:使两数的小数点位置对齐。

2.尾数加减:将对阶后的两尾数按定点加减运算规则求和(差)。

3.规格化,为增加有效数字的位数,提高运算精度,必须将求和或差后的尾数规格化。

4.舍入,为提高精度,要考虑尾数有意时丢失的数值位。

5.判断结果是否溢出。

浮点数乘除运算

- 两浮点数相乘其乘积的阶码为相乘两数阶码之和,其尾数应为相乘两数的尾数之积。

- 两个浮点数相除,商的阶码为被除数的阶码减去除数的阶码得到的差,尾数为被除数的尾数除以除数的尾数所得的商。

- 参加运算的两个数都为规格化浮点数,乘除运算都可能出现结果不满足规格化要求的问题,因此也必须进行规格化,舍入和溢出判断等操作。规格化时要修改阶码。

运算部件的组成

1.八功能的ALU:完成算术与逻辑运算;

2.16X4位寄存器组:寄存加减运算的操作数;

3.4位Q寄存器:用于接收ALU的输出数据,具有左、右移功能;

4.3选1和2选1多路开关:用于多路地址、数据的选择。