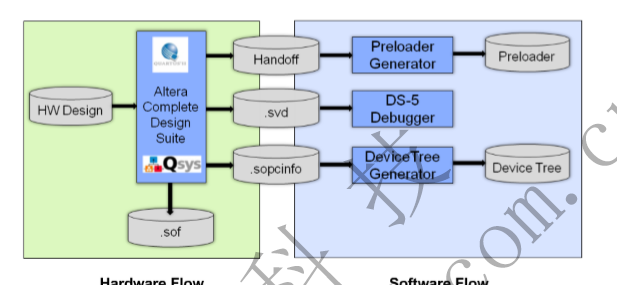

1、Qsys 与 Qurartus II 生成的档案

搭建好的硬件系统,经过 Qsys generate 还有 Quartus II 编译后,会产生三种文件提 供给 SoC 系统以进行后续软件开发。如图所示,这三种文件分別是:

1. SOPC info file(.sopcinfo):文档用于生成 Device Tree

2. Handoff Folder:里面有关于产生 preloader 相关配置文件

3. System View Descr(.svd):用于 DS-5 debug 功能

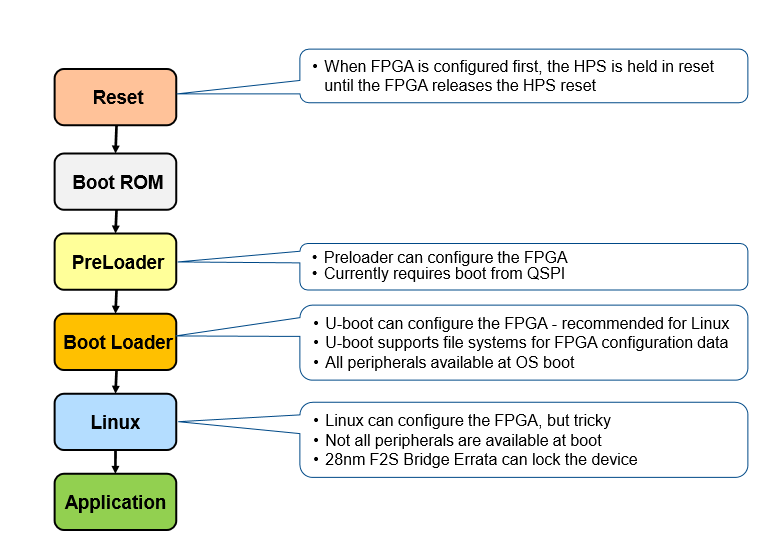

可以看到Preloader image file以及Device Tree是软件流运行所需文件,这里就需要了解一下Altera SOC fapa的启动步骤:

第1步:起动固化在内部的厂家ROM程序,根据起动引脚的配置,选择从哪里起动(QSPI,SD,NAND);

第2步:加载Preloader程序到芯片内部的RAM缓存里运行,这一步很重要,有些重要的参数在这一步设置,比方说,IO口复用,DDR3参数等。

第3步:由Preloader程序加载uboot到DDR3里运行。假如在第2步中,DDR3参数设置不正确,就会报Bad image with mismatched CRC校验错误,就没反应了。

第4步:uboot读取起动配置文件(uboot.scr),没有的话,就直接加载zImage。

第5步:再加载设备树。

具体可以参照下图:

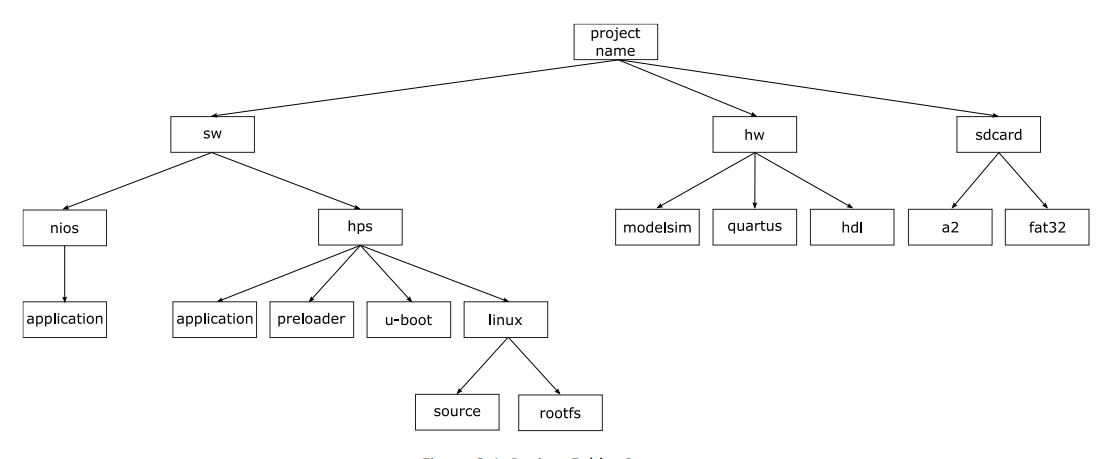

工程的文件结构如下:

2、 生成Preloader Image 文件

可以看出,preloader 是启动中很重要的一步,他可以保存在外部存储中,也可以保存在FPGA结构中。它主要完成以下几个操作

- SDRAM接口初始化

- 通过扫描管理器对HPS I/O进行配置

- 通过系统管理器配置多功能引脚

- 通过时钟管理器配置HPS时钟

- 初始化存储下一步软件程序的存储器(NAND,SD/MMC,QSPI)

- 加载下一步的启动软件程序到SDRAM进入到下一步。

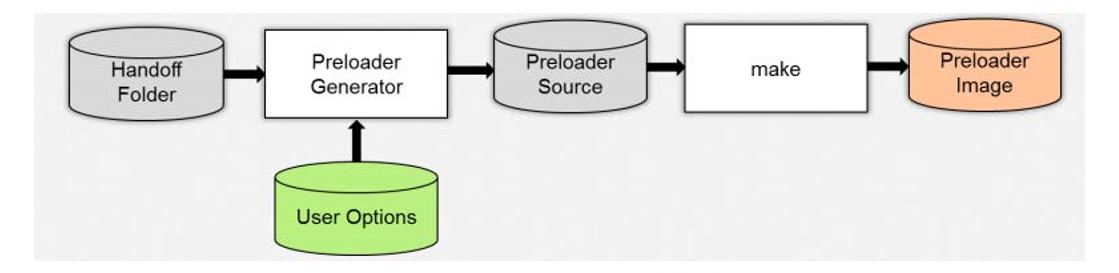

因为我们可以通过Qsys删减ARM端外设及添加与FPGA相连的组件。我们自定义的设定在经过Qsys generate和Quartus II compile时会产生一些HPS和FPGA相关的配置文件。在进行软件设计时,这些文件可以通过BSP Editor抓换成Preloader需要的输入档案。以进一步生成Image文件。下图是preloader image的制作流程。

步骤如下(这里以HPS基本概念及其设计里的工程为例):

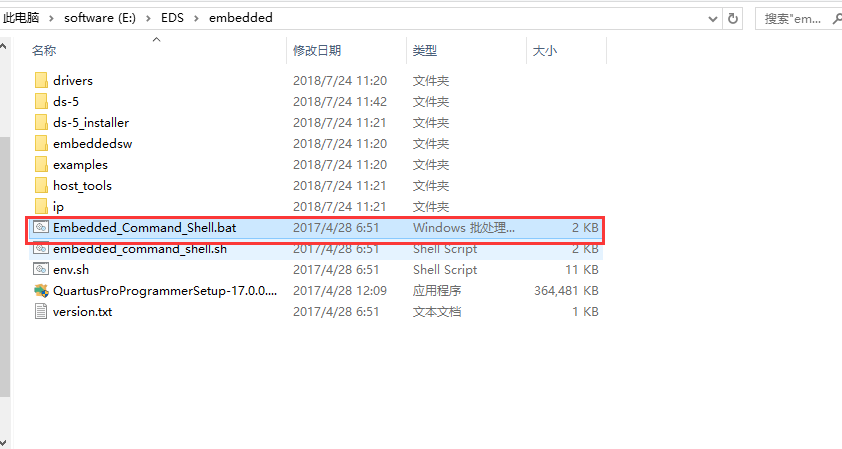

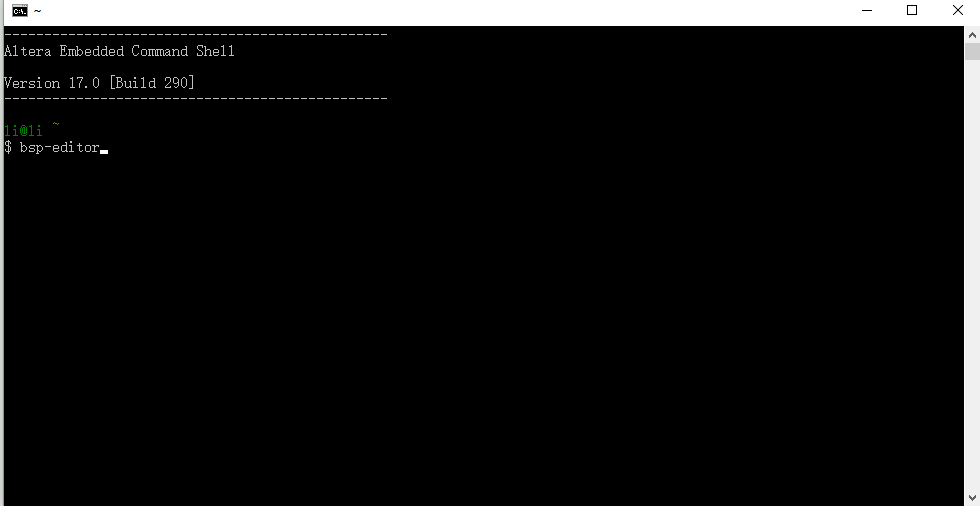

1. 进入 SoC EDS 的安装路径并打开 Embedded Command Shell。打开<your path>embedded 并执行 “Embedded_Command_Shell.bat”。Altera Embedded Command Shell 窗口将会出现。

2. 在Embedded_Command_Shell中启动 BSP Editor:在窗口内输入 bsp-editor 并按 enter 键

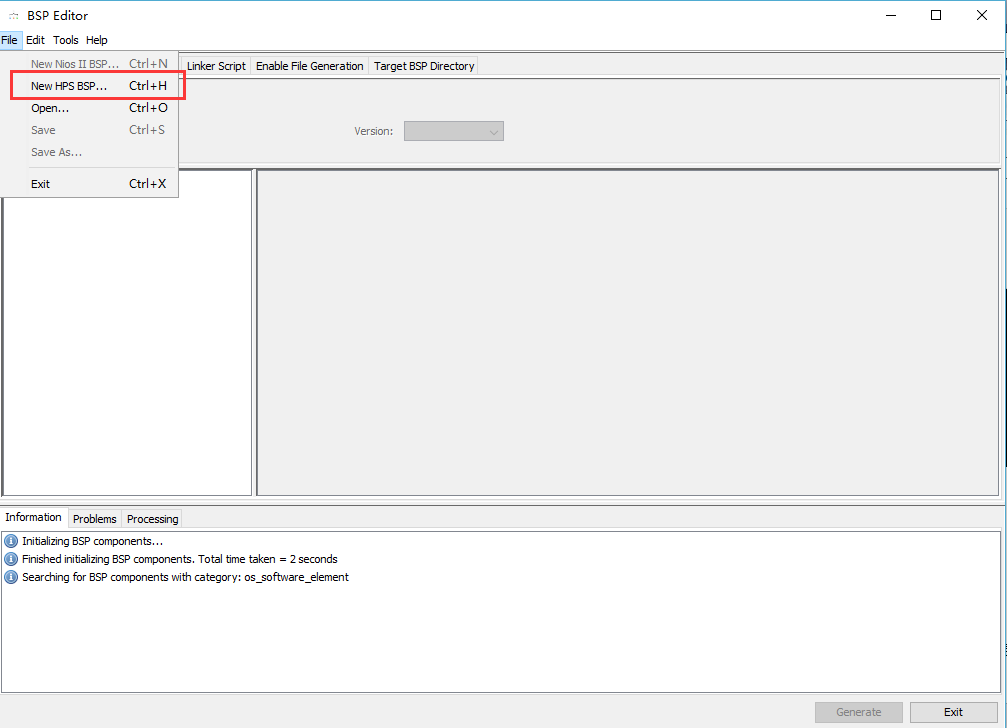

3. 产生新的 BSP:打开 bsp-editor 后选择菜单 File --> New BSP 来创建新的 BSP

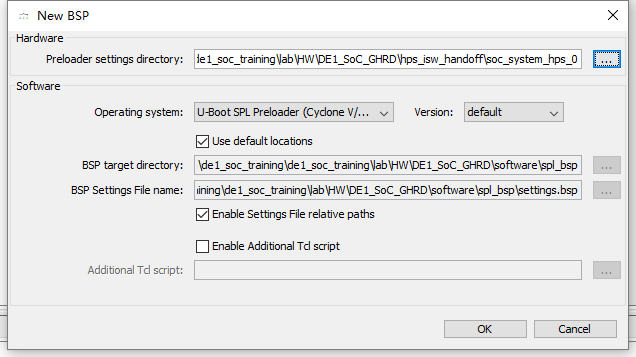

4. 在 New BSP 的窗口下选择 Preloader Setting Directory 的路径,把路径指 向上节实验工程 DE1_SoC_ghrdhps_isw_handoffsoc_system_hps_0(例如我的就是 C:UsersliDesktoppeixunde1_soc_trainingde1_soc_traininglabHWDE1_SoC_GHRDhps_isw_handoffsoc_system_hps_0无论何时使用Qsys生成SoC设计并在Quartus中编译,都将生成“hps_isw_handoff”文件夹。此文件夹包含预加载器配置时钟,IO和SDRAM控制器所需的配置信息。)。如图所示:

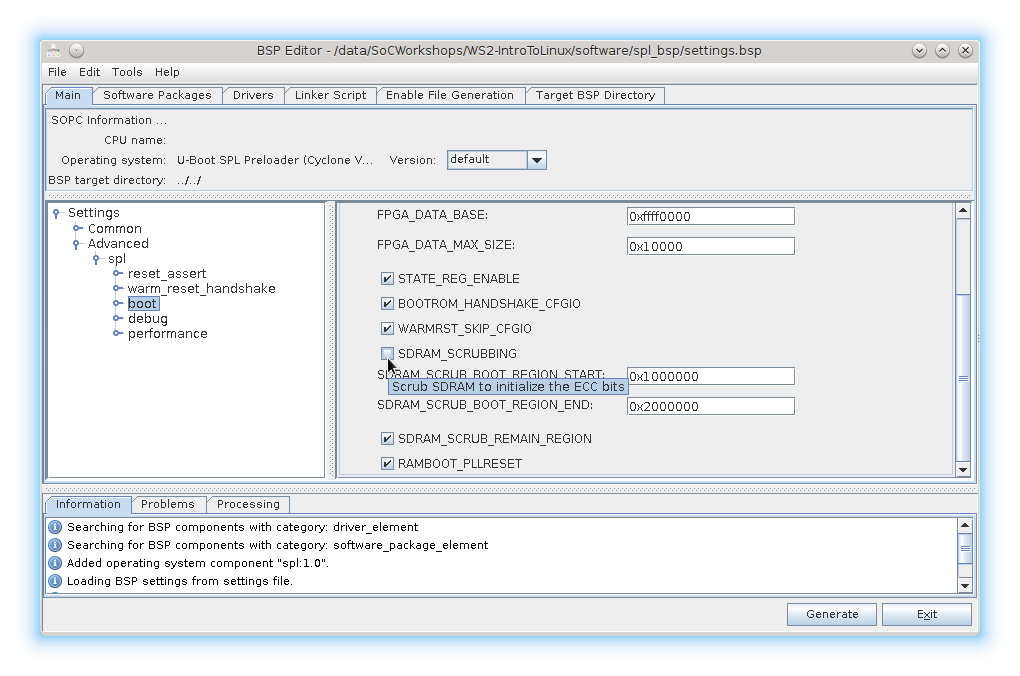

选择OK ,会BSP编辑器窗口中,我们希望接受大多数默认设置。如果你的开发板支持ECC SDRAM存储,则应选择下面显示的SDRAM擦除选项,否则请将其取消选中。(DE1-SOC不需要此操作及下面的操作,这里直接采用默认的,然后generate就可以了)

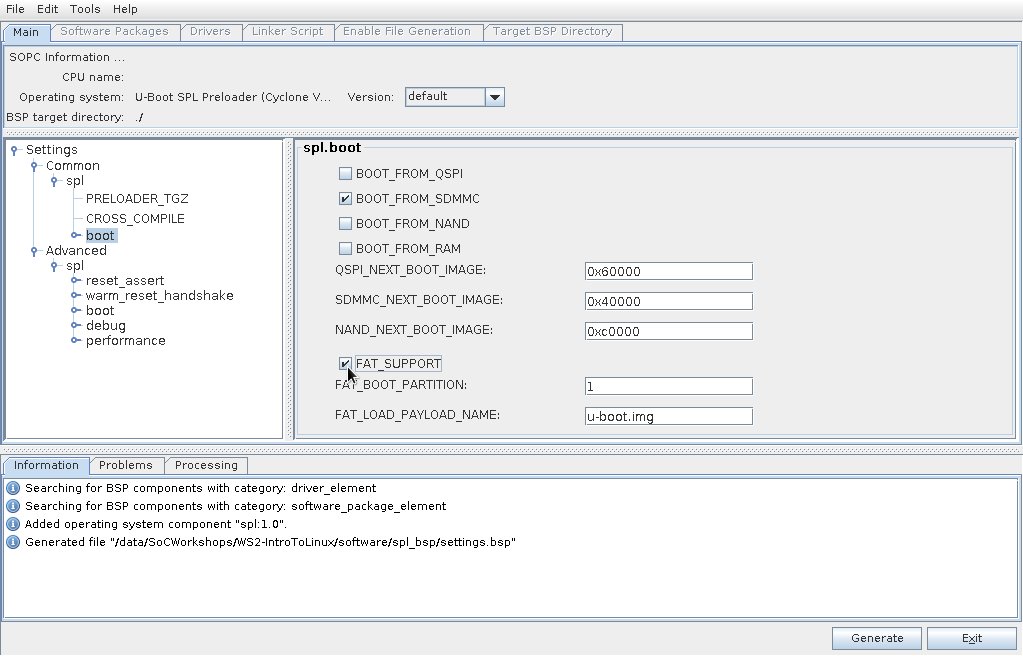

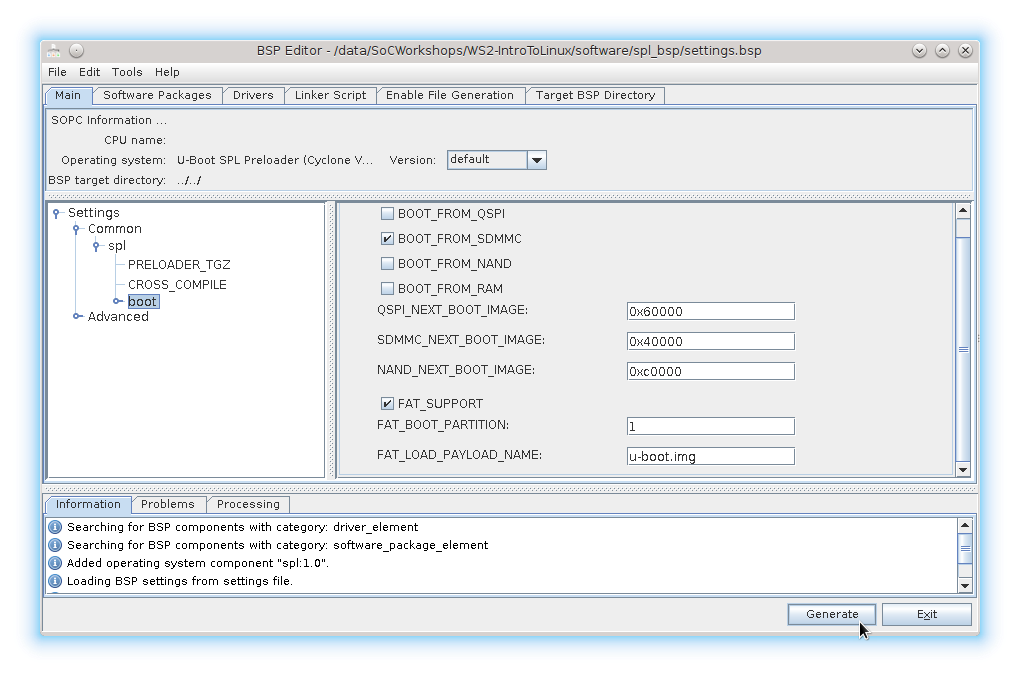

Preloader可以从引导设备中的绝对原始地址或SDMMC设备中的FAT分区加载下一级引导映像。在本实验中,您将配置Preloader以从FAT分区加载u-boot,该分区是SD卡上的分区1。在“设置”下,展开“公共”和“拆分”,然后选择“启动”。在“spl.boot”视图中,选中标记为“FAT_SUPPORT”的框。确保“FAT_BOOT_PARTITION”设置为1,“FAT_LOAD_PAYLOAD_NAME”设置为“u-boot.img”。这些应该是默认设置。

现在单击Generate按钮为Preloader生成BSP。

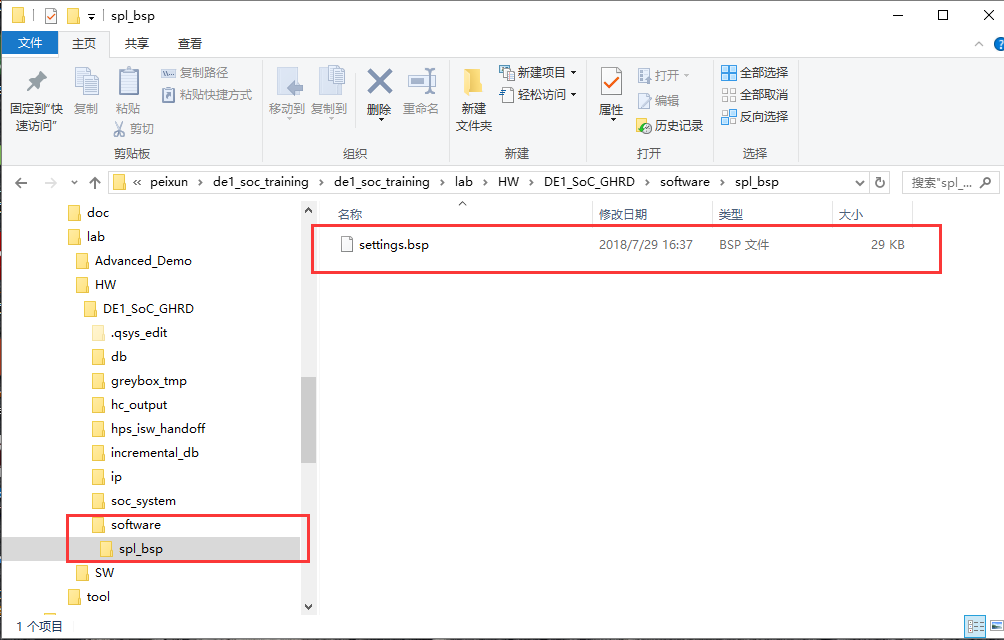

5. 选择 OK 来产生 BSP setting 文档以及文件夹。系统将在工程內产生一个 software 的文件夹,并生成一个 settings.bsp 文 档,如图所示

| 文件 | 描述 |

|---|---|

| settings.bsp | 预加载器设置文件,包含预加载器生成器的设置 |

| Makefilefile | Makefile用于构建Preloader |

| generated | 包含基于切换文件夹中的信息生成的源代码的文件夹 |

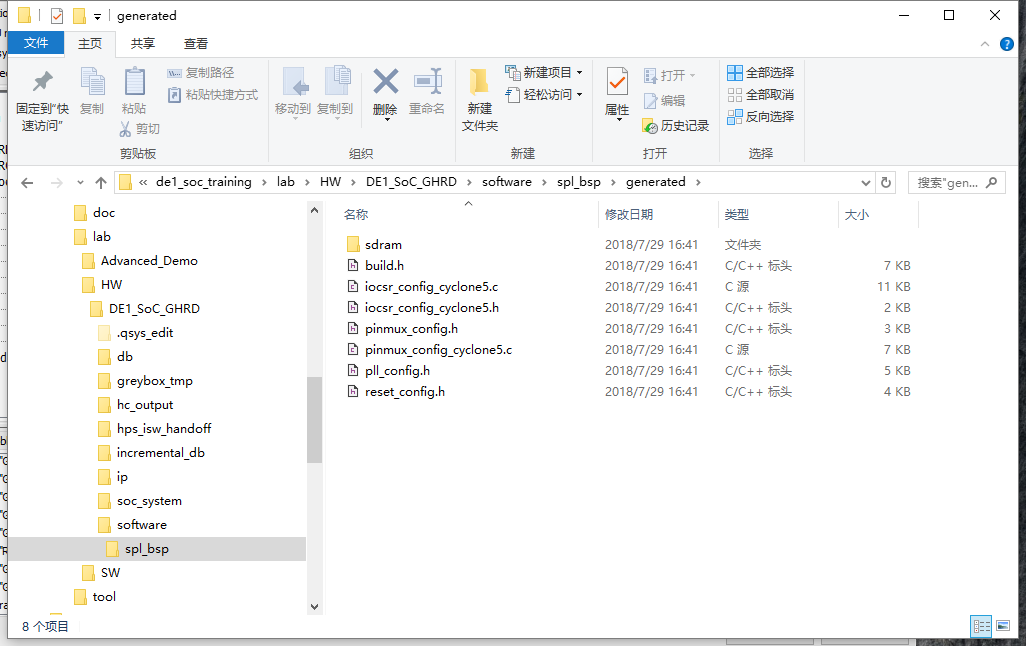

| preloader.ds | ARM DS-5 AE,可用于加载Preloader |

6.当生成档案完 成后,按下 exit 完成任务离开窗口, 接下来按下 Generate 生成 preloader 的原始档以及 Makefile。进入 softwarespl_bspgenerated 的子文件夹并查看产生的文档。可以看到 之前在 Qsys 中有关 HPS 的相关设定已经转换成..h 头文件以配置 preloader source code 对应设置。如图所示:

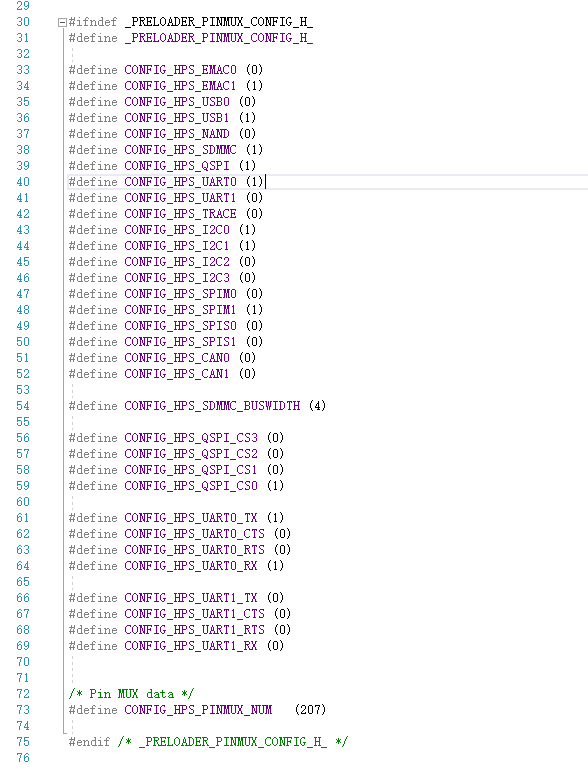

7、以 pinmux_config.h 为例,可以看到 HPS 的外设的配置使用情况,其中“(1)” 代表该外设被使用,如图所示:

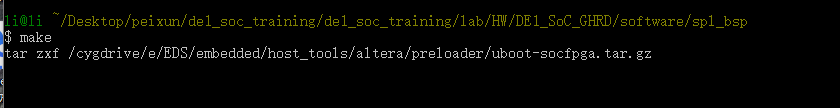

8.. 在 shell 窗口,进入项目位置里的 softearespl_bsp 活页夹,然后输入 make 指令如图所示(若 PC CPU 内核为多核,如 4 核,可输入 make -j8 进行多线程编译以提高编译效率)。

Makefile(也由Preloader Generator创建)执行以下步骤:

- 提取Preloader源代码的固定部分

- 使用Preloader源代码的固定和生成部分构建Preloader可执行文件

- 将可执行文件转换为二进制文件,然后将引导ROM所需的标头添加到它

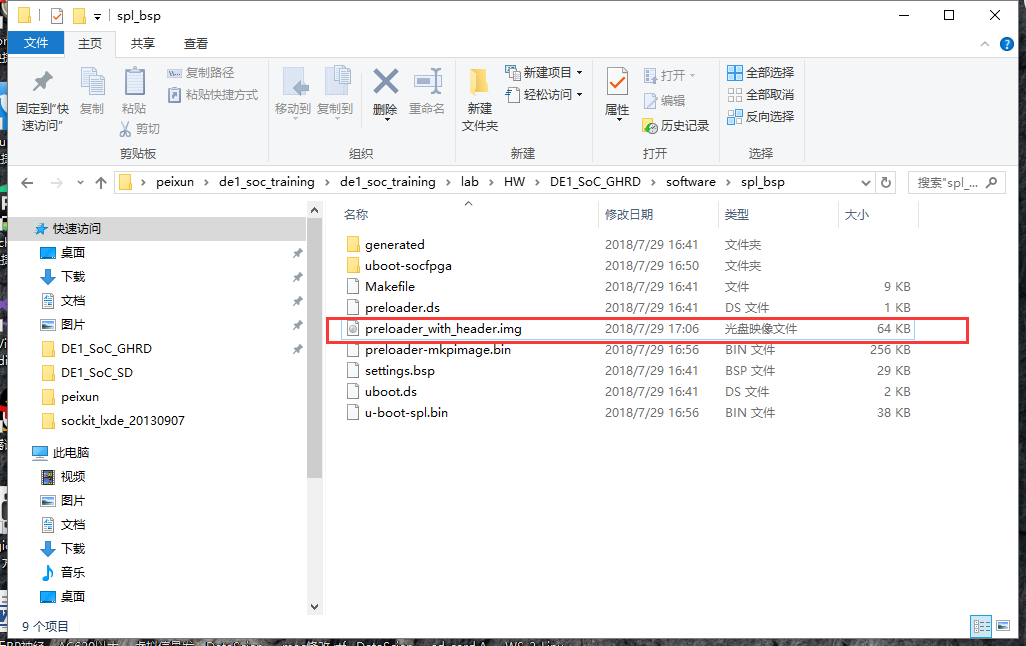

9.完成后以下文件内置于“software / spl_bsp /“文件夹:

| 文件 | 描述 |

|---|---|

| uboot-socfpga/spl/u-boot-spl | 预加载器ELF文件 |

| uboot-socfpga/spl/u-boot-spl.bin | 预加载器二进制文件 |

| preloader-mkpimage.bin | 具有引导ROM所需标头的预加载器映像 |

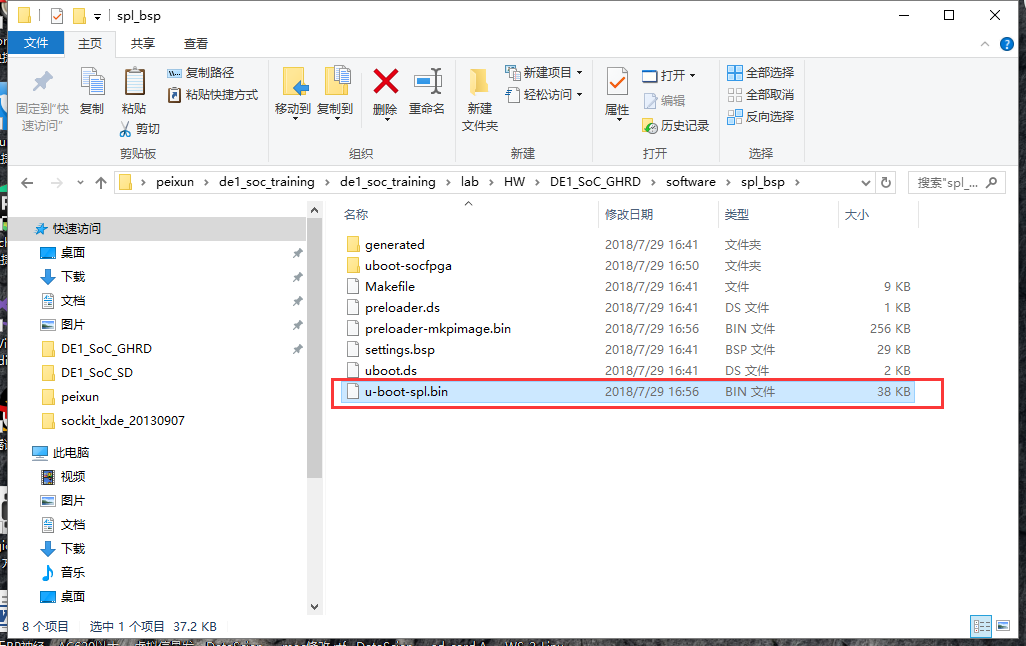

10. 下一步是产生 preloader 的 image file。先将sotwarespl_bspuboot-socfpgaspl下的u-boot-spl.bin复制到向上 两层的sotwarespl_bsp文件夹下,如图所示:

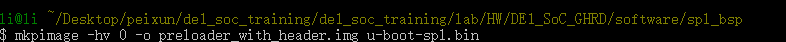

12.在 shell 窗口下,路径也重新定位于此。 并输入指令 mkpimage –hv 0 –o preloader_with_header.img u-boot-spl.bin 如图所示:

如此便可以产生 preloader_with_header.img 文件,产生的新的 preloader image file 即可在 linux 环境下,通过输入相应命令更新到 boot SD card。

3、 生成Devixe Tree

1.设备树的起源

linux 2.6及之前,大量板级信息被硬编码到内核里,十分庞大,大量冗余代码;

linux 2.6之后,引入了设备树;

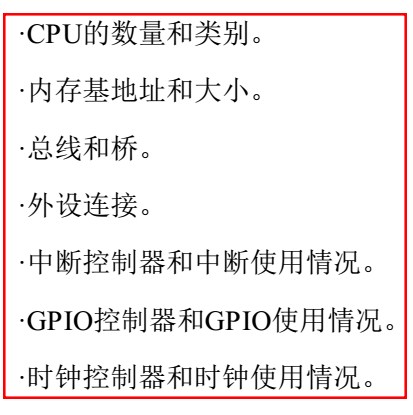

设备树源于OpenFirmware,描述硬件的数据结构。由一些列节点node和属性property组成,通常包括下列信息:

本质上是画一棵CPU、总线、设备组成的树,Linux内核会把设备树展开成platform_device、i2c_client、spi_device等设备,而这些设备用到的内存、中断等资源,也会传递个内核,内核会将这些资源绑定给展开的相应设备。

典型SOC的内容通常是非常静态的。因此,描述SOC的设备树源非常静态,通常通过手动编辑文本文件来创建。但是,当电路板包含FPGA时,可能包含可以频繁更改的复杂设计,用于创建设备树源的工具非常有用。

总的来说,Device Tree是一种有关硬件系统描述的数据结构,他可以描述整个系统上挂载了多少种硬件。通过Device Tree,系统上的硬件信息都可以传递给OS(linux)。如此便可以不用在kernel内放置大量的代码。这种特性对于硬件里有FPGA情况下提供了很大的灵活性。

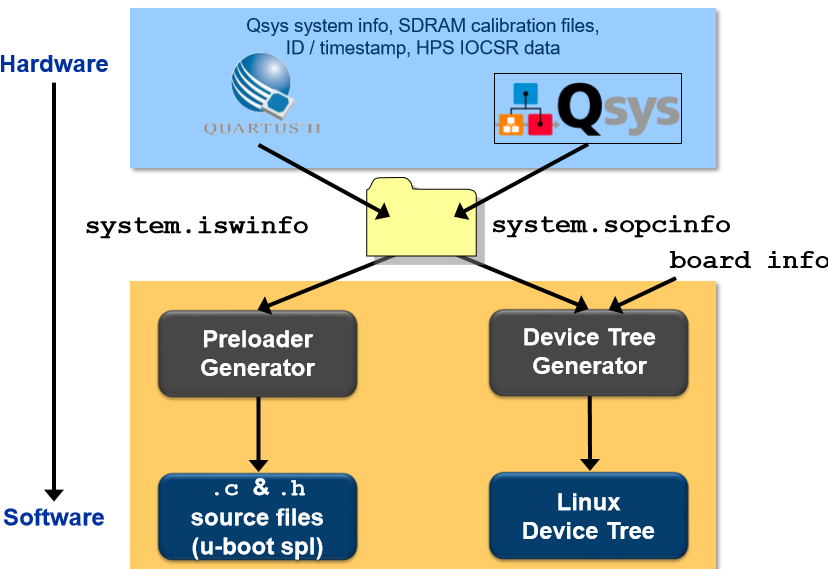

2.设备树流程

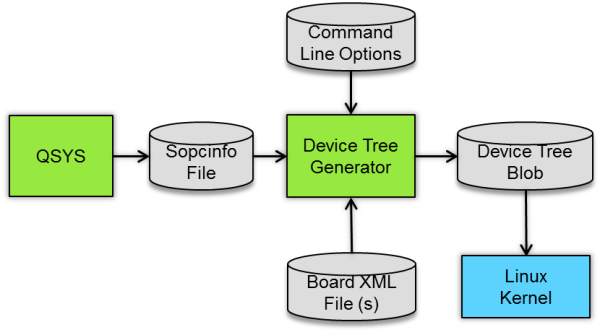

下图描绘了生成设备树的整个流程。

当Qsys产生出 FPGA 的设计后(.sopcinfo),可以使用Altera SoC EDS工具里的Device Tree Generator 来产生 Device Tree 的源文档(dts)。它描述了有关 HPS 的外设还有 选择使用到的 FPGA Soft IP 以及用户自定义的外设等信息。 .dtb文件是.dts文件被Device Tree Compiler编译后生成的二进制格式的Device Tree 描述,可被 Linux 内核解析。通常在我们为开发板制作 NAND、Sdcard 启动 image 时, 会为.dtb 文件预留一个很小的存放区域(FAT 分区)。之后 bootloader 在引导 kernel 的过程中,会先读取该.dtb 到内存。更多关于 Device Tree 的介绍可以参考的链接。

设备树的组成和结构DTS/DTC/DTB

dts:文本

dtc:编译dts的

dtb:编译后的二进制文件

3、更新 preloader

我们也 可 以 同 时 更 新 u-boot.img 文件和 preloader.img 文 件 。 将softwarespl_bspuboot-socfpga 目录下 生 成 的 u-boot.img 文件也拷贝到softwarepreloader 中,

4.设备树生成步骤

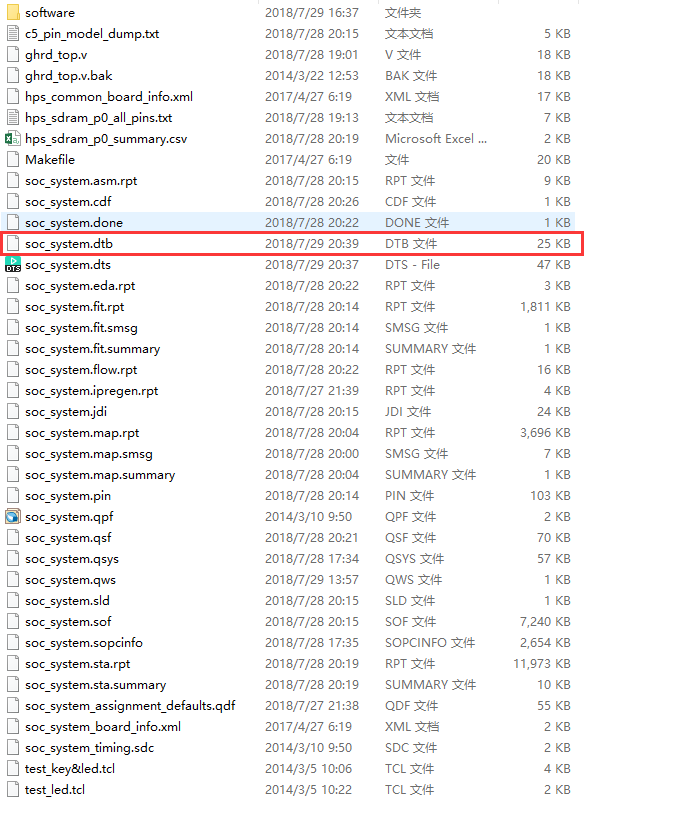

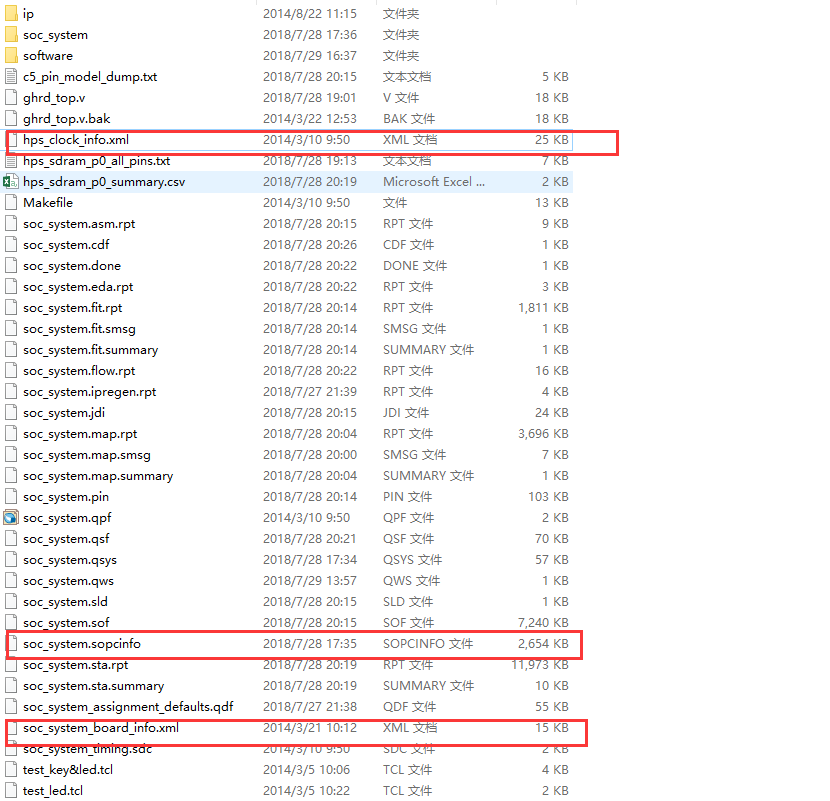

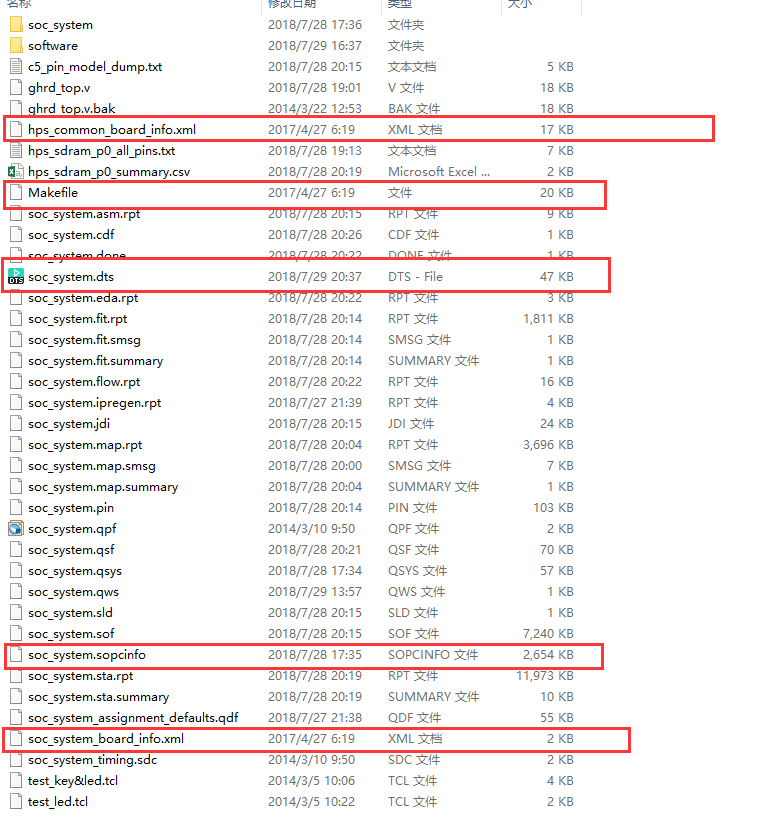

1.开启前面的工程文件夹,检视是否 Qsys 有生成 soc_system.sopcinfo 文件。同时确认是否有 hps_clock_info.xml 和 soc_system_board_info.xml. Device Tree Generate 将使用这两个文件来产生 出.dts 文件。

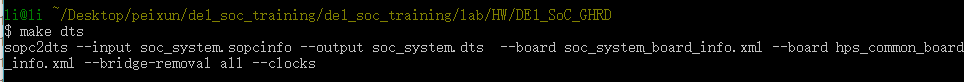

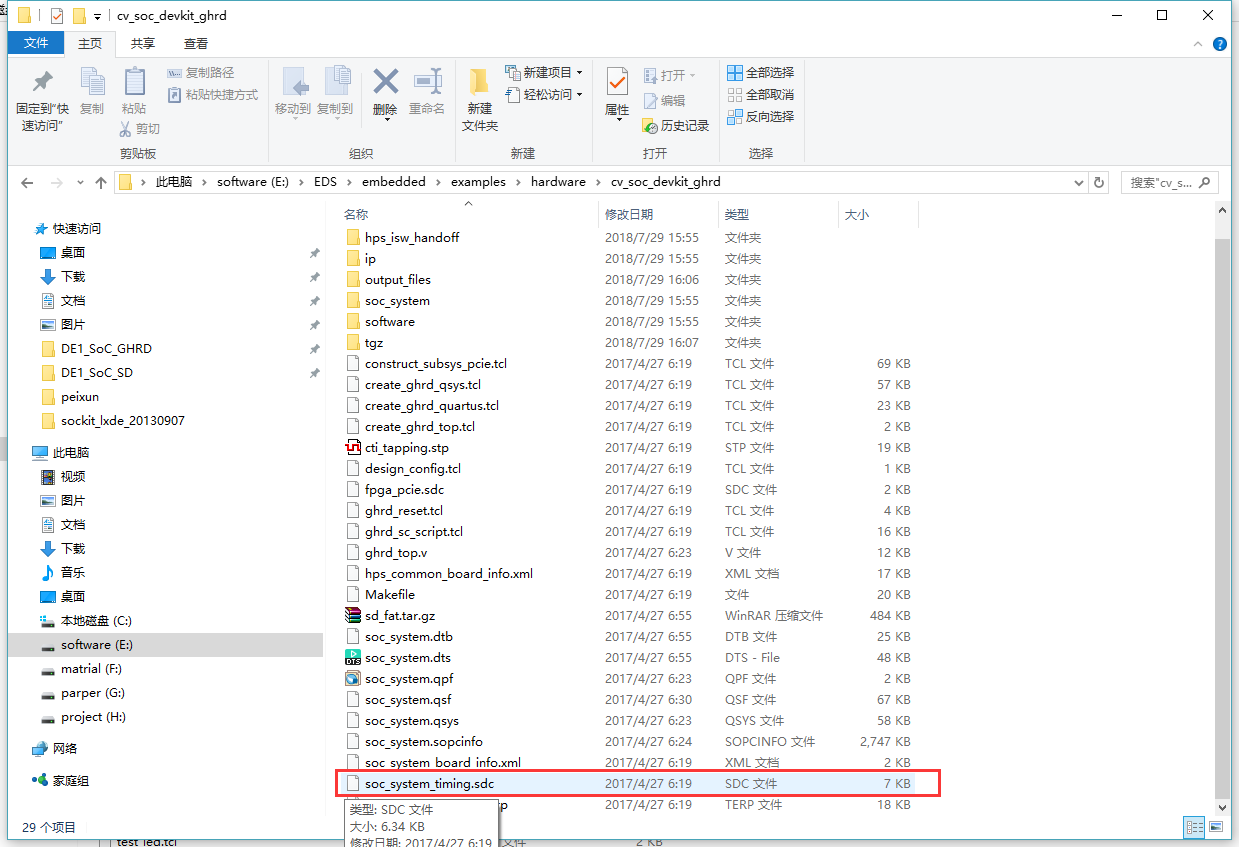

2、在shell中进入工程目录,输入以下的命令以产生 .dts 文件,这里直接使用这三个文件,用原来的Makefile文件来生成dts和dtb,dts能够生成,但是有错误,dtb直接无法生成。原因就在于,这是因为在新版本的Quartus II软件中,第二个使用的不再是hps_clock_info.xml文件,而是hps_common_board_info.xml。这个文件我们可以在SOCEDS软件安装目录下的exampleshardwarecv_soc_devkit_ghrd 文件夹下找到

: 将其中的两个xml文件hps_common_board_info.xml、soc_system_board_info.xml和一个Makefile复制出来,粘贴到我们自己的工程目录下,并将原来的三个文件删除即可。然后make dts在文件夹下可以看到.dts文件已经被生成

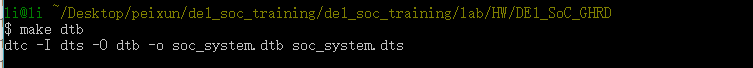

2、接着输入make dtb来产生 .dtb 文件如图所示: