∑–△型模数转换器(ADC)

1.概述

近年来,随着超大规模集成电路制造水平的提高,Σ-Δ型模数转换器正以其分辨率高、线性度好、成本低等特点得到越来越广泛的应用。Σ-Δ型模数转换器方案早在20世纪60年代就已经有人提出,然而,直到不久前,在器件商品化生产方面,这种工艺还是行不通的。今天,随着1微米技术的成熟及更小的CMOS几何尺寸,Σ-Δ结构的模数转换器将会越来越多地出现在一些特定的应用领域中。特别是在混合信号集成电路(Mixed-signal ICs,指在单一芯片中集成有模数转换器、数模转换器以及数字信号处理器功能的集成电路芯片)中。目前,Σ-Δ型模数转换器主要用于高分辨率的中、低频(低至直流)测量和数字音频电路。用于低频测量的典型芯片有16位分辨的AD7701,24位分辨的AD7731等;用于高品质数字音频场合的典型芯片有18位分辨率的AD1879等。随着设计和工艺的水平的提高,目前已经出现了高速Σ-Δ型模数转换器产品。例如AD7723(1.2MSPS),AD9260(2.5MSPS)等。

2. ∑–△型ADC的理论基础

与一般的ADC不同,∑–△型ADC不是直接根据抽样数据的每一个样值的大小进行量化编码,而是根据前一量值与后一量值的差值即所谓的增量的大小来进行

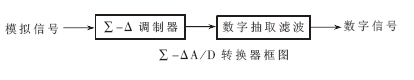

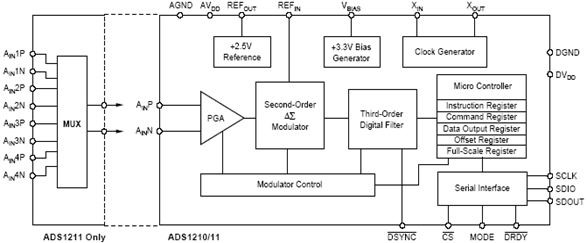

量化编码。从某种意义上讲,它是根据信号波形的包络线进行量化编码的。∑–△型ADC由两部分组成,第一部分为模拟∑–△调制器,第二部分为数字抽取滤波器,如下图所示。

∑–△调制器以极高的抽样频率对输入模拟信号进行抽样,并对两个抽样之间的差值进行低位量化,从而得到用低位数码表示的数字信号即∑–△码;然后将这种∑–△码送给第二部分的数字抽取滤波器进行抽取滤波,从而得到高分辨

率的线性脉冲编码调制的数字信号。因此抽取滤波器实际上相当于一个码型变换器。由于∑–△调制器具有极高的抽样速率, 通常比奈奎斯特抽样频率高出

许多倍,因此∑–△调制器又称为过抽样ADC转换器。这种类型的ADC采用了极低位的量化器, 从而避免了制造高位转换器和高精度电阻网络的困难;另一方面,因为它采用了∑–△调制技术和数字抽取滤波,可以获得极高的分辨率;同时由于采用了低位量化输出的∑–△码,不会对抽样值幅度变化敏感,而且由于码位低,抽样与量化编码可以同时完成,几乎不花时间,因此不需要采样保持电路,这就使得采样系统的构成大为简化。这种增量调制型ADC实际上是以高速抽样率来换取高位量化,即以速度来换精度。

从调制编码理论的角度看,多数传统的ADC,例如并行比较,逐次逼近型等,均属于线性脉冲编码调制(LPCM,Linear Pulse Code Modulation)类型。这类ADC根据信号的幅度大小进行量化编码,一个分辨率位n的ADC其满刻度电平被分为2n个不同的量化等级,为了能区分这2n个不同的量化等级需要相当复杂的电阻(或电容)网络和高精度的模拟电子器件。当位数n较高时,比较网络的实现是比较困难的,因而限制了转换器分辨率的提高。同时,由于高精度的模似电子器件受集成度,温度变比等因素的影响,进一步限制了转换器分辨率的提高。

∑–△型ADC与传统的LPCM型ADC不同,它不是直接根据信号的幅度进行量化编码,而是根据前一采样值与后一采样值之差(即所谓增量)进量化编码,从某种意义上来说它是根据信号的包络形状进行量化编码的。从这一点上看,它与跟踪计数型ADC有一点类似。

△表示增量,∑表示积分或求和。在下面可以看到,∑–△型ADC采用了极低位的量化器(通常是1位),从而避免了LPCM型ADC在制造时面临的很多困难,非常适合用MOS技术实现。另一方面,又因为它采用了极高的采样速率和∑–△调制技术,可以获得极高的分辨率。同时,由于它采用低位量化,不会像LPCM型ADC那样对输入信号的幅度变化过于敏感。

与传统LPCM型ADC相比,∑–△型ADC实际上是一种用高采样速率来换取高位量化,即以速率换分辨率的方案。

过采样(Oversampling)技术是改善模数转换器总体性能诸多技术中的一种。∑—△结构的ADC是一种内在的过采样转换器。∑—△型ADC以很低的采样分辨率(1位)和很高的采样速率将模拟信号数字化,通过使用过采样技术,噪声整形和数字滤波技术增加有效分辨率,然后对ADC输出进行抽取(Decimation)处理,以降低ADC的有效采样速率,去除多余信息,减轻数据处理的负担。由于∑—△型ADC所使用的1位量化器(即1位比较器)和1位数模转换器(为一开关)具有良好的线性,所以∑—△型ADC表现出的微分线性和积分线性性能是非常优秀的,并且,不像其它类型的ADC那样,它无需任何的修调。

3. 一阶∑–△型ADC的基本原理

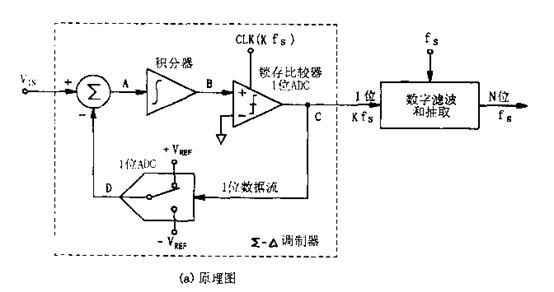

要了解∑—△型ADC的工作原理,必须熟悉过采样,噪声整形,数字滤波和采样抽取等几个基本概念。下图是一阶∑—△型ADC含有非常简单的模拟电路(一个比较器,一个开关,一个或几个积分器及模拟求和电路)和十分复杂的数字信号处理电路。

一阶∑—△型ADC

Σ-Δ转换器具有相对简单的结构,又称为过采样转换器。这种转换器由Σ-Δ调制器(虚线框内)及连接于其后的数字滤波器构成。调制器的结构非常近似于双斜率ADC,包括一个积分器和一个比较器,以及含有一个1位ADC的反馈环。这个内置的DAC仅仅是一个开关,它将积分器输入切换到一个正或负的参考电压。Σ-ΔADC还包括一个时钟单元,为调制器和数字滤波器提供适当的定时。

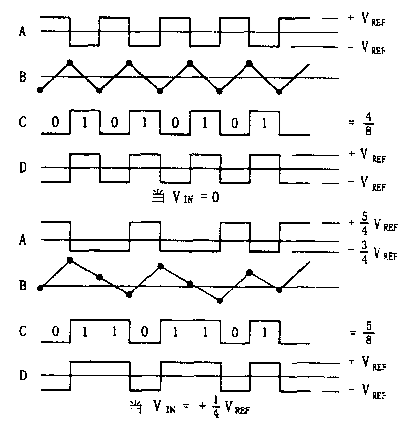

下图是输入Vin=0和Vin=+Vref/4两种情况下,电路中各点的电压波形示意图。可以看出两种情况下,C点输出的码流中"0"和"1"的个数是不一样的。

波形图

窄带信号送入Σ-ΔADC后被以非常低的分辨率(1位)进行量化,但采样频率却非常高,如2MHz或更高。经过数字滤波处理后,这种过采样被降低到一个比较低的采样率,如8KHz左右,同时ADC的分辨率(即动态范围)被提高到16位或更高,尽管比流水线ADC要慢且限于比较低的输入带宽,这种Σ-Δ技术在模数转换器市场上仍占据了很重要的位置。它具有三个主要优势:

低价格、高性能(最高可到24位)

集成化的数字滤波

与DSP技术的兼容性便于实现系统集成

主要应用在:音频和测量

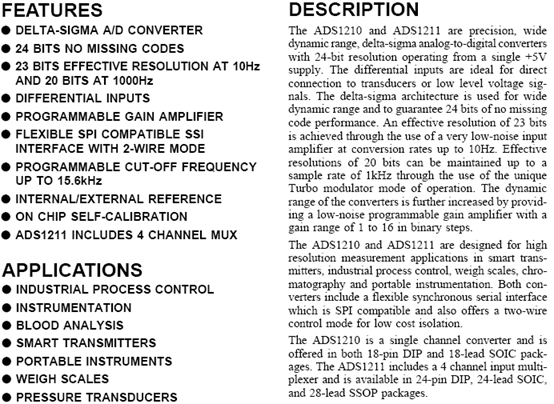

芯片实例:ADS1210系列:24位A/D转换器。Burr-Brown公司

近年来,采用高分辨率的Σ-Δ型ADC颇为流行,它的一个突出优点是在一片混合信号CMOS大规模集成电路上实现了ADC与数字信号处理技术的结合。这一技术的其它优点:分辨率高达24位;比积分型及压频变换型ADC的转换速率高; 采用混合信号CMOS工艺,可实现低价格、高分辨率的数据采集和数字信号处理;由于采用高倍频过采样技术,降低了对传感器信号进行滤波的要求,实际上取消了信号调理。缺点:当高速转换时,需要高阶调制器;在转换速率相同的条件下,比积分型和逐次逼近型ADC的功耗高。

目前,Σ-Δ型ADC分为四类:(1)高速类ADC;(2)调制解调器类ADC;(3)编码器类ADC;(4)传感器低频测量ADC。其中每一类Σ-Δ型ADC又分为许多型号,给用户带来极大方便。