时序路径 Timing Paths

时序分析工具寻找并检查设计中所有的时序路径,每个路径有一个起始点和一个终止点。起始点是在设计中数据被时钟沿触发的端点。数据在路径中上经过组合逻辑传播,并在终止点上被另一个时钟沿捕获。

The timing analysis tool finds and analyzes all of the timing paths in the design. Each path has a startpoint and an endpoint. The startpoint is a place in the design where data is launched by a clock edge. The data is propagated through combinational logic in the path and then captured at the endpoint by another clock edge.

路径的起始点一般是时序器件的时钟引脚或者设计的输入的端口。有效时钟边沿到达起始点时,将会在路径中触发数据。由于一个输入端口的数据的到达是由外部源触发,输入端口可以被视为起始点

The startpoint of a path is a clock pin of a sequential element or an input port of the design.The arrival of an active clock edge at a startpoint launches data through the path. An input port can be considered a startpoint due to the arrival of data launched by an external source.

路径的终止点一般是时序器件的数据输入引脚或者设计的输出端口。有效时钟边沿到达捕获器件的时钟输入端口时,将捕获在路径末端的数据。由于外部捕获了离开输出端口的数据,输出端口可以被视为终点。

The endpoint of a path is a data input pin of a sequential element or an output port of the design. The arrival of an active clock edge at the clock input of the capture device captures data at the end of the path. An output port can be considered an endpoint due to the external capture of the data leaving the output port.

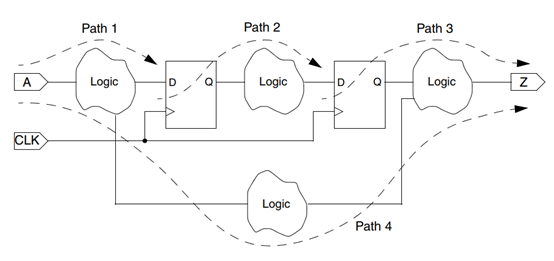

图1-7 时钟路径类型

Figure 1-7 Timing Path Types

图1-7 展示了一个设计和该设计的时钟路径的例子

Figure 1-7 shows an example of a design and its timing paths

每条路径开始于数据发射端,经过一些组合逻辑电路,结束于数据捕获端

Each path starts at a data launch point, passes through some combinational logic, and ends at a data capture point:

路径1开始于输入端口,结束于时序元件的数据输入端

路径2开始于时序元件的时钟引脚,结束于时序元件输入端

路径3开始于时序元件的时钟引脚,结束于输出端口

路径4开始于输入端口,结束于输出端口

• Path 1 starts at an input port and ends at the data input of a sequential element.

• Path 2 starts at the clock pin of a sequential element and ends at the data input of a

sequential element.

• Path 3 starts at the clock pin of a sequential element and ends at an output port.

• Path 4 starts at an input port and ends at an output port.

设计中的每条路径都有一个相关的时序裕量。这个裕量是一个可正可负可为零的时间值。

拥有最差裕量的单一路径称为关键路径。这条路径要么拥有最负的时间裕量,要么在没有时序违例时,会成为设计中所有路径中最小的时序裕量路径。关键路径中的路径的复数表示,代表着设计中所有路径中裕量最差的n条路径的集合。

Each path in the design has an associated timing slack. The slack is a time value that can be positive, zero, or negative. The single path having the worst slack is called the critical path. This is the path that has the most negative slack, or if there are no timing violations, the one with the smallest slack among all paths in the design. The plural term, critical paths, means the set of n paths having the worst slack among all paths in the design.

您可以选择将设计的路径划分为组,以便为指定的路径组分别进行时间分析、报告和优化。例如,您可以将input-to-register、register-to-register和register-to-output路径分成三个单独的组,因为它们有不同类型的时间约束。默认情况下,设计中使用的每个时钟都有一个路径组。

You can optionally divide the paths of a design into groups so that timing analysis, reporting,and optimization are done separately for the designated path groups. For example, you might put the input-to-register, register-to-register, and register-to-output paths into three separate groups because they have different types of timing constraints. By default, there is one path group for each clock used in the design.

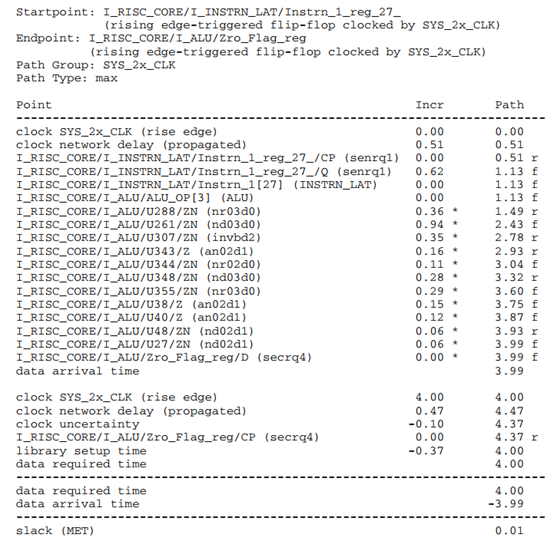

下面是IC编译器中由report_timing命令生成的典型路径定时报告。在DC或PT中使用report_timing命令生成类似的报告。

The following is a typical path timing report generated by the report_timing command in

IC Compiler. A similar report is produced by the report_timing command in Design

Compiler or PrimeTime.

默认情况下,report_timing命令将会报告每个路径组下最差的建立时间路径

By default, the report_timing command reports the worst setup path in each path group.

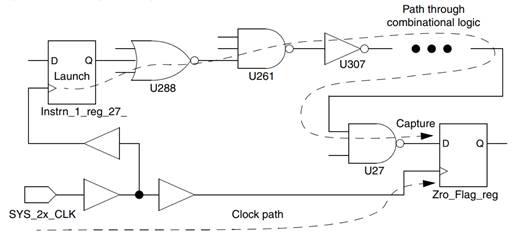

在这个例子中,与报告的路径相关联的逻辑电路如图1-8所示

In this example, the logic associated with the reported path is shown in Figure 1-8.

Figure 1-8 Timing Path Logic

在报告的开头处,显示了路径的起始点,路径的结束点,路径分组的名字以及路径时序检查的类型。在这个例子中,路径检查的类型显示为max,这代表着最大延迟检查或者建立时间检查,如果为min,那代表着最小延迟检查或者保持时间检查。

The report starts by showing the path startpoint, path endpoint, path group name, and path timing check type. In this example, the path timing check type is shown as "max," which means a maximum-delay or setup check; "min" would mean a minimum-delay or hold check.

一个很大的表格显示了从起点到终点的路径上逐点计算的延迟。该表有标记为Point、Incr和Path的列。这些列分别列出路径上的点(单元的引脚)、每个点对延迟的增量贡献以及到该点的累计延迟。分层边界交叉点也被列出,在每个交叉点显示零增量延迟。

A large table shows point-by-point accounting of the delays along the path from the

startpoint to the endpoint. The table has columns labeled Point, Incr, and Path. These

columns list the points (cell pins) along the path, the incremental contribution to the delay at

each point, and the cumulative delay up to that point, respectively. Hierarchical boundary

crossings are listed as well, showing zero incremental delay at each crossing.

星号(*)符号在增加列表明SDF反标注延迟值被用于网络延迟。路径列中的字母"r"和"f"表示信号转换的意义,在路径的那一点上升或是下降。路径从发射时钟边缘开始,并在捕获设备的数据输入端结束。

The asterisk (*) symbols in the Incr column indicate where SDF back-annotated delay values were used for the net delay. The letters "r" and "f" in the Path column indicate the sense of the signal transition, either rising or falling, at that point in the path. The path starts with the launch clock edge and ends at the data input of the capture device.

表中显示的"数据到达时间"是考虑到路径上最长的可能延迟之后,从发射时钟边缘的来源到数据到达端点所经过的时间,。

之后是所需到达时间的核算。

表中所示的"数据所需时间"是最新的容许数据路径端点的到达时间,该时间考虑到标称时钟上升沿捕获时间,时钟网络延迟,时钟的不确定性, 沿时钟路径的最小延迟以及时钟路径和捕获器件的库设置时间要求。

所需时间会因时钟再收敛悲观消除(CRPR)而调整。

The "data arrival time" shown in the table is the amount of elapsed time from the source of the launch clock edge to the arrival of data at the endpoint, taking into consideration the longest possible delays along the path.

After this is the accounting for the required arrival time.

The "data required time" shown in the table is the latest allowable arrival time for the data at the path endpoint, taking into account the nominal capture clock edge time, the clock network delay, the clock uncertainty,the least possible delay along the clock path, and the library setup time requirement for the capture device.

The required time is subject to adjustment for clock reconvergence pessimism removal (CRPR).

在报告的最后,显示的裕量值是所需的数据时间减去数据到达时间。时间裕量是考虑了数据最快可能到达终点的情况以及捕获时钟沿的最早到达的情况,且满足时序约束的时间量。

The slack value shown at the end of the report is simply the data required time minus the data arrival time. The slack is the amount of time by which the timing constraint is met,considering the latest possible arrival of data at the endpoint and the earliest possible arrival of the capture clock edge.

在该例中,时间是一个非常小的正值,这意味着刚刚满足了时序约束。一个负值的裕量会需要对设计进行修正以修复违例。例如,路径上的驱动单元可以被替换为一个更大的具有更高驱动能力的单元,这将会减少连线延迟。在另一方面,一个较大的正的时间裕量值提供了优化的机会。例如,路径上的驱动单元可以替换为更小的,更慢的单元来减少面积,或者更慢的,高阈值电压的单元来减少漏电流。

In this example, the slack is a very small positive value, which means that the timing

constraint is barely met. A negative slack would require a change in the design to fix the violation. For example, a driver in the path could be replaced with a larger cell with a higher drive strength, which would reduce the net delay. On the other hand, a large positive slack would offer opportunities for optimization. For example, drivers in the path could be replaced with slower, smaller cells to reduce the area or with slower, higher-threshold cells to reduce leakage power.