32位除法器verilog语言实现的原理

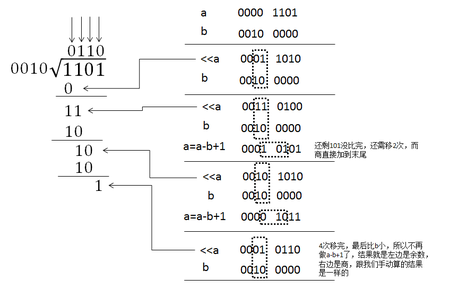

对于32位的无符号数除法,被除数a除以除数b,他们的商和余数一定不会超过32位,首先将a转换成高32位为0,低32位为a的temp_a,再将b转换成高32位为b,低32位为0的temp_b。在每个周期开始前,先将temp_a左移一位,末尾补0,然后与b相比较看是否大于b,若大于b,则temp_a=temp_a-temp_b+1,否则继续往下执行。上面的移位操作、比较和减法要执行32次,执行完成后得到的temp_a的高32位为两数a和b相除的余数,低32位表示商。具体的算法流程可从下图的例子中得到体现

用verilog代码实现如下:

module div32( input clk,rst_n, input start, input [31:0] a, input [31:0] b, output done, output [31:0] yshang, output [31:0] yyushu ); reg[63:0] temp_a; reg[63:0] temp_b; reg[5:0] i; reg done_r; //------------------------------------------------ always @(posedge clk or negedge rst_n)begin if(!rst_n) i <= 6'd0; else if(start && i < 6'd33) i <= i+1'b1; else i <= 6'd0; end //------------------------------------------------ always @(posedge clk or negedge rst_n) if(!rst_n) done_r <= 1'b0; else if(i == 6'd32) done_r <= 1'b1; else if(i == 6'd33) done_r <= 1'b0; assign done = done_r; //------------------------------------------------ always @ (posedge clk or negedge rst_n)begin if(!rst_n) begin temp_a <= 64’h0; temp_b <= 64’h0; end else if(start) begin if(i == 6'd0) begin temp_a = {32'h00000000,tempa}; temp_b = {tempb,32'h00000000}; end else begin temp_a = temp_a << 1; if(temp_a >= temp_b) temp_a = temp_a - temp_b + 1'b1; else temp_a = temp_a; end end end assign yshang = temp_a[31:0]; assign yyushu = temp_a[63:32]; endmodule