从RTL到最终的GDS版图,大致需要经过什么阶段.

RTL +SDC(性能需求),经过后端,完成版图。 版图要保证 功能、性能、要符合fab厂的物理规则(走线、宽度等)。

逻辑综合

目的: 把RTL代码,转换成工艺库的门电路,如0.11m, 55nm库.

步骤: (1) 翻译成逻辑表达式。(2) Optimize 优化表达式 ,并映射成工艺库的门。 迭代优化、映射。

延迟估算: 因为门电路,导线、寄生电容,通过这些,都需要耗掉一丢丢的时间,dc需要根据自己所优化的门级网表进行预估。

估计每个路径上,等效电阻多大、寄生电容多大、门电路的物理延迟多大,得出整个估值。

RTL 读入DC工具,完成第一步翻译的工作. 这一步的记过可以输出出来。gtech.v

然后,根据target_library,即目标工艺库。配合sdc约束文件,完成第二步 优化映射。产生netlist网表文件、

结果可以输出: mapped.v 和report报告。

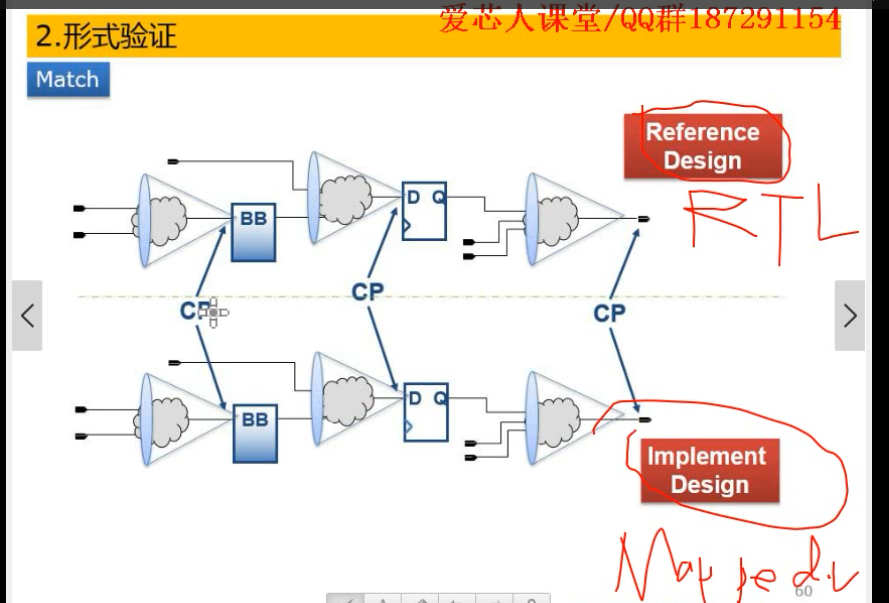

形式验证

综合之后,因为有翻译迭代优化映射的过程,怎么确保前后功能是一致的? Formality就是进行对比RTL和Netlist的。

基本原理 : 引入比较点、逻辑锥。 把寄存器、input、black_box之间的组合逻辑,化成一个整体。

然后去比较对应的逻辑锥是否功能一样. 具体怎么比?

把逻辑锥的所有input信号,0101进行遍历操作,然后比较两个比较点输出是否一样,通过为pass,失败为fail。

整体上,形式验证如下图:

得到了映射的工艺库,后面需要做的是物理实现.即把映射网标文件,转为工艺厂能生产使用的gds文件,

这一个过程,后面再做补充. 目前学些的重点是 DC,以及FM。详细的学习第一个阶段所涉及的知识.