S02_CH04_User_IP实验

4.1 创建IP

在之前的教程中,我们通过MIO与EMIO来控制LED,所使用的也是官方的IP,实际当中,官方提供的IP不可能涵盖到方方面面,用户需要自己编写硬件描述语言,然后将其封装成IP来使用,本节就将详细的讲解如何在VIVADO中创建用户自定义的IP。

Step1:打开VIVADO软件,新建一个工程。

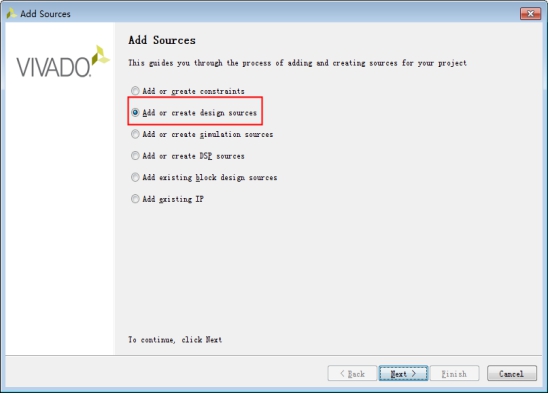

Step2:单击Add Source,选择Add or Creat design Sources,然后单击Next。

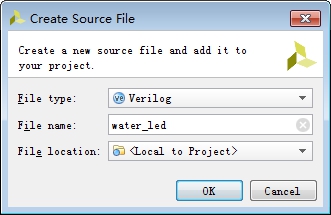

Step3:单击Create File,输入文件名,单击OK。

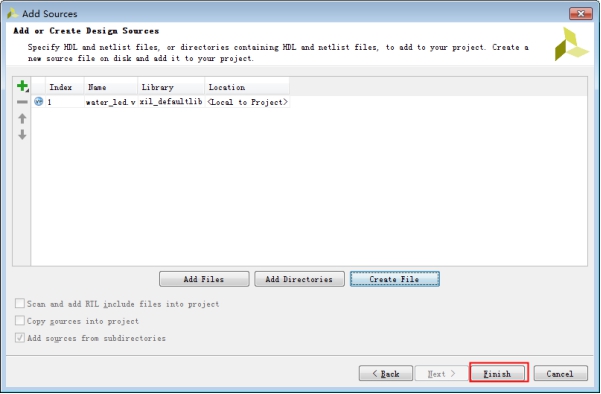

Step4:单击Finish,完成Verilog文件的创建。

Step5:将以下代码复制入文本编辑区内。

| module LED_ML( input CLK_i,//100MHZ input RSTn_i, output reg [3:0]LED_o ); reg [31:0]C0; always @(posedge CLK_i) if(!RSTn_i) begin LED_o <= 4'b0001; C0 <= 32'h0; end else begin if(C0 == 32'd49_999_999)//1s begin C0 <= 32'h0; if(LED_o == 4'b1000) LED_o <= 4'b0001; else LED_o <= LED_o << 1; end else begin C0 <= C0 + 1'b1; LED_o <= LED_o; end end endmodule |

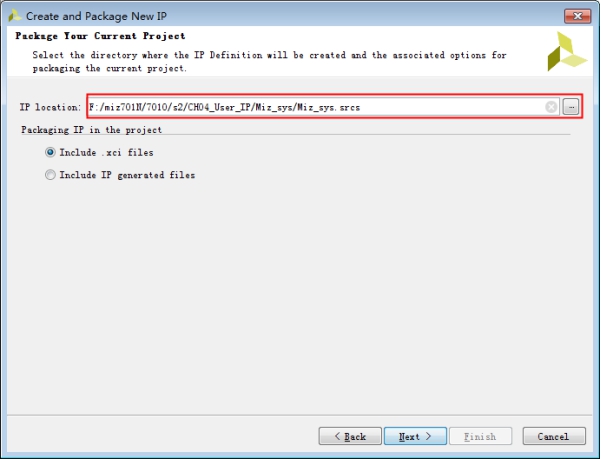

Step6:单击Tools—>Create and package IP,单击Next。

Step7:选择IP的保存路径,单击Next。

Step8:单击Finish完成封装。

4.2 调用自定义IP

Step1:另外新建一个VIVADO工程,根据自己的开发板正确配置芯片型号。

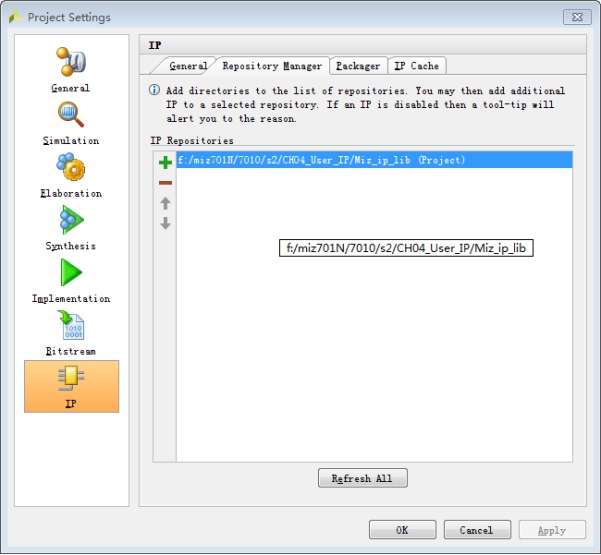

Step2:在Project manager区中单击Project settings。

Step3:选择IP设置区中的repository manager,。

Step:4:单击+号图标,将上一节封装的IP的路劲存放进去,单击OK。

Step5:新建一个BD文件,输入文件名,完成创建。

Step6:向BD文件中添加一个ZYNQ Processing system,根据自身硬件完成IP的配置。

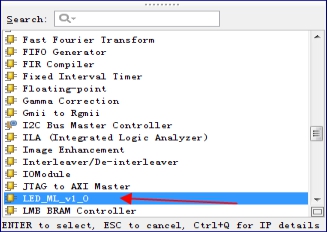

Step7:单击添加IP图标,输入上一节我们自定义IP的模块名,将其添加入BD文件中。

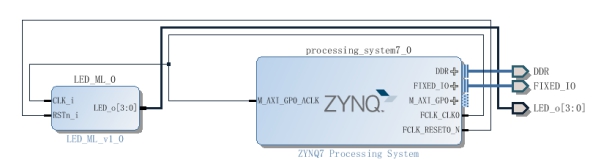

Step8:按如下电路图完成模块间的连线。

Step9:右键单击Block文件,文件选择Generate the Output Products。

Step10:右键单击Block文件,选择Create a HDL wrapper,根据Block文件内容产生一个HDL 的顶层文件,并选择让vivado自动完成。

Step11:选中Project manager,然后右单击Constraints,选择Add Sources。

Step12:输入文件名,完成创建,将上一章EMIO的约束文件copy进去。

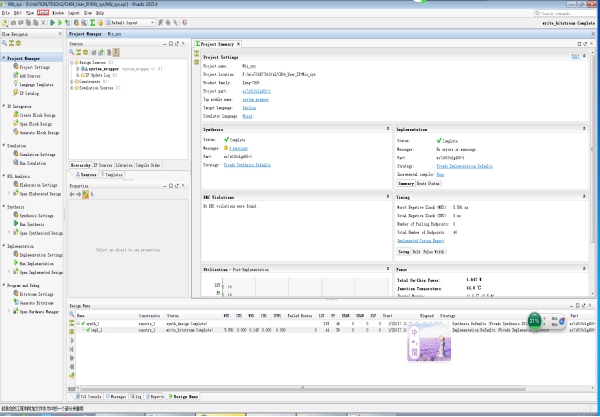

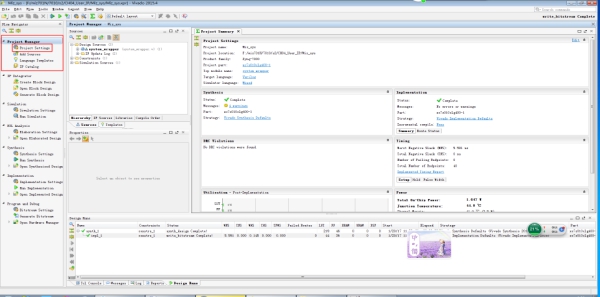

Step11:产生bit文件。

4.3 导入到SDK

由于自定义的IP的时钟输入来自于ZYNQ Processing system,源时钟是使用的PS的时钟,因此需要启动SDK整个系统才能启动,而自定义IP不需要由SDK进行配置,因此我们可以按照前几节讲过的内容,在SDK端建立一个Hello World工程跑起来就能让自定义IP跑起来。

Step1:创建一个Hello World工程。

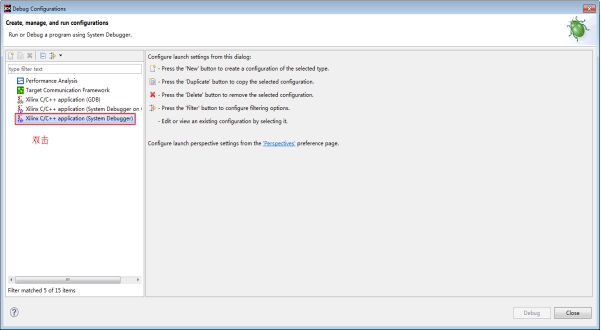

Step2:右击工程,选择Debug as ->Debug configuration。

Step3:选中system Debugger,双击创建一个系统调试。

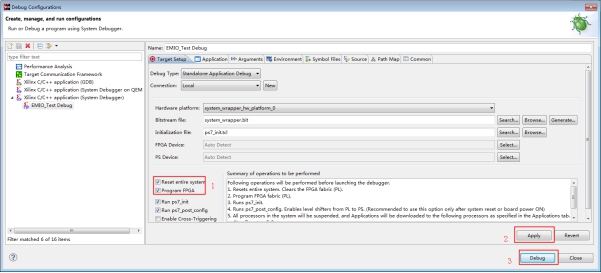

Step7:设置系统调试。

Step8:单击窗口上的运行按钮,运行程序,可看到LED的流水操作。

4.4 本章小结

本章主要介绍了如下在VIVADO下创建一个自定义的IP,内容比较简单,需要注意的是如果工程中使用的源时钟是为PS时钟的话,是需要启动SDK系统才能正常工作的,若是系统使用到了ZYNQ Processing System,则系统使用的是PS时钟,这是一个判断的依据。在ZYNQ的开发中,创建自定义IP是一项基本功,还未熟练掌握的要勤加练习。