原帖地址:https://blog.csdn.net/moon9999/article/details/75283926

在Linux下对verilogHDL进行功能仿真时非常必要的,下面提供两种常见方式:

1.命令行方式

1)新建文件夹vcs_test,将所有的工程文件与tb文件复制入,testbench中可以没有在脚本文件中添加的函数,一般的tb文件就可以。

本例子中有三个文件:

clk_half.v, //对clk信号进行分频。

module clk_half(

clk_in

,rst

,clk_out

);

input clk_in;

input rst;

output reg clk_out;

always @(posedge clk_in or posedge rst) begin

if (rst) begin

// reset

clk_out <= 0;

end

else begin

clk_out <= !clk_out;

end

end

endmodule

counter.v //简单的4位计数器。

module counter ( out, clk, reset ) ; input clk, reset; output [3:0] out; reg [3:0] out; always @(posedge clk or posedge reset) begin if (reset) begin // reset out <= 4'b0; end else begin out <= out + 1'b1; end end wire clk_out; clk_half u0( .clk_in(clk), .rst(reset), .clk_out(clk_out) ); endmodule

counter_tb.v //testbench文件

`timescale 1ns/1ns module counter_tb () ; wire [3:0] out; reg clk=1'b0; reg reset; counter u0 ( .out (out), .reset (reset), .clk (clk) ); always #10 clk =~ clk; initial begin reset = 1'b0; #4 reset = 1'b1; #4 reset = 1'b0; end initial begin $dumpfile("counter.vcd"); $dumpvars(0,u0); end initial #1000 $finish; endmodule

2)运行vcs

在终端中输入

vcs -V -R counter_tb.v counter.v clk_half.v -o simv -gui -debug_pp

-V:Verbose模式,打印vcs在运行的过程中执行的C Compiler汇编器和链接器的指令

-R:这个指令是告诉VCS在编译完成以后直接运行可执行文件,如果你在编译的时候没有带上这个选项,编译完成以后VCS就退出了,但是你会发现在相应的目录下产生了以各可执行文件,默认叫simv-o:

-o:给后面的simv文件改名字,如改成counter.simv

-gui:调用VCS的图形化界面

-debug_pp:看波形必须要在debug模式下

其他一些指令

-q:退出模式;抑制了例如VCS使用的C编译器/VCS分析源文件、top层、制定的timescale的信息。

-notice:使能更详细的诊断信息。

-pvalue+parameter_hierarchical_name=value:这个选项是用来改变源文件中parameter参数值的命令。 例如:-pvalue+udut.uchip.ucore. IDLE =0

-full64:这个选项是为64位的操作系统准备的

-l filename:制定一个VCS产生的log文件名,如果你键入了-R选项,那么在编译和仿真的时候都会将log内容打印到log文件中

2)观察波形

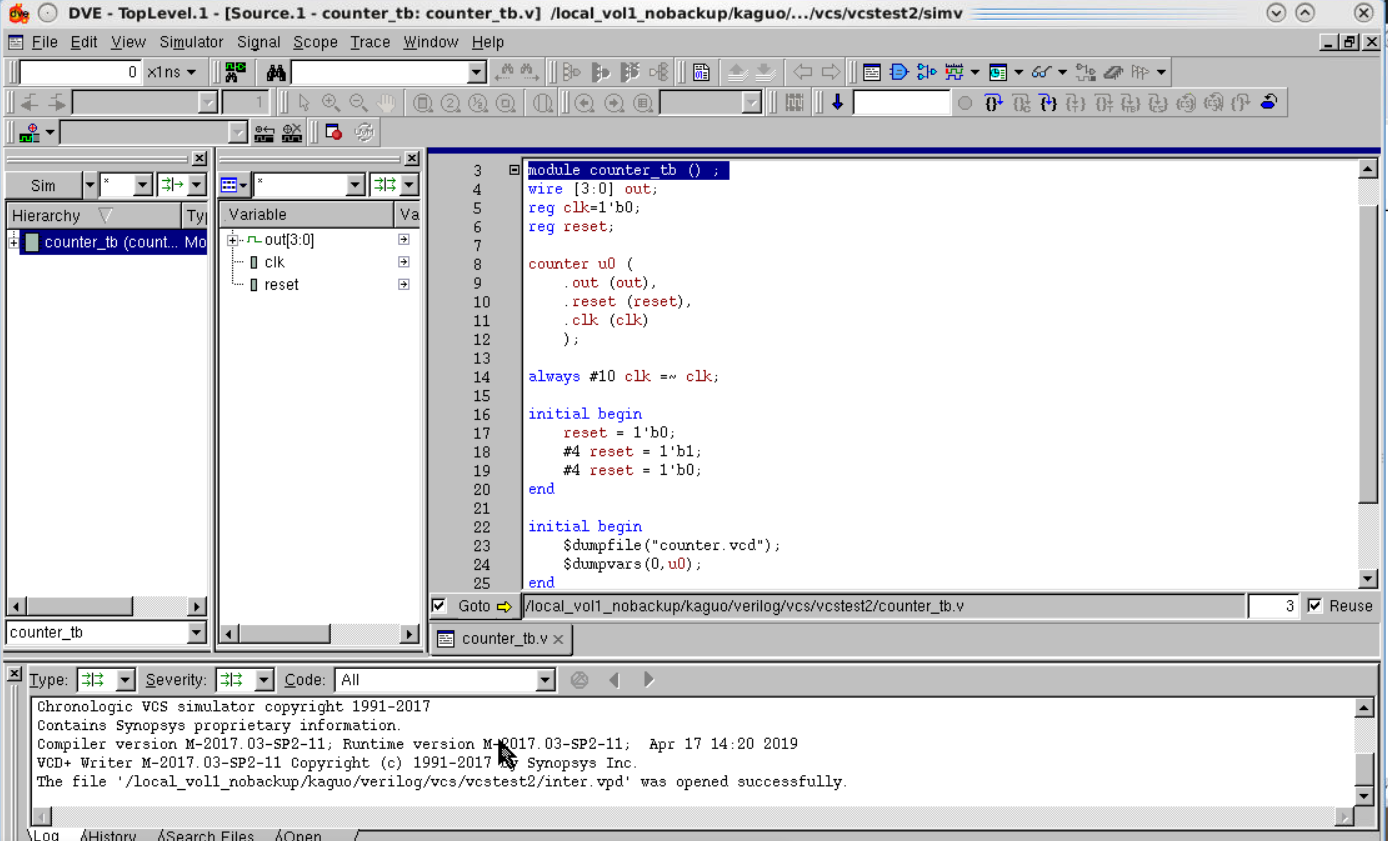

执行上面的vcs命令或者再次输入simv,就会打开dve窗口。如下图所示:

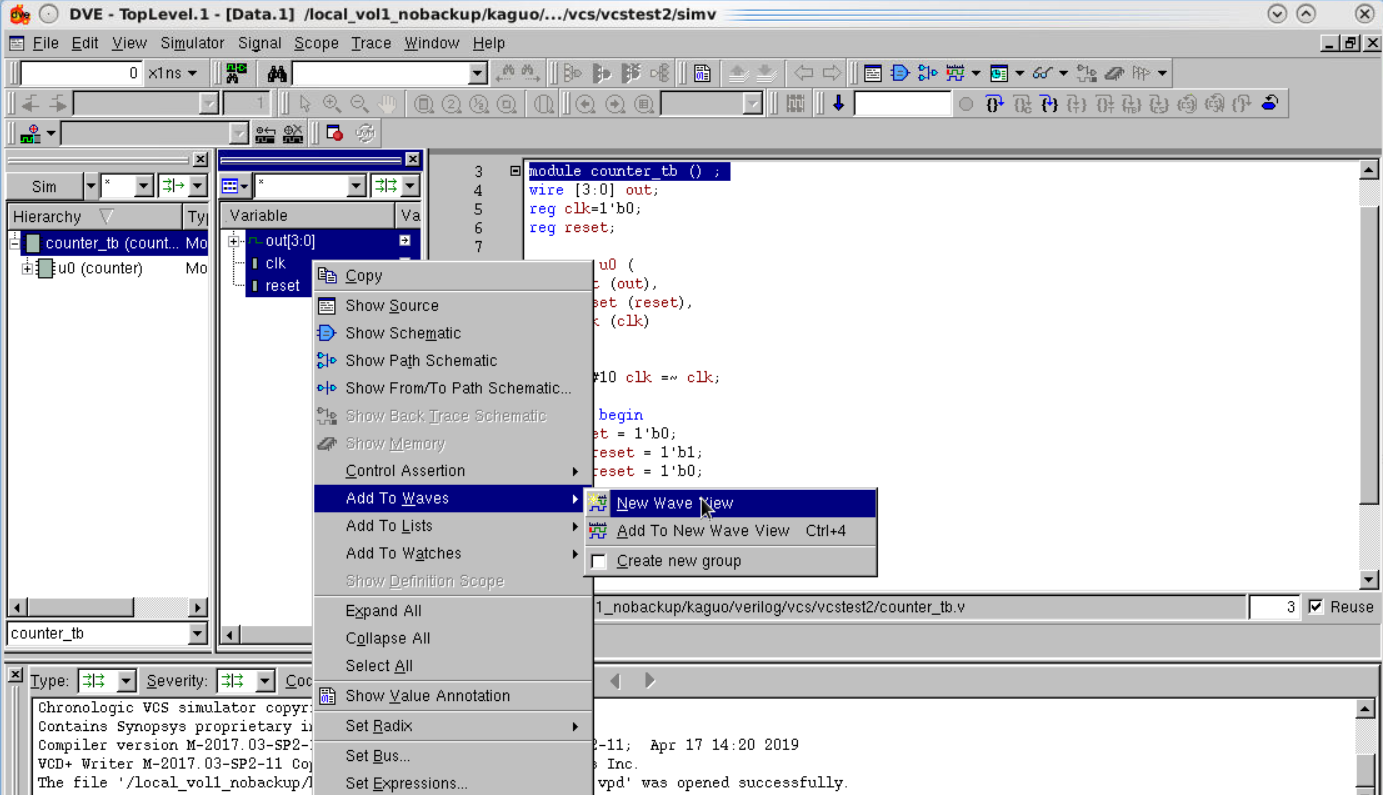

选取信号,点击菜单add to waves->new wave view

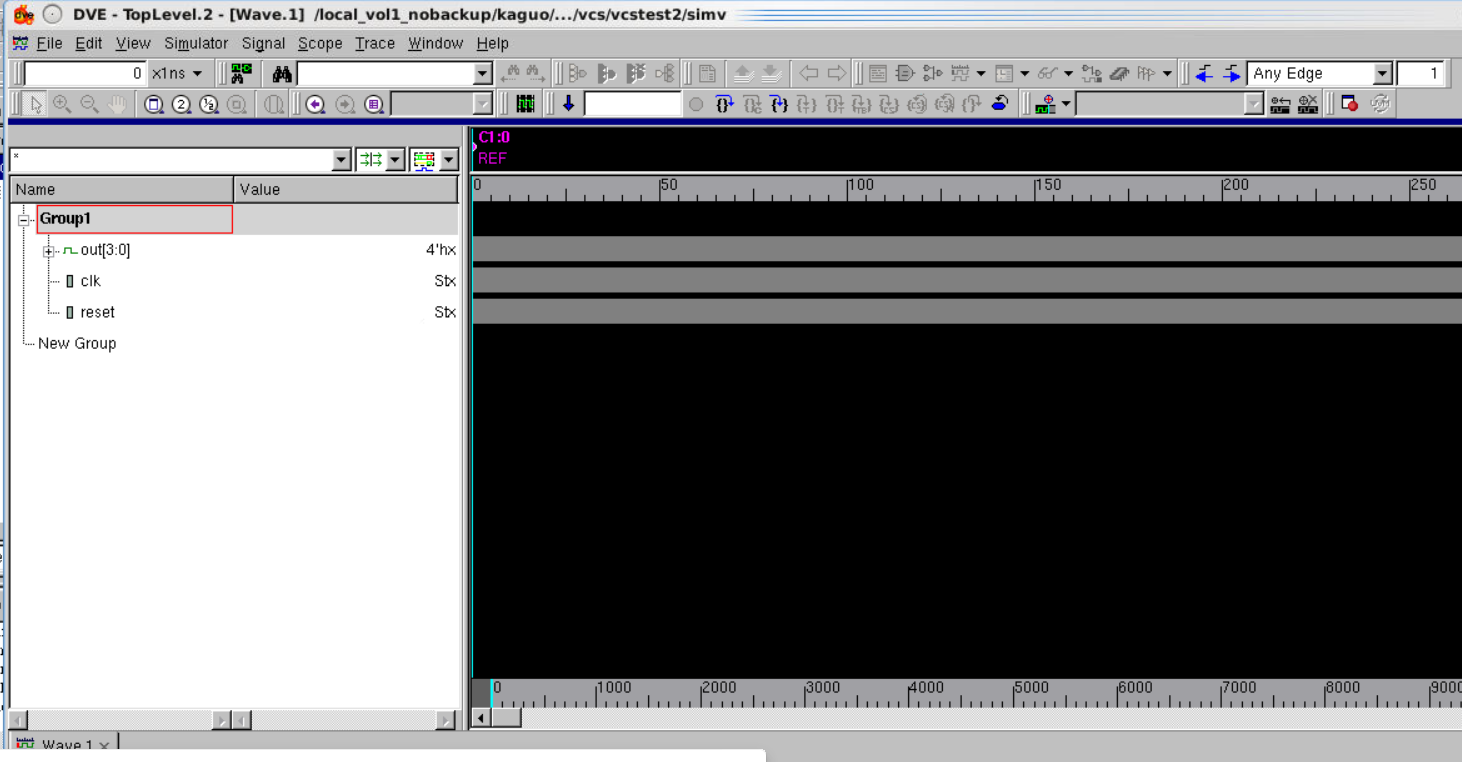

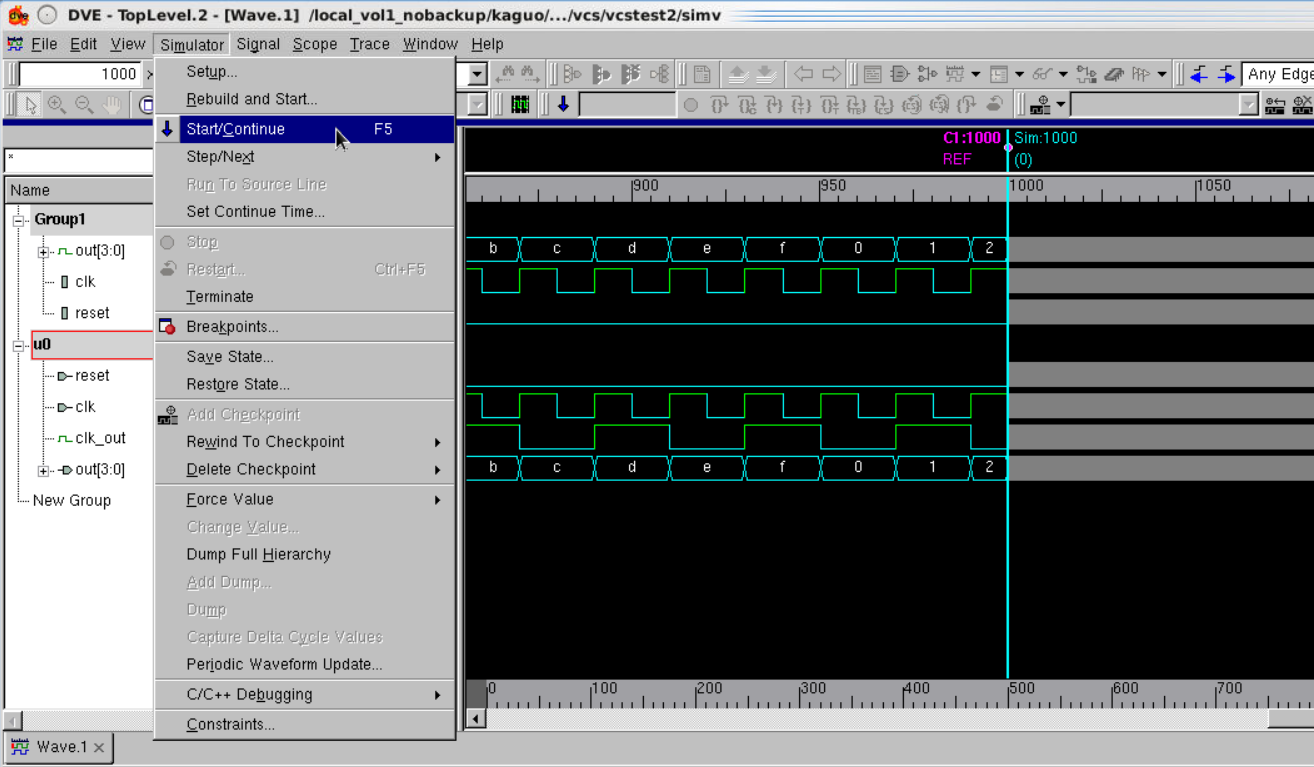

现在可以用鼠标中键拖动信号到这个窗口,观察波形,或者把信号拖到代码窗口,找到对应代码。点解start菜单,可以进行可以看到信号。

2.脚本方式

vcs -R counter_tb.v counter.v clk_half.v +v2k +define+RTL_SAIF

+v2k: verilog 2000 ieee

+define+RTL_SAIF : define macro RTL_SAIF

其中counter_tb.v为testbench文件,counter.v、clk_half.v为工程文件,注意要把所有的工程.v文件都添加进去

保存文件

4)在终端运行vcs.scr脚本文件

在终端中输入

source vcs.scr

程序编译执行完后,打开dve,然后选择vcd波形文件,查看波形,也可以用verdi查看波形。