I2S简介

如上图所示:

- SCLK :位时钟,数据单bit反转。 频率=2 * 采样频率 * 采样位宽

- LRCK :帧时钟,左右声道标志位。 频率=采样频率

- SDATA :串行音频数据BIT位。图中表示音频数据为8bit,即采样位宽=8

- sdata在sclk的下降沿变化,上升沿采集。且在lrck发生反转后的第二个上升沿采集音频数据的最高位。音频数据的最低位是lrck再次反转的第一个上升沿。

I2S详介

I2S音频总线协议

功能简介

将音频数据经过存储后,进行并传串处理,按照I2S协议输出。

模块端口

接口描述

| signal_name | direction | width | description |

|---|---|---|---|

| i_clk | input | 1 | FPGA内部系统时钟 |

| i_rst_n | input | 1 | 异步复位,低电平有效 |

| i_dsp_clk | input | 1 | 由DSP给出,用于分频出 sclk 和 lrck |

| i_aud_left_data | input | SAMP_BITS | 左声道的音频数据 |

| i_aud_right_data | input | SAMP_BITS | 右声道的音频数据 |

| i_aud_en | input | 1 | 音频样本有效标志 |

| o_aud_sclk | output | 1 | I2S位时钟 |

| o_aud_lrck | output | 1 | I2S帧时钟 |

| o_aud_sdata | output | 1 | I2S串行音频数据 |

| o_rd_req | output | 1 | 向上级模块发出音频数据请求,若上级模块无存储则忽略该信号 |

参数定义

| Paramter | description |

|---|---|

| DIV_SCLK_DEPTH | sclk 是 i_dsp_clk 的 2^N 分频,取值 N |

| DIV_LRCK_DEPTH | lrck 是 sclk 的 2^M 分频,取值 M |

| SAMP_BITS | 左 (右)音频的采样位宽 |

| FIFO_DEPTH | FIFO数据深度的位宽。如深度为256,则取值8 |

实现方案

- i_dsp_clk经过分频模块divdreq_clk分频出lrck和sclk。

- 将左右声道位拼接后写入FIFO中。

- 利用lrck上升沿读取FIFO数据,配合I2S时序移位输出。

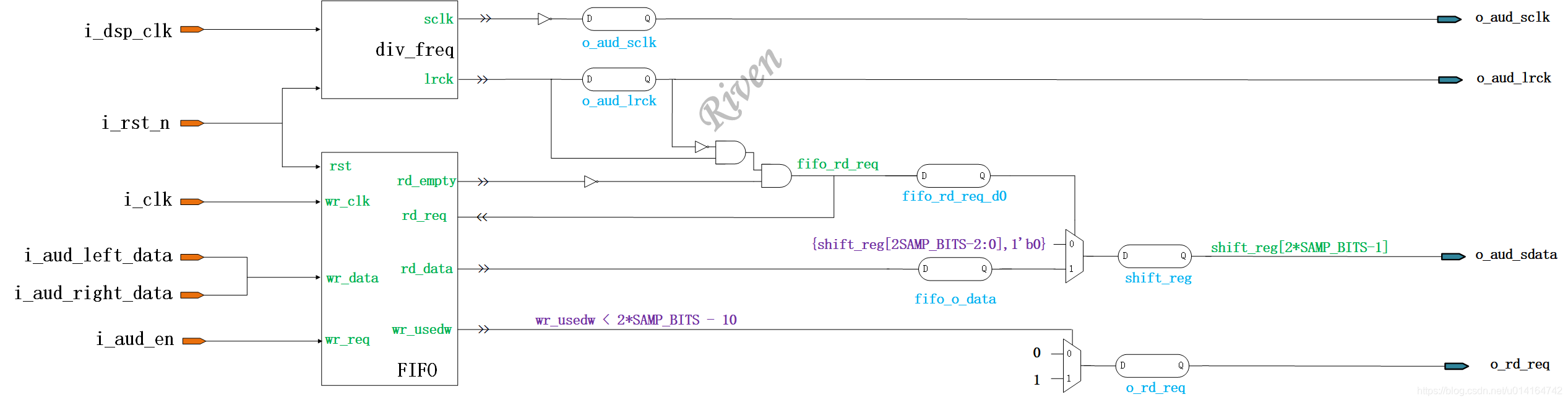

电路图描述

注:绿色为wire型,蓝色为reg型,紫色是逻辑计算

资源占用估计

| 资源 | 类型 | 个数 | 用途 |

|---|---|---|---|

| 寄存器 | 1bit | 3 | 信号延拍 |

| 寄存器 | 2*SAMP_BITS bit | 2 | 数据流 |

| FIFO | 深度:FIFO_DEPTH;位宽:2*SAMP_BITS | 1 | 跨时钟域变化 |

子模块(div_freq)

功能简介

- i_clk根据parameter进行2^N分频得到o_clk。(N为parameter)

- 根据i_rst_n进行异步复位同步释放处理得到与o_clk相匹配的o_rst_n。

接口描述

| signal_name | direction | width | description |

|---|---|---|---|

| i_clk | input | 1 | FPGA内部系统时钟 |

| i_rst_n | input | 1 | 异步复位,低电平有效 |

| o_clk | output | 1 | 分频得到的时钟 |

| o_rst_n | output | 1 | 分频得到的复位信号 |

参数定义

| Paramter | description |

|---|---|

| DIV_CNT_DEPTH | o_clk 是 i_clk 的2^X分频,取值为X |

代码实现

module div_freq

#(

parameter DIV_CNT_DEPTH = 2

)

(

input i_clk ,

input i_rst_n ,

output reg o_clk ,

output reg o_rst_n

)

//----------------------------- reg && wire -------------------------------

reg rst_n_temp_0 ;

reg rst_n_temp_1 ;

//-------------------------------- o_clk -----------------------------------

always @(posedge i_clk or negedge i_rst_n)

begin

if(!i_rst_n)

div_cnt <= { {DIV_CNT_DEPTH}{1'b0} } ;

else

div_cnt <= div_cnt + 1'b1;

end

always @(posedge i_clk)

o_clk <= div_cnt[DIV_CNT_DEPTH-1];

//-------------------------------- o_rst_n -----------------------------------

always @(posedge o_clk or negedge i_rst_n)

begin

if(!i_rst_n)

begin

rst_n_temp_0 <= 1'b0;

rst_n_temp_1 <= 1'b0;

o_rst_n <= 1'b0;

end

else

begin

rst_n_temp_0 <= 1'b1;

rst_n_temp_1 <= rst_n_temp_0;

o_rst_n <= rst_n_temp_1;

end

end

endmodule

资源占用估计

| 资源 | 类型 | 个数 | 用途 |

|---|---|---|---|

| 寄存器 | 1bit | 4 | 信号延拍 |

| 计数器 | DIV_CNT_DEPTH bit | 1 | 分频计数器 |

有问题联系可以我,一起讨论。