2017-2018-1 20155310 《信息安全系统设计基础》第七周学习总结

教材学习内容总结

ISA的定义

指令集体系结构(ISA)定义了处理器状态、指令的格式、以及每条指令对状态的影响。大多数ISA包括IA32和x84-64,将程序的行为描述成好像每条指令是按顺序执行的。

指令集体系统:一个处理器支持的指令和指令的字节级编码,每种不同的处理器都有自己不同的ISA

Y86指令集体系结构

定义一个指令集体系结构,包括定义各种状态元素,指令集和他们的编码、一组程序规范和异常处理。

•RF程序寄存器:%eax,%ecx,%edx,%ebx,%esi,%edi,%esp,%ebp(%esp被入栈、出栈、调用和返回指令作为栈指针)

•PC程序计数器:存放当前正在执行指令的地址

•DEME存储器:一个很大的字节数组,保存着程序和数据

•Stat程序状态:表明程序执行的总体状态

•CC条件码:ZF、SF、OF

4.3 Y86的顺序实现

•SEQ硬件结构

在SEQ中,所有硬件单元的处理都在一个时钟周期内完成。

SEQ线路图的画图惯例:

浅灰色方框表示硬件单元

控制逻辑块是用灰色圆角矩形表示的

线路的名字在白色椭圆中说明

宽度为字长的数据连接用中等粗度的线表示

宽度为字节或者更窄的数据连接用细线表示

单个位的连接用虚线表示

•SEQ的时序

SEQ的实现包括组合逻辑和两种存储器设备: 时钟寄存器、程序计数器和条件码寄存器

随机访问存储器 寄存器文件、指令存储器和数据存储器

每个时钟周期,程序计数器都会装在新的指令地址;只有在执行整数运算指令时,才会装载条件码寄存器;只有在执行rmmovl、pushl或call指令时,才会写数据存储器;寄存器文件的两个写端口允许每个时钟周期更新两个程序寄存器。

组织计算原则:处理器从来不需要为了完成一条指令的执行而去读由该指令更新了的状态。

用时钟来控制状态元素的更新,值通过组合逻辑传播。

•处理器设计的几个重要经验:

管理复杂性是首要问题,尽量保持硬件设计的简单。

不需要直接实现ISA。

•一开始就保证设计正确是非常重要的。

创建一个流水线化的Y86处理器的好开端。但是,将流水线技术引入一个带反馈的系统,当相邻指令同存在相关时会导致出现问题。

流水线控制逻辑必须处理以下4种控制情况,这些情况是其他机制(例如数据转发和分支预测)不能能处理的:

处理ret:流水线必须暂停直到ret指令到达写回阶段。

•加载/使用冒险:流水线必须暂停一个周期。

预测错误的分支:在分支逻辑发现不应该选择分支之前,分支目标处的几条指令已经进流水线了。必须从流水线中去掉这些指令。

•异常:当―条指令导致异常,我们想要禁止后面的指令更新程序员可见的状态,并睏异常指令到达写回阶段时,停止执行。

教材学习中的问题和解决过程

无

代码调试中的问题和解决过程

无

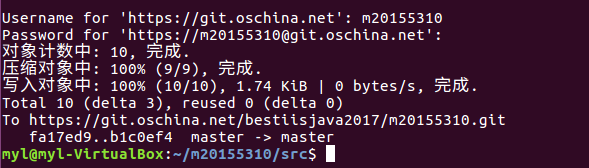

代码托管

上周考试错题总结

无

其他(感悟、思考等,可选)

无

学习进度条

| 代码行数(新增/累积) | 博客量(新增/累积) | 学习时间(新增/累积) | 重要成长 | |

|---|---|---|---|---|

| 目标 | 2000行 | 30篇 | 400小时 | |

| 第三周 | 15/300 | 3/7 | 3/60 | |

| 第四周 | 25/400 | 4/9 | 4/90 | |

| 第五周 | 25 /400 | 5/11 | 5/120 | |

| 第六周 | 45 /500 | 6/13 | 6/120 | |

| 第七周 | 65/600 | 7/15 | 7/130 |

尝试一下记录「计划学习时间」和「实际学习时间」,到期末看看能不能改进自己的计划能力。这个工作学习中很重要,也很有用。

耗时估计的公式

:Y=X+X/N ,Y=X-X/N,训练次数多了,X、Y就接近了。

-

计划学习时间:4小时

-

实际学习时间:1小时

-

改进情况:

(有空多看看现代软件工程 课件

软件工程师能力自我评价表)