配套FPGA开发板(含该设计的工程代码):https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-4676525296.4.6e8950ed57YPhv&id=17848039135

功能说明

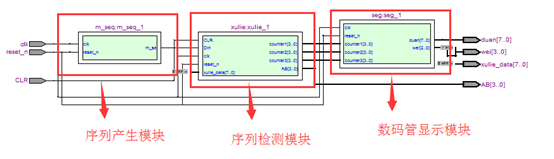

本设计主要分为3个模块:序列产生模块、序列检测模块、检测结果数码管显示模块。

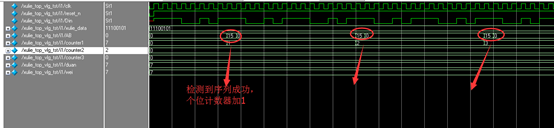

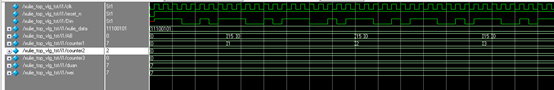

其中序列产生模块主要用来产生序列,用于仿真测试;序列检测模块用于对序列进行检测,本设计设计的检测序列的长度为8bit,当检测到一个对应的序列的时候,检测成功计数器会进行计数,该计数器能够计数的范围为0~999;检测结果数码管显示模块用于显示检测成功计数器的结果。

FPGA软件

下载链接: Quartus II 9.0 软件:http://pan.baidu.com/s/1jHSS0vG

仿真软件

ModelSimSEv6.2b

链接:http://pan.baidu.com/s/1o8lo0sU 密码:88wp

大西瓜-modelsim实用教程

链接:http://pan.baidu.com/s/1dFxJvuL 密码:v09a

原理

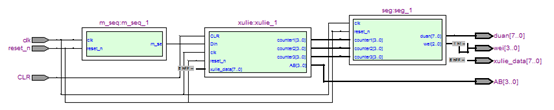

顶层原理图

本设计主要分为3个模块:序列产生模块、序列检测模块、检测结果数码管显示模块。

其中序列产生模块主要用来产生序列,用于仿真测试;序列检测模块用于对序列进行检测,本设计设计的检测序列的长度为8bit,当检测到一个对应的序列的时候,检测成功计数器会进行计数,该计数器能够计数的范围为0~999;检测结果数码管显示模块用于显示检测成功计数器的结果。

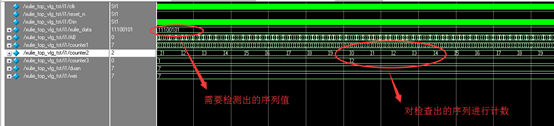

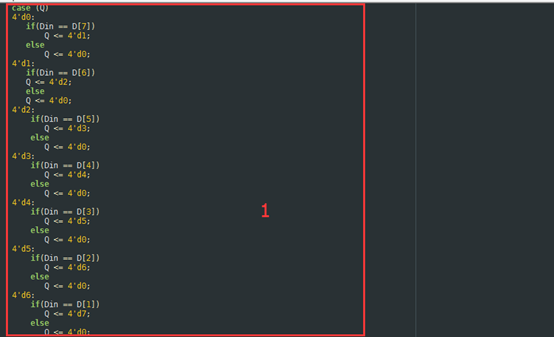

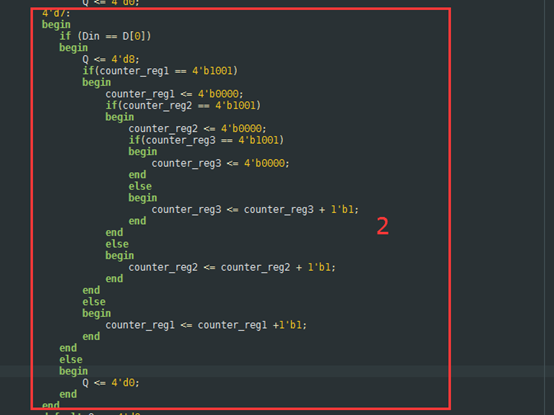

序列检测原理

1为一个一个位的检测

2为对检测正确的序列进行计数,计算正确的序列,然后用于显示在数码管

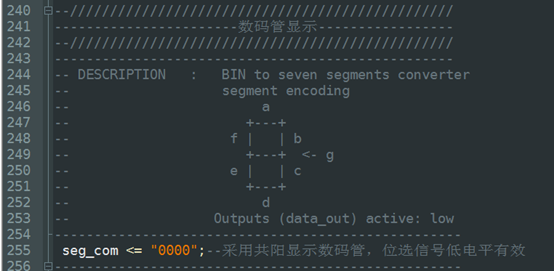

数码管显示原理

采用动态显示,动态显示原理:由于LED静态显示需要占用较多的I/O口,且功耗较大,因此在大多数场合通常不采用静态显示,而采用动态扫描的方法来控制LED数码管的显示。动态显示的特点是将8位数码管的段选线并联在一起,由位选线控制是哪一位数码管有效。点亮数码管采用动态扫描显示。

动态扫描显示原理:动态扫描显示即轮流向各位数码管送出字形码和相应的位选,只要扫描显示速度够快,利用发光管的余辉和人眼视觉暂留作用,使人的感觉好像各位数码管同时都在显示。动态显示的亮度比静态显示要差一些,所以在选择限流电阻时应略小于静态显示电路中的。动态扫描显示时刷新频率最好大于50HZ,即显示一轮的时间不超过20ms,本设计采用1000HZ的频率进行扫描显示,也就是数码管的刷新频率,每个数码管显示时间不能太长也不能太短,时间太长会影响刷新率,导致总体显示呈现闪烁的现象,时间太短发光二极管的电流导通时间也就短,会影响总体的显示亮度。一般控制在1ms左右最佳。

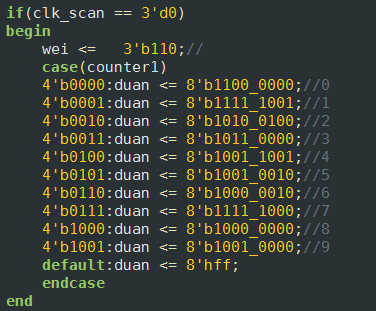

数码管显示原理

位选信号

本设计采用共阳数码管,即位选低电平有效,并且将位选信号设置为低电平;

段选信号

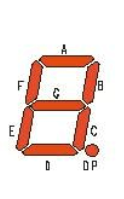

本设计采用共阳数码管,数码管的段选信号为8bit,数码管的段选对应实物图如下:

一个数码管有八段:A,B,C,D,E,F ,G,H,DP,即由八个发光二极管组成,; 因为发光二极管导通的方向是一定的(导通电压一般取为1.7V),这八个发光二极管的公共端有两种: +5V(即为共阳极数码管)、接地(即为共阴极数码管),其中共阳极每个段均有0导通,而共阴极则1导通发光,所以共阳极数码管和共阴极数码管显然是不同的,段选码表如下图所示:

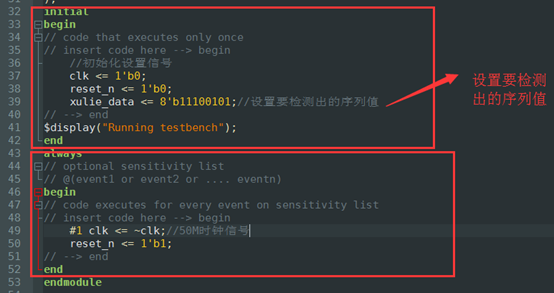

序列产生原理

该模块用于仿真测试,产生m序列信号。

红色框内为序列产生的代码,产生的序列为"11100101"

顶层模块

用于连接以上三个模块的信号,然后输出到引脚上。

仿真

仿真测试文件

仿真结果