配套FPGA开发板(含该设计的工程代码):https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-4676525296.4.6e8950ed57YPhv&id=17848039135

设计文件说明

-

顶层文件

文件名:DDS_top.v

该文件为工程的顶层文件,相当于C语言中的主函数,下面的文件相当C语言中的子函数。

在FPGA中,这个文件就是顶层电路。

DDS算法模块:

32位加法器:

10位加法器:

32位寄存器:

10位寄存器:

TLC5615驱动模块:

按键消抖模块:

按键编码模块:

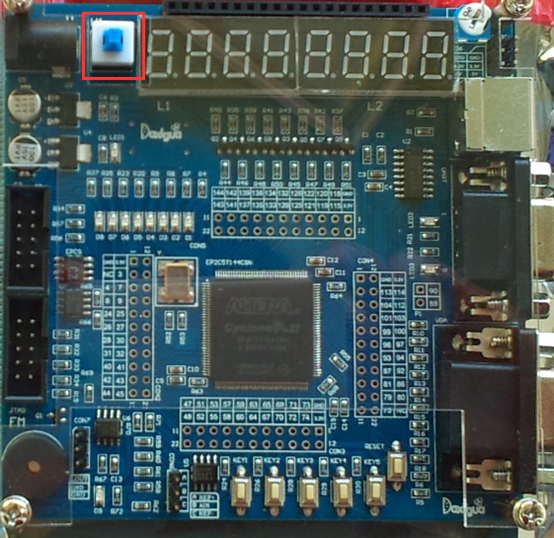

电路板

该设计中涉及到的硬件电路如下:

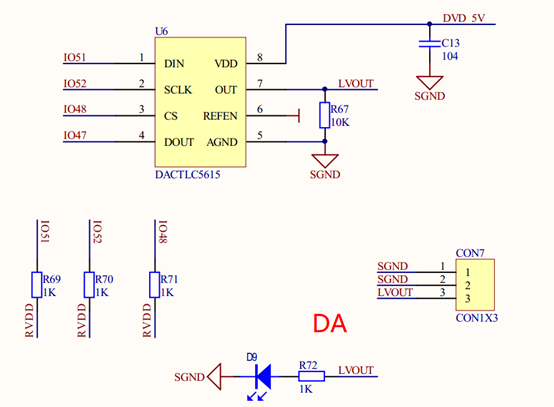

DAC电路

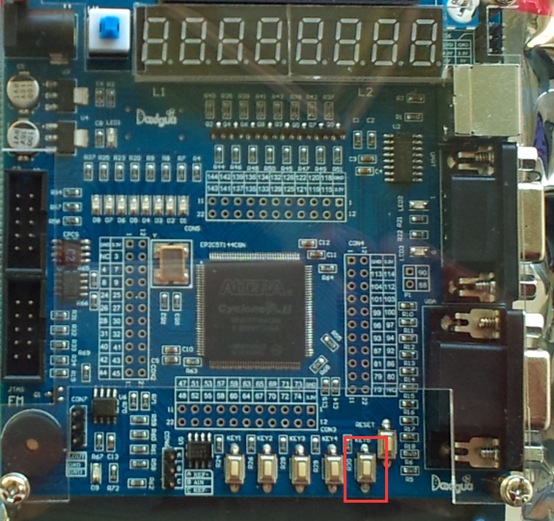

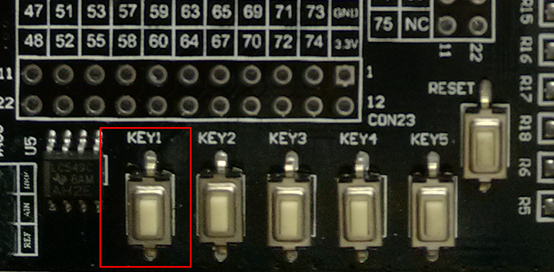

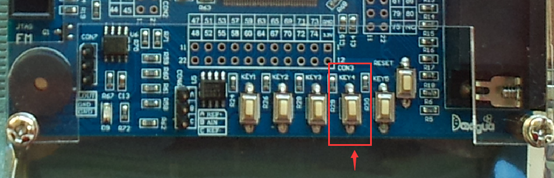

按键

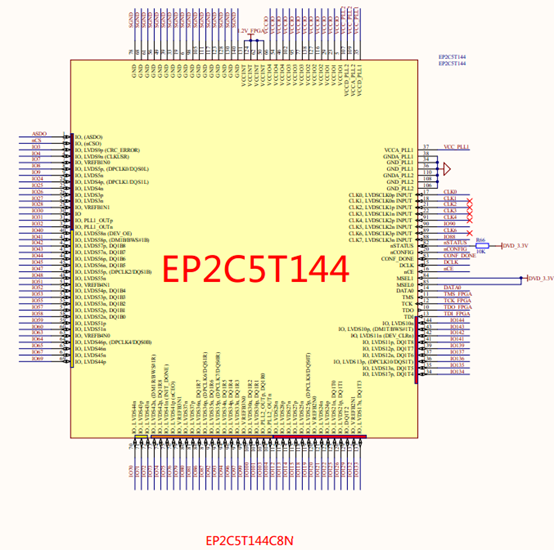

FPGA

电源

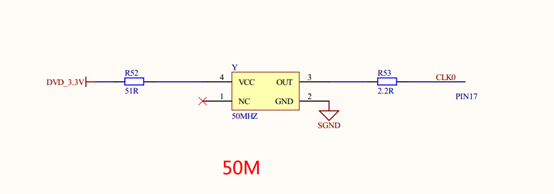

晶振

操作

上电

接入5V电源,用配套的线,USB那端接电脑即可;

电源开关

按下电源开关

复位

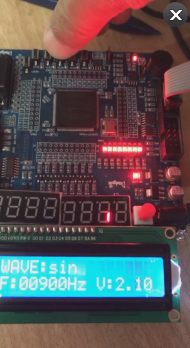

输出正弦波

DAC波形输出与示波器的接法

DAC芯片旁边插针为3个

图示接口接示波器!

谨防短路!

波形设置

一上电后,输出的波形默认为正弦波,每按下一次按键,输出的波形就会切换到另外一种波形。

频率设置

初始频率设置为100Hz,每按一次按键增加100HZ。设置范围为100Hz到25KHz。

幅值设置

初始幅值设置为最大值的十分之一,每按一次按键增加十分之一。设置到最大之后又再按一次,又会变为最小。

复位操作

复位按键,按下,有回到刚上电的状态。

显示

第一行显示波形;

第二行显示频率和有效值;