SDRAM知识普及

在学习SDRAM之前,必须先了解"SDRAM"这个概念性的东西,并有感性的认识转变到一种理性的认识,所谓理性的认识就是实质性的东西…….不多说,相信你已经迫不急待了。那我们就开始了。

初识SDRAM

SDRAM的全称是:Synchronous Dynamic Random Access Memory,同步动态随机存储器,同步是指 Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据读写。

相信通过这段话,你已经知道什么是SDRAM了,这里面有几个概念性的东西需要我们好好了解:同步、动态、随机。

同步:这个词在FPGA设计之中我们经常会遇到它,它反映了驱动sdram必须遵守一种时序原则,就是数据/命令和时钟在时间上同时的概念,也是在驱动sdram时要十分注意的一点。

动态:RAM这中存储结构会掉电丢失,在上电的时候也会丢失。为什么?因为SDRAM内部存储的数据是二进制数据,非0则1。用来存储该二进制数据的电路是由电容构成的,由于电容这种器件会随着时间而慢慢放电,就像人的记忆一样,有些记忆会随着时间的流逝而淡忘了。很简单,如果你不想让某些事某些人淡忘,怎么办?就只有时不时地去回忆。那SDRAM不想"忘"了它的数据,怎么办,一样,也只有不断地回忆,就是不断地去刷新里面的存储电路。

随机:随机就是不指定为一次连续,也就是可以对SDRAM里面的随意地址进行读写操作。

SDRAM的历史

SDRAM从发展到现在已经经历了四代,分别是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM.

第一代SDRAM采用单端(Single-Ended)时钟信号,第二代、第三代与第四代由于工作频率比较快,所以采用可降低干扰的差分时钟信号作为同步时钟。

SDR SDRAM的时钟频率就是数据存储的频率,第一代内存用时钟频率命名,如pc100,pc133则表明时钟信号为100或133MHz,数据读写速率也为100或133MHz。

之后的第二,三,四代DDR(Double Data Rate)内存则采用数据读写速率作为命名标准,并且在前面加上表示其DDR代数的符号,PC-即DDR,PC2=DDR2,PC3=DDR3。如PC2700是DDR333,其工作频率是333/2=166MHz,2700表示带宽为2.7G。

DDR的读写频率从DDR200到DDR400,DDR2从DDR2-400到DDR2-800,DDR3从DDR3-800到DDR3-1600。

实验中要操作的SDRAM就是第一代SDRAM,虽然SDRAM经历了这么多次的更新换代,但其内部的架构还是相差无几,更多的是在速率和存储数量上的不同。

实验的SDRAM介绍

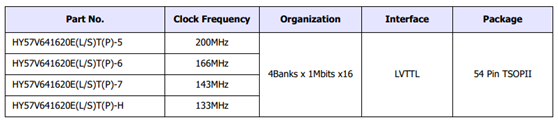

通过上面的两节,相信你已经对SDRAM已经有了大致的了解。现在就以实验中用到的SDRAM--HY57V641620ET-H(海力士的SDRAM)为一个例子对SDRAM的内部结果进行一个详细的介绍

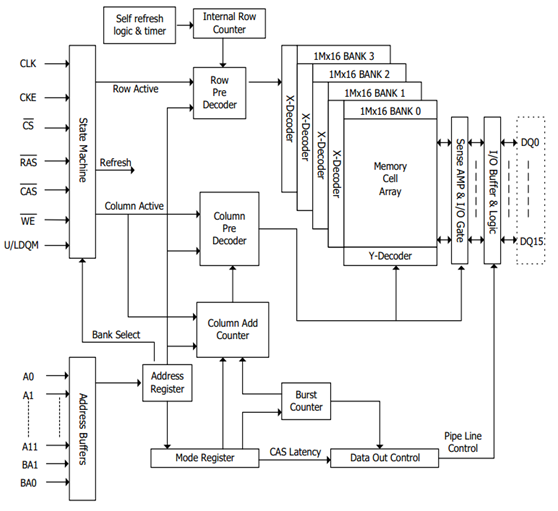

HY57V641620ET-H的内部结构

通过上图可以看到SDRAM的"五脏六腑",下面就来一一剖析:

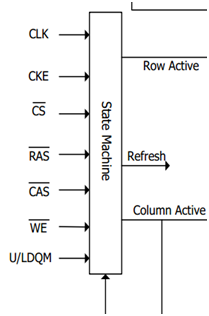

SDRAM指令接口模块,这些信号组成了SDRAM的控制指令,控制指令通过"state machine"进行译码,由此产生了一系列的控制动作。

SDRAM地址线,其中包括块地址线、行地址线、列地址线,至于会有这么多线,是因为用到了总线复用,其行线和列线分时复用,从而节省了总线资源,又可以操作到SDRAM的全部存储单元。至于块地址线,下面会讲到。

SDRAM存储块和数据接口:HY57V641620ET-H内部存储由四个一模一样的存储块组成,至于怎么识别这四个存储块,必须要有两条地址线,所以就用到了上面的那两条地址线。

动作电路模块:这几个模块主要是根据"state machine"的译码结果进行工作的、包括行列地址的编码、自刷新定时和自刷新操作。

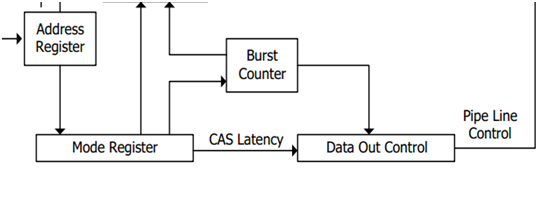

模式寄存器解码和突发操作模块:在对SDRAM的寄存器进行配置的时候,是通过地址线对SDRAM进行配置的,SDRAM中有一种突发操作模式,该模式由寄存器进行配置,所以该电路中包含一个突发操作的计数器。至于突发操作的原理下面会涉及到。

相信看到这里,你已经对SDRAM由感性的认识升级到实质性的认识,恭喜你,哈哈….

HY57V641620ET-H的存储量

看到这之前相信你应该了解过不少SDRAM的资料,也相信很多资料中从未讲过SDRAM名称的问题,现在我就来帮你解析这个SDRAM

HY:代表是海力士的SDRAM存储器

57:代表这是SDRAM芯片

V:代表这个SDRAM芯片工作电压是3.3V

641620:代表这个SDRAM芯片的存储容量

ET:代表SDRAM的块反应时间和封装

H:代表SDRAM的速度等级

下面我们来计算下这个芯片的存储容量:

存储容量由存储深度和存储宽度决定,这是任何存储芯片存储容量的定义;

存储深度:HY57V641620ET-H内部有4个块,每个块有行地址12bit,列地址8bit

所以每个块就有2^12*2^8 = 4096*256=1048576个存储单元,4个块就有4*1048576=4194304个存储单元。

存储宽度:该SDRAM的数据位宽为16bit

存储容量:4194304*16bit = 67108864bit,就是64M

大西瓜FPGA-->https://daxiguafpga.taobao.com

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。