逻辑综合

定义:

将RTL源代码转换成门级网表,将HDL语言描述的电路转换为工艺库器件构成的网络表的过程。在综合过程中,优化进程尝试完成库单元的组合,是组合成的电路能最好的满足设计的功能、时序和面积的要求。

逻辑综合组成:

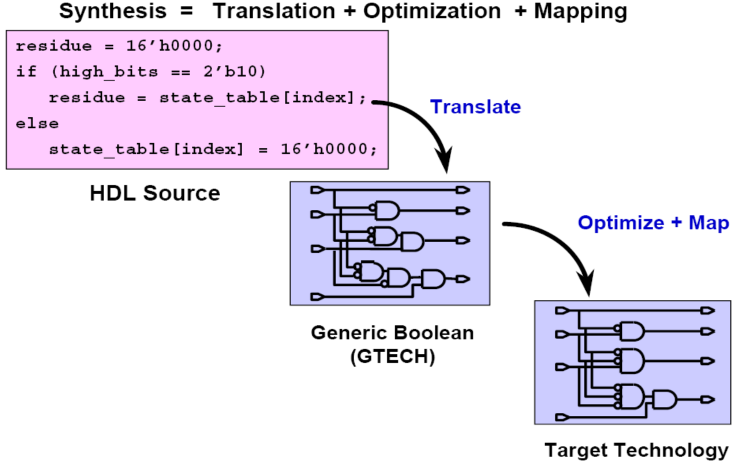

电路的综合一般分为三个步骤,分别是转化(Translation)、逻辑优化(Logic Optimizaion)和映射(Mapping)。

转化(Translation):把描述RTL级的HDL语言,在约束下转化成DC内部的同意用门级描述的电路(Generic Boolean Gates).

逻辑优化(Logic Optimization):把统一用门级描述的电路进行优化,改善路径和门。

映射(Mapping):把优化了的统一门级描述。以DC为例,DC使用工艺库将电路映射出来,得到.ddc文件,该文件包含如映射的门电路信息与网表,.v格式的网标,延时信息(sdf),工作约束(sdc)等信息。.ddc中包含的网标是实际意义上的网表文件,.v的网表是用于进行后仿的文件。

综合过程中的约束:

约束对于综合而言非常重要,如果不施加约束,综合工具会产生非优化的网表,无法满足要求。

综合是约束驱动(Constraint driven)的,给定的约束是综合的目标,约束一般是在对整个系统进行时序分析得到的,综合工具会对电路进行优化以满足约束的要求。

综合以时序路径为基础进行优化。

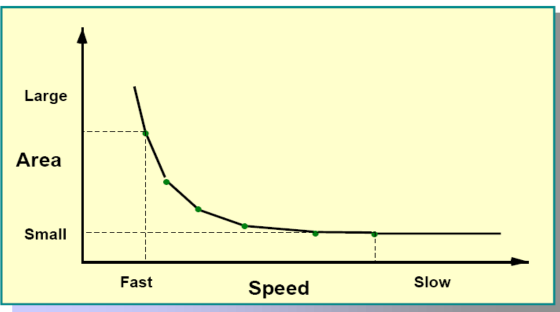

综合过程中时序与面积的关系:

下图为综合过程中时序与面积的关系,面积和延迟存在折中关系。综合工具以约束为指导,在满足时序的情况下获得最小面积。

综合的基本流程:

- 准备RTL代码,经过前端仿真后才能用于综合;

- 定义库,设定好所需要用到的综合库等多种库;

- 读入设计,综合工具读入RTL代码并进行分析;

- 定义设计环境,设定设计的工作环境、端口的驱动和负载、线负载模型等;

- 设置设计约束(关键),主要是定义时钟和I/O的约束,约束要适当,只有正确的约束才能得到正确的结果;

- 设置综合策略,top-down和bottom-up两种策略,根据需求进行选择;

- 优化设计,综合工具可以根据约束对电路进行优化,也可认为加入命令改变优化方法;

- 分析和解决设计的问题,在设计综合后,根据报告分析设计中出现的问题,并修订问题;

- 保存设计数据,综合结束后,保存各种数据以供后续布局布线使用(需先通过验证)。

常用综合工具:

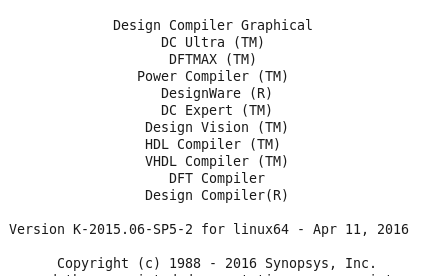

Synopsys 的Design Compiler;

Candance的Enconter RTL Compiler。

Design Compiler

启动Design Compiler方式:

- 在命令行输入dc_shell启动终端控制,再在dc_shell>后输入start_gui打开图形界面(Design Vision),可以输入-help查看启动选项。在命令行输入dc_shell -gui可以进入dc_shell并打开图形界面;

- 使用design_vision,通过design_vision -help查看DC的启动选项;

- .Batch mode,上面两种方式只启动DC,需要通过source命令开始进行编译;使用Batch mode在启动过程中开始执行脚本,如:dc_shell -topo -f run.tcl | tee -i run.log:意思是:使用拓扑模式启动DC,启动的同时执行run.tcl脚本文件,并且把启动过程中显示在终端的信息记录到run.log中。| tee -i就是写进信息的管道命令,讲dc_shell -topo -f run.tcl 执行后显示的信息(输出结果),流入到run.log文件中。这样子是为了在DC启动失败的时候,通过查看启动信息,进而排除错误。

工作模式有两种:

一种是Tcl模式;

另一种是图形模式;

DC工具组成:

参考文献:

《Tcl与Design Compiler (二)——DC综合与Tcl语法结构概述》https://www.cnblogs.com/IClearner/p/6617207.html