第一章 计算机组成与体系结构

系统构建于硬件与操作系统之上,对计算机底层原理有一定认识后,我们可以对安全与性能有更好的了解、认识,方便优化。

1.1 计算机系统组成

计算机系统是一个硬件和软件的综合体,可看做是按功能划分的多级层次结构。

1.1.1 计算机硬件的组成

硬件通常指能看得见、摸得着的设备实体。

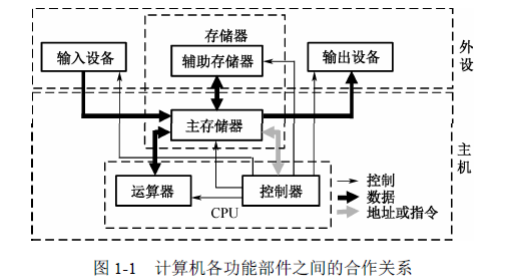

原始的冯-诺依曼 计算机在结构上以运算器为中心,现在转向以存储器为中心了。

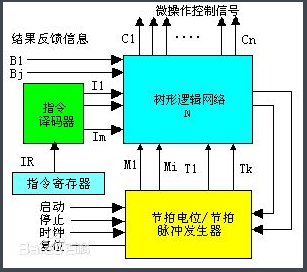

(1)控制器的组成:

1>.程序计数器PC(program counter)

详细解释摘自百度

程序计数器是用于存放下一条指令所在单元的地址的地方。

当执行一条指令时,首先需要根据PC中存放的指令地址,将指令由内存取到指令寄存器中,此过程称为“取指令”。与此同时,PC中的地址或自动加1或由转移指针给出下一条指令的地址。此后经过分析指令,执行指令。完成第一条指令的执行,而后根据PC取出第二条指令的地址,如此循环,执行每一条指令。

程序计数器是计算机处理器中的寄存器,它包含当前正在执行的指令的地址(位置)。当每个指令被获取,程序计数器的存储地址加一。在每个指令被获取之后,程序计数器指向顺序中的下一个指令。当计算机重启或复位时,程序计数器通常恢复到[1] 零。

2>.指令寄存器IR (Instruction Register):存储即将执行的指令

3>.指令译码器ID (Instruction Decoder) :对指令中的操作码字段进行分析解释

操作码表示要执行的操作性质,即执行什么操作,或做什么;

地址码是操作码执行时的操作对象的地址。

计算机执行一条指定的指令时,必须首先分析这条指令的操作码是什么,以决定操作的性质和方法,

然后才能控制计算机其他各部件协同完成指令表达的功能。这个分析工作由译码器来完成。

4>.时序部件:提供时序控制信号

(2)运算器,运算器也称为算术逻辑单元(ArithmeticandLogicUnit ,ALU), 主要功能时在控制器的控制下完成各种算术运算和逻辑运算。

运算器组成包含:

1>.算术逻辑单元ALU:数据的算术运算和逻辑运算

2>.累加寄存器AC (accumulator ):通用寄存器,为ALU提供一个工作区,用于暂存数据

3>.数据缓冲寄存器DR(Data Register):写内存时,暂存指令或数据

4>.状态条件寄存器PSW:存状态标志与控制标志(也有的,将他归类为:控制器)

(3)主存储器 (也称为内存储器,内存或者主存)。

(4)辅助存储器(也称为外存储器,外存或者辅存),存储需要长期保存的各种信息

(5)输入设备

(6)输出设备

1.1.2 计算机系统结构的分类

计算机的发展经历了电子管、晶体管时代、集成电路时代(中小规模、大规模、超大规模、甚大规模、极大规模)。

1.存储程序的概念

1946年6月冯-诺依曼等人提出,可概括为:

(1)计算机(指硬件)应由运算器、存储器、控制器、输入设备、输出设备五大基本部件组成。

(2)计算机内部采用二进制来表示指令和数据

(3)将编好的程序和原始数据事先存入存储器中,然后再启动计算机工作。

冯-诺依曼型计算机的主要弱点:存储器访问

通过百度文库检索到的这篇文章,观点:认为冯-诺依曼结构体系的瓶颈主要是因为:串性

https://wenku.baidu.com/view/7c8bd42f2af90242a895e58d.html

目前出现的一些突破存储程序控制的计算机,统称为:非冯-诺依曼型计算机,

例如:数据驱动的数据流计算机、需求驱动的归约计算机和模式匹配驱动的智能计算机等。

2.Flynn分类

1966年,Michael.J.Flynn 提出根据指令流-数据流的多倍性特征对计算机系统进行分类(通常称为Flynn分类法),有关定义:

(1)指令流:指机器执行的指令序列;

(2)数据流:指由指令流调用的数据序列,包括输入数据和中间结果,但不包括输出数据。

Flynn 根据不同的指令流-数据流组织方式,把计算机系统分成四类:

(1)单指令流单数据流(Single Instruction stream and Single Data stream ,SISD)

SISD就是传统的顺序执行的单处理计算机,其指令部件每次只对一条指令进行译码,并只对一个操作部件分配数据。

(2)单指令流多数据流(Single Instruction stream and Multiple Data stream,SIMD)

SIMD以并行处理机(矩阵处理机)为代表,并行处理机包括多个重复的处理单元,由单一指令部件控制,按照同一指令流的要求为它们分配各自所需的不同数据。

(3)多指令流单数据流(Multiple Instruction stream and Single Data stream,MISD)

MISD具有n个处理单元,按n条不同指令的要求对同一数据流及中间结果进行不同的处理。一个处理单元的输出又作为另一个处理单元的输入。这类系统实际上很少见到。有文献把流水线看作多个指令部件,称流水线计算机是MISD。

(4)多指令流多数据流(Multiple Instruction stream and Multiple Data stream ,MIMD)

MIMD 是指能实现作业、任务、指令等各级全面并行的多机系统。如多核处理器、多处理机属于MIMD。

1.1.3 复杂指令集系统与精简指令集系统

计算机系统结构发展的过程中,指令系统的优化设计有两个截然相反的方向,

一个是增强指令的功能,设置一些功能复杂的指令,把一些原来由软件实现的、常用的功能改用硬件的指令系统来实现,这种计算机系统 统称为复杂指令系统计算机(Complex Instruction Set Computer ,CISC)

另一个是尽量简化指令功能,只保留那些功能简单,能在一个节拍内执行完成指令,较复杂的功能用一段子程序来实现,这种计算机系统统称为精简指令系统计算机

(Reduced Instruction Set Computer,RISC)

1.CISC指令系统的特点

CISC指令系统的主要特点:

(1)指令数量众多。指令系统拥有大量的指令,通常有100~250条。

(2)指令使用频率相差悬殊。最常使用的是一些比较简单的指令,仅占指令总数的20%,但在程序中出现的频率缺占80%。而大部分复杂指令却很少使用。

(3)支持很多种寻址方式。支持的寻址方式通常为5~20种。

(4)变长的指令。指令长度不是固定的,变长的指令增加指令译码电路的复杂性。

(5)指令可以对主存单元中的数据直接进行处理。

典型的CISC 通常都有指令能够直接对主存单元中的数据进行处理,其执行速度较慢。

(6)以微程序控制为主。CISC的指令系统很复杂,难以用硬布线逻辑(组合逻辑)电路实现控制器,通常采用微程序控制。

https://baike.baidu.com/item/%E7%A1%AC%E5%B8%83%E7%BA%BF%E6%8E%A7%E5%88%B6%E5%99%A8/5791306

硬布线控制器是早期设计计算机的一种方法。硬布线控制器是将控制部件做成产生专门固定时序控制信号的逻辑电路,产生各种控制信号,因而又称为组合逻辑控制器。这种逻辑电路以使用最少元件和取得最高操作速度为设计目标,因为该逻辑电路由门电路和触发器构成的复杂树型网络,所以称为硬布线控制器。

一旦控制部件构成后,除非重新设计和物理上对它重新布线,否则要想增加新的控制功能是不可能的。 硬布线控制器是计算机中最复杂的逻辑部件之一。

2.RISC 指令系统特点:

RISC要求指令系统简化,操作在单周期内完成,指令格式力求一致,寻址方式尽可能减少,并提高编译的效率,最终达到加快机器处理速度的目的。

RISC指令系统的主要特点:

(1)指令数量少。优先选取使用频率最高的一些简单指令和一些常用指令,避免使用复杂指令。 只提供了LOAD(从存储器中读数)和STORE(把数据写入存储器)两条指令对存储器操作,其余所有的操作都在CPU的寄存器之间进行。

(2)指令的寻址方式少。通常只支持寄存器寻址方式、立即数寻址方式和相对寻址方式。

(3)指令长度固定,指令格式种类少。因为RISC指令数量少、格式少、相对简单,其指令长度固定,指令之间各字段的划分比较一致,译码相对容易。

(4)以硬布线逻辑控制为主,为了提高操作的执行速度,通常采用硬布线逻辑(组合逻辑)来构建控制器

(5)单周期指令执行,采用流水线技术。因为简化了指令系统,很容易利用流水线技术,使得大部分指令都能在一个机器周期内完成。少数指令可能会需要多周期,例如,LOAD/STORE指令因为需要访问存储器,其执行时间就会长一些。

(6)优化的编译器:RISC的精简指令集使编译工作简单化。因为指令长度固定、格式少、寻址方式少,编译时不必在具有相似功能的许多指令中进行选择,也不必为寻址方式的选择而费心,同时易于实现优化,从而可以生成高效率执行的机器代码。

(7)CPU中的通用寄存器数量多,一般在32个以上,有的可达上千个。

大多数RISC采用了Cache方案,使用Cache来提高取指令的速度。而且,有的RISC使用两个独立的Cache来改善性能。一个称为指令Cache,另一个称为数据Cache。这样,取指令和取数据可以同时进行,互不干扰。

1.1.4总线

总线是一组能为多个部件分时共享的公共信息传送线路。

共享是指总线上可以挂接多个部件,各个部件之间相互交换的信息都可以通过这组公共线路传送;

分时是指同一时刻只允许有一个部件向总线发送信息,如果出现两个或两个以上部件同时向总线发送信息,势必导致信息冲突。当然,在同一时刻,允许多个部件同时从总线上接收相同的信息。

按总线相对于CPU或其他芯片的位置可分为:内部总线和外部总线两种。

1.在CPU内部,寄存器之间和算术逻辑部件ALU 与控制部件之间传输数据所用的总线称为内部总线。

2.外部总线:指CPU与内存RAM、ROM和输入/输出设备接口之间进行通信的通路。

由于CPU通过总线实现程序取指令、内存/外设的数据交换,在CPU与外设一定的情况下,总线速度是制约计算机整体性能的最大因素。

按总线功能来划分,又可分为地址总线、数据总线、控制总线三类。

地址总线用来传送地址信息,数据总线用来传送数据信息,控制总线用来传送各种控制信号。