1 Scope of Document

This document describes i2c bus hardware design and support i2c-devices: eeprom(at24c08) rtc(rx8025).

2 Requiremen

2.1 Function Requirement

Enumerate i2c bus eeprom and rtc i2c-device, load corresponding drivers

2.2 Performance Requirement

NA

3 Hardware Overview

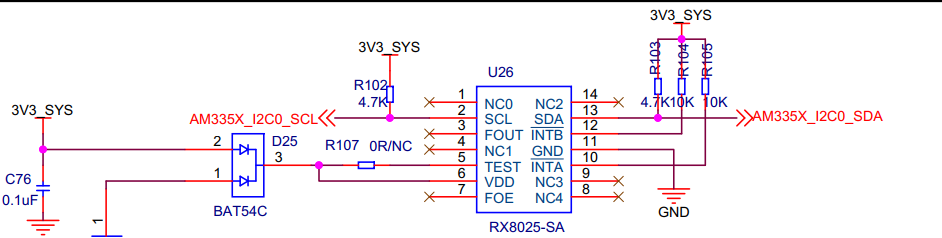

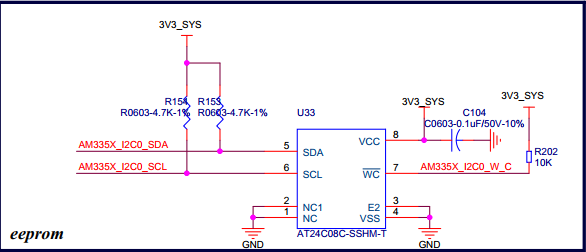

i2c interface,pin map:

AM335X_I2C0_SCL------------------I2C0_SCL

AM335X_I2C0_SDA------------------I2C0_SDA

Figure 1 tf interface block diagram

4 Functional Description

4.1 I2C

4.1.1 Overview

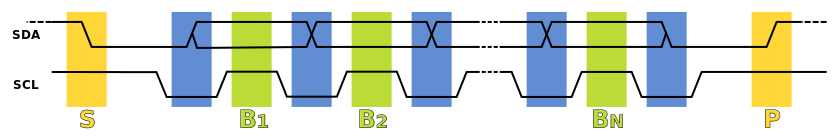

Figure 2 timing diagram

- Data transfer is initiated with a start bit (S) signaled by SDA being pulled low while SCL stays high.

- SCL is pulled low, and SDA sets the first data bit level while keeping SCL low (during blue bar time).

- The data are sampled (received) when SCL rises for the first bit (B1). For a bit to be valid, SDA must not change between a rising edge of SCL and the subsequent falling edge (the entire green bar time).

- This process repeats, SDA transitioning while SCL is low, and the data being read while SCL is high (B2, ...Bn).

- The final bit is followed by a clock pulse, during which SDA is pulled low in preparation for the stop bit.

- A stop bit (P) is signaled when SCL rises, followed by SDA rising.

5 Porting

5.1 Kernel porting

Dts file :

i2c0_pins: pinmux_i2c0_pins {

pinctrl-single,pins = <

AM33XX_IOPAD(0x988, PIN_INPUT_PULLUP | MUX_MODE0)

AM33XX_IOPAD(0x98c, PIN_INPUT_PULLUP | MUX_MODE0)

>;

};

&i2c0 {

pinctrl-names = "default";

pinctrl-0 = <&i2c0_pins>;

status = "okay";

clock-frequency = <400000>;

at24c08@50 {

compatible = "atmel,24c08";

pagesize = <16>

reg = <0x50>;

};

rtc@32 {

compatible = "epson,rx8025";

reg = <0x32>;

};

};

[ 1.795430] at24 0-0050: 1024 byte 24c08 EEPROM, writable, 16 bytes/write

[ 1.803203] rtc-rx8025 0-0032: rx8025_get_time: read 0x09 0x01 0x06 0x06 0x16 0x11 0x18

[ 1.803220] rtc-rx8025 0-0032: rx8025_get_time: date 9s 1m 6h 16md 10m 118y

[ 1.803504] rtc rtc0: rx8025: dev (253:0)

[ 1.803534] rtc-rx8025 0-0032: rtc core: registered rx8025 as rtc0

[ 1.809854] omap_i2c 44e0b000.i2c: bus 0 rev0.11 at 400 kHz

[ 3.179312] rtc-rx8025 0-0032: rx8025_get_time: read 0x10 0x01 0x06 0x06 0x16 0x11 0x18

[ 3.179330] rtc-rx8025 0-0032: rx8025_get_time: date 10s 1m 6h 16md 10m 118y

[ 3.179373] rtc-rx8025 0-0032: setting system clock to 2018-11-16 06:01:10 UTC (1542348070)

6 Follow-up

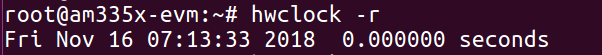

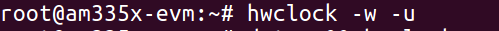

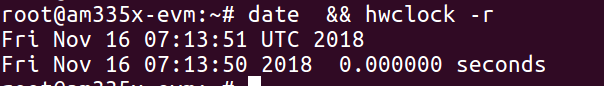

Read rtc:

Write rtc:

test rtc:

eeprom access dir:

/sys/bus/i2c/devices/0-0050