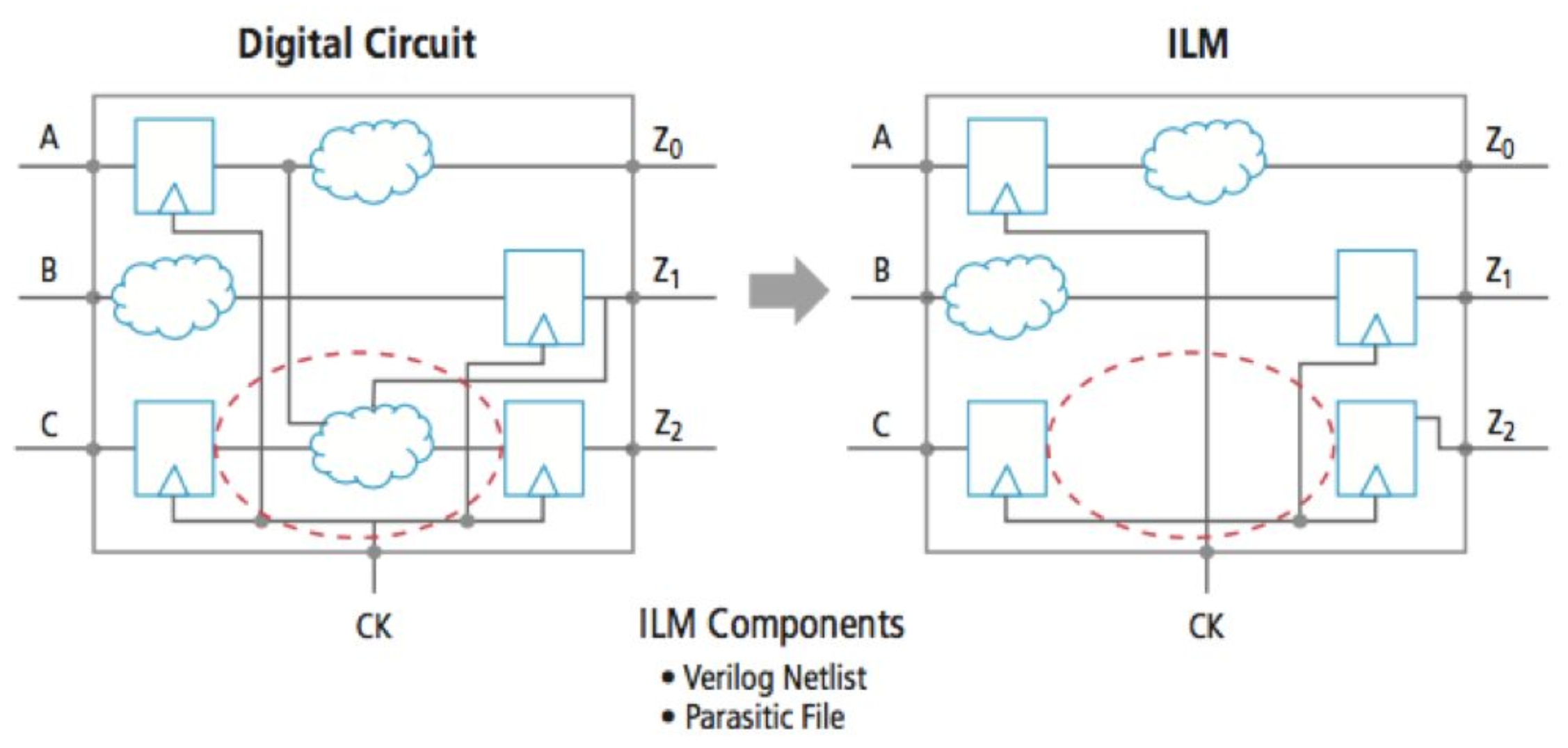

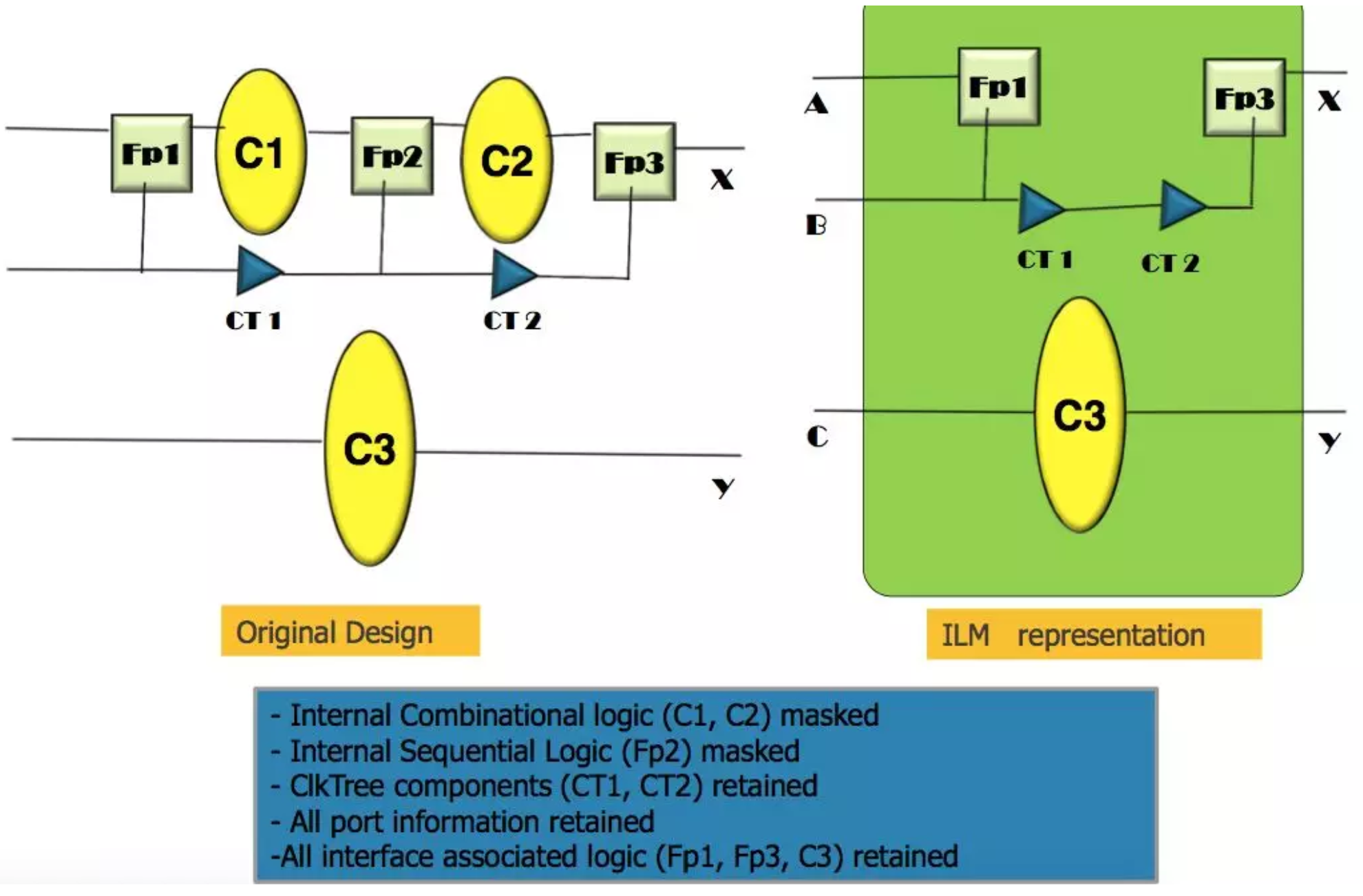

1.描述接口逻辑的模型。

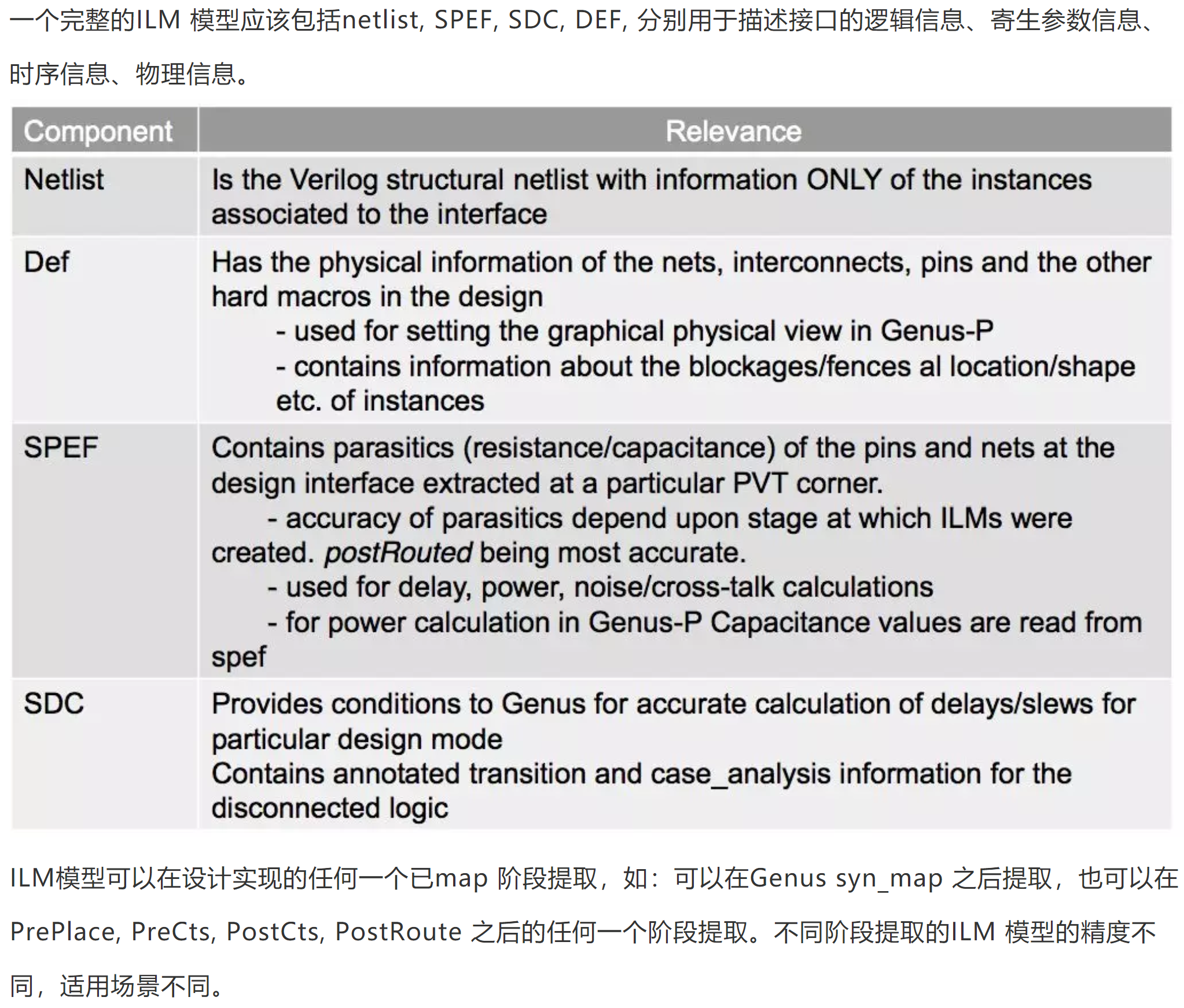

2.包括 netlist spef sdc def

3.所有以上文件只描述和接口相关的逻辑,其他逻辑一概排除

3.用于STA/PR/DC的hierachical flow,相对于ETM model,更精确,ETM 只包含接口的timing arc信息,无法精确的进行cross talk 分析

4.XILM 包含接口的耦合电容信息,可用于精确的cross talk 分析

5.ILM模型可以在设计实现的任何一个已map 阶段提取,如:可以在Genus syn_map 之后提取,也可以在PrePlace, PreCts, PostCts, PostRoute 之后的任何一个阶段提取。不同阶段提取的ILM 模型的精度不同,适用场景不同。

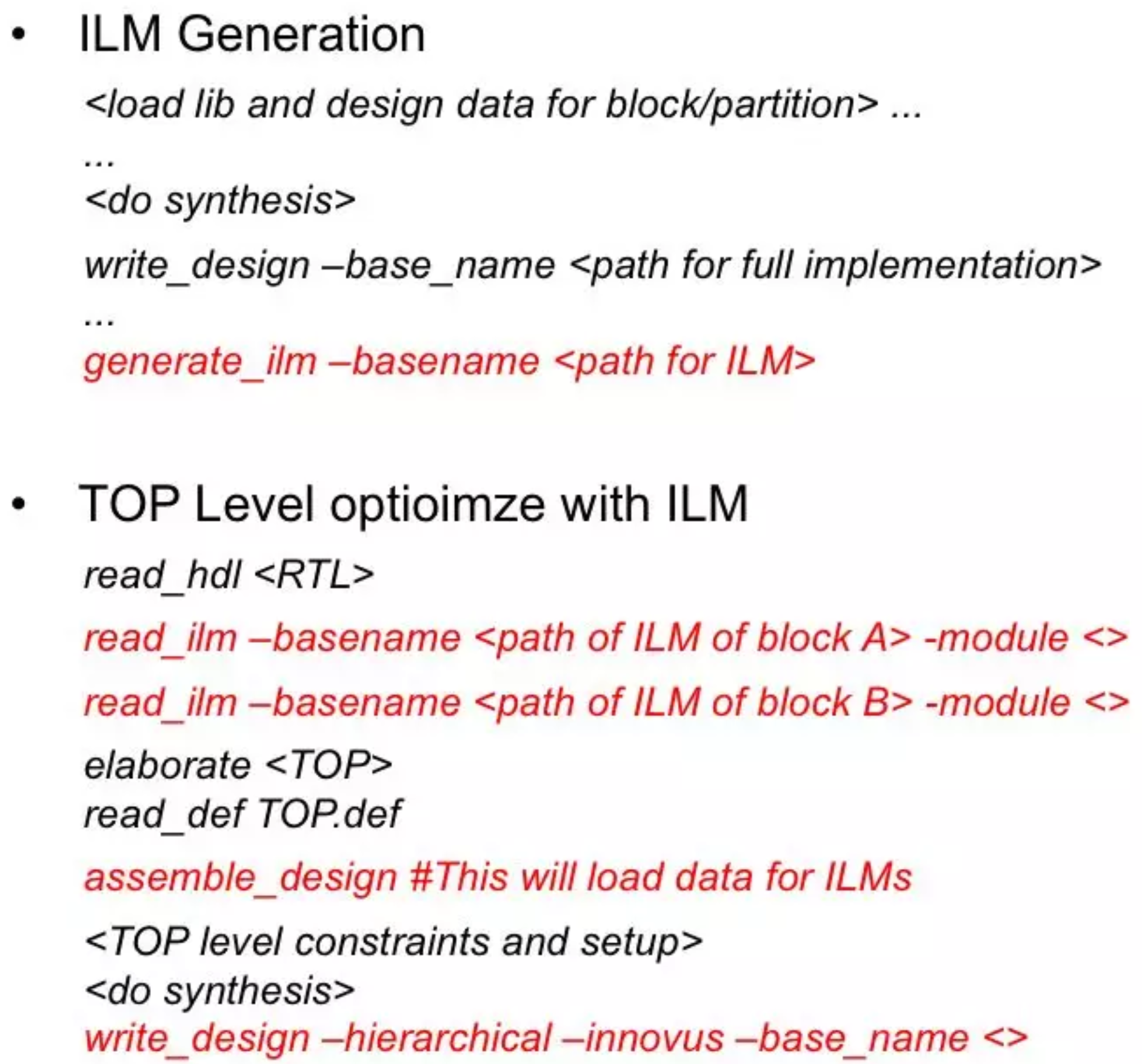

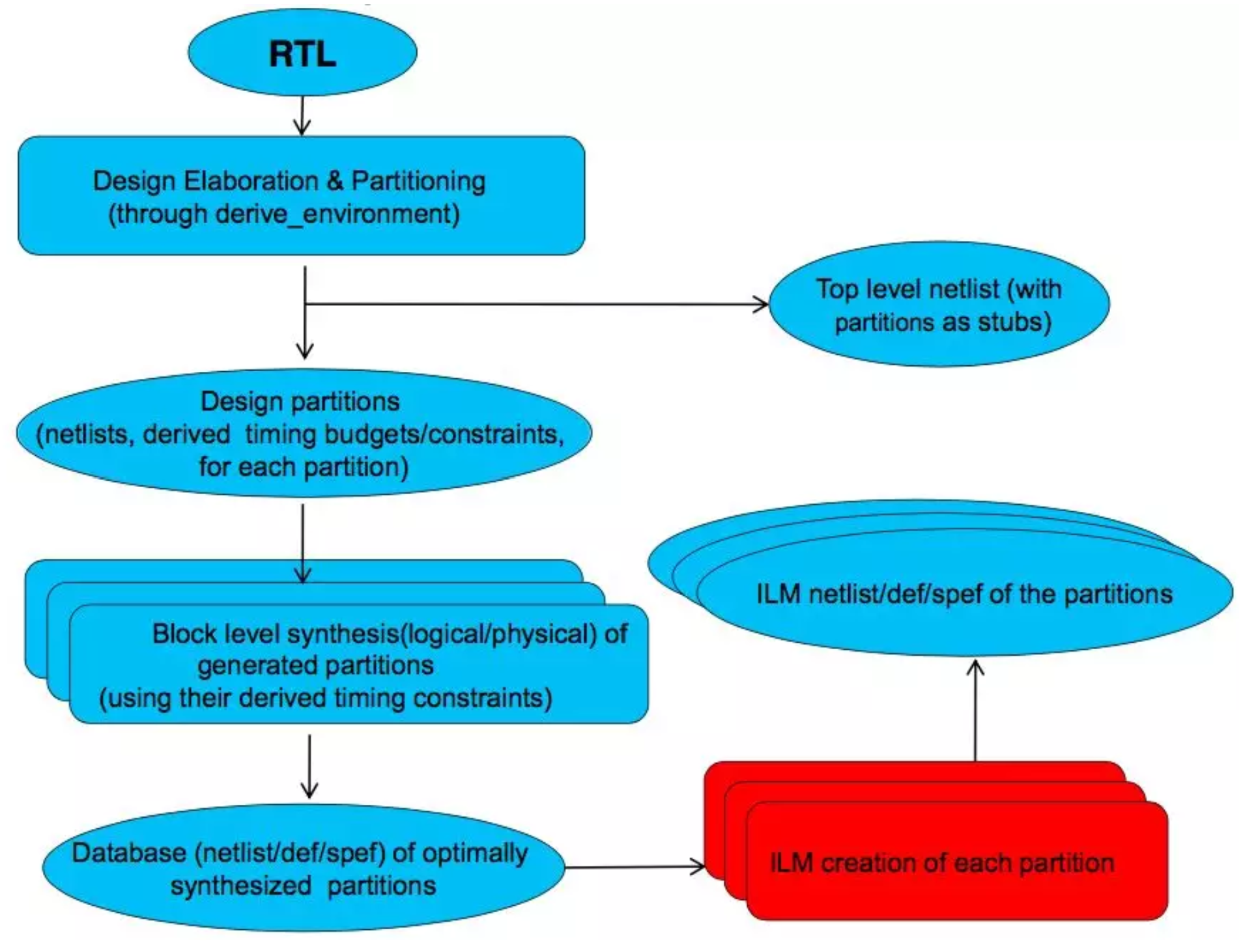

6.Genus 用ILM 模型做hierarchical 综合的流程非常简单明了,如下图所示,如果当前没有sub module 的ILM 模型,可以先用Genus 对sub module 进行综合,并用命令 "generate_ilm" 生产一个ilm 模型;然后再综合上一层设计,在综合父级设计时关键的命令只有两个 " read_ilm " 跟 " assemble_design "。

7.