参考网站:https://forums.xilinx.com/t5/Video-and-Audio/Xilinx-Video-Series/td-p/849583

1、数字视频简介

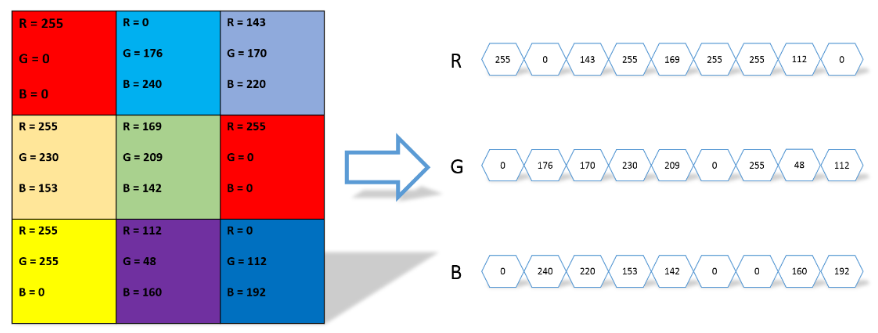

图像是由像素(pixel)构成的阵列

对于彩色图像,像素由三个值确定——R,G,B

视频是一系列图像以一个特定频率变化出现

在从视频源到显示器传输过程中,每个图象的传输都是像素从上到下从左到右传输的

例如下图这个3x3像素图象传输

时间信号会和像素信号一起传输

视频帧包括视频流和消隐时段

信号传输过程中有水平消隐和垂直消隐,分别记作hblank和vblank https://blog.csdn.net/re_call/article/details/105756273?utm_medium=distribute.pc_relevant_t0.none-task-blog-BlogCommendFromMachineLearnPai2-1.nonecase&depth_1-utm_source=distribute.pc_relevant_t0.none-task-blog-BlogCommendFromMachineLearnPai2-1.nonecase

行同步和场同步(记作hsync and vsync)发生在hblank和vblank之间,表示将会开始新的一行或者一帧

消隐周期开始到同步信号开始之间的时间称为前沿(front porch),而同步信号结束和消隐信号结束之间的时间称为后沿(back porch)。

VGA_SOURCE IP是一个IP,它以1280x1024 @ 60Hz的分辨率生成VGA信号(视频的宽度为1280,高度为1024,图像每16.66ms(1 / 60Hz)更新一次)。

2、从本地视频到AXI4-Stream

- tdata:将视频数据从主机传输到从机

- tvalid:主机发送的信号,指示tdata上的数据何时有效

- tready:由从站用来指示何时准备就绪

- tuser:Xilinx视频IP使用它来指示帧的第一个像素(从主机到从机)

- tlast:Xilinx视频IP用来指示一行的最后一个像素(从主节点到从节点)

pynq的hdmi输出实验

参考:https://forums.xilinx.com/t5/Xilinx-产品设计与功能调试技巧/视频系列-23-在-Pynq-Z2-HDMI-输出上生成视频输出/ba-p/954606

https://blog.csdn.net/qq2419292516/article/details/90481663?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522159540492819725247650112%2522%252C%2522scm%2522%253A%252220140713.130102334..%2522%257D&request_id=159540492819725247650112&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~all~first_rank_ecpm_v3~pc_rank_v2-1-90481663.first_rank_ecpm_v3_pc_rank_v2&utm_term=pynq+hdmi&spm=1018.2118.3001.4187

按照如上链接,一步一步完成设置和实验

但是发现连接显示屏不能出现图像,为什么呢

从头开始一步一步检查,原来是约束文件.xdc出错了

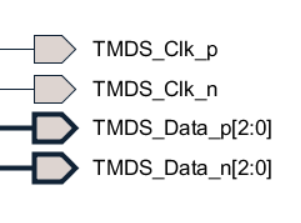

约束文件这一部分,这里应该和block中的引脚名称一样

之前直接抄的链接里面的xdc文件,却不知所以然,结果教程里面的引脚名称和我的不一样,导致xdc文件错误

修改以后显示屏输出如下