# HW 学习例子

- S3C2440 Chip -> Nand flash控制器

- K9F2G08U0A Nand Flash芯片

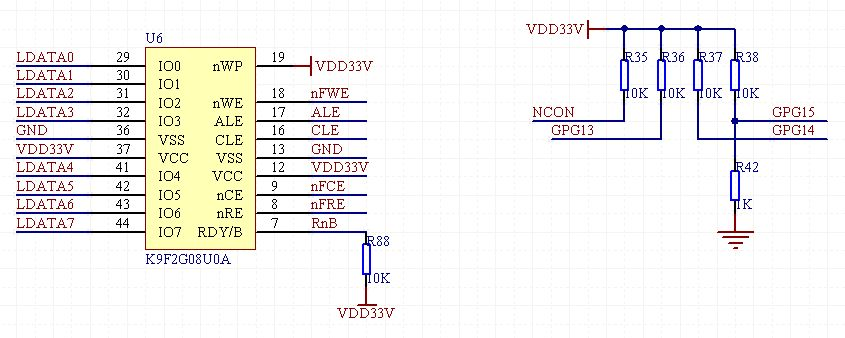

# K9F2G08U0A - Nand Flash 原理图理解

上图的左边为K9F2G08U0A与2440的连接图,右边的部分是S3C2440的Nand控制器的配置。

- IO0 - IO7 传地址也传数据

- CLE 低电平表示传命令

- ALE 低电平表示传地址

- CE 片选,当2440要操作访问Nand的时候,首先必须选中。

- RE 读状态,当RE为低的时候,表示数据由Nand流向2240;

- WE 写状态,当RE为低的时候,表示数据由2240流向Nand;

- WP 写保护,只能写,不能擦除。

- R/B 工作状态,工作中拉低,Done拉高表烧写完成

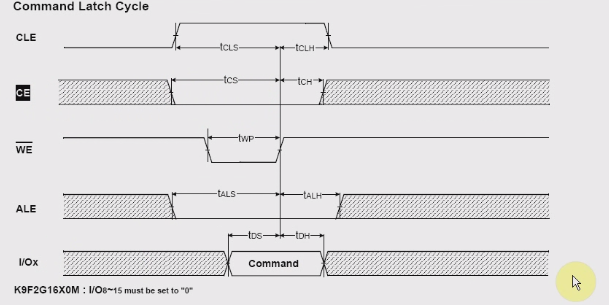

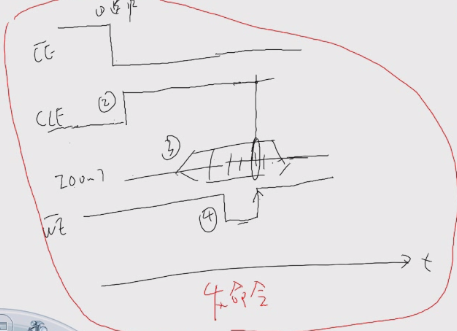

# 写命令时序图

首先CE发出片选信号,CLE发出高电平,IO 0-7将命令驱动出去,WE写脉冲,在写脉冲的上升沿,Nand flash在上升沿,将IO 0-7中数据读取出来。

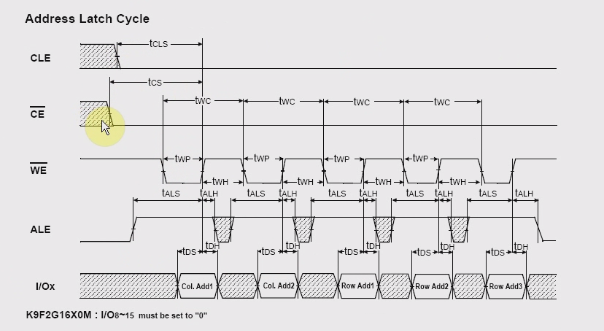

# 写地址时序图

CE片选, ALE由低变高,IO 0-7驱动 数据,WE发出写脉冲。

# 写数据时序图

CE选中,ALE、CLE低电平,2440 IO 0-7驱动 数据,WE写信号,Nand flash根据ALE、CLE低电平,读取数据。

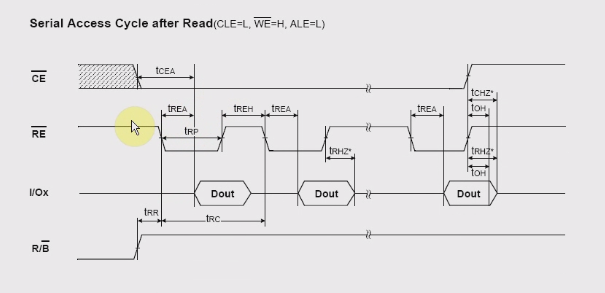

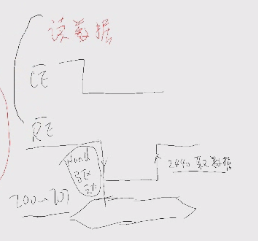

# 读数据时序图

CE低电平选中,RE由高变为低(Nand flash收到RE由高变低时,马上准备数据,然后在RE的上升沿将数据发送出去),Nand flash 驱动数据到IO 0-7,在上升沿,2440取数据。

# 如何设置时序

- 看2440手册,确定能设置哪些参数。

- 看外设(如Nand flash)手册,确定取值

- 计算

# 2440-Chip中Nand FLASH控制器的特性:

- 一个引导启动单元

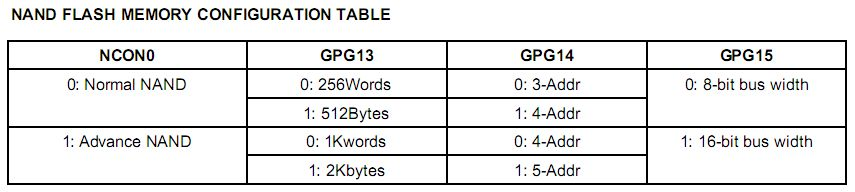

- Nand Flash存储器接口,支持8位或16位的每页大小为256字,512字节,1K字和2K字节的Nand flash

- 软件模式:用户可以直接访问Nand Flash存储器,此特性可以用于Nand Flash存储器的读、擦除和编程。

- S3C2440支持8/16位的Nand Flash存储器接口总线

- 硬件ECC生成,检测和指示(软件纠错)。

- Steppingstone接口,支持大/小端模式的按字节/半字/字访问。

# 具体操作简述

配置引脚NCON,GPG13,GPG14和GPG15用来设置Nand Flash的基本信息,Nand控制器通过读取配置引脚的状态获取外接的Nand Flash的配置信息。

2440这些引脚发出的数据,必须满足Nand flash的时序要求。需要查看2440芯片手册,查看设备哪个寄存器的某些位来控制时序。