参考书:

《Verilog HDL数字集成电路高级程序设计》蔡觉平,西安电子科技大学出版社 2015

《Verilog HDL 高级数字设计》电子工业出版社,Michael D. Ciletti著,张雅绮译,2008年.6

《Verilog HDL数字设计与综合》电子工业出版社,Samir Palnitkar,夏宇闻等译,2009.8

《VERILOG数字系统设计--RTL综合.测试平台与验证》电子工业出版社, Zainalabedin Navabi,李广军等译,2007

《硬件描述语言Verilog》 清华大学出版社,Thomas &Moorby,刘明业等译,2001.8

01.很多综合工具(如Quartus II)不允许边沿变化信号和电平变化信号同时出现在敏感事件表中。例如

always @(posedge clk , negedge rst ) //是正确的,可以被综合。 always @(posedge clk , rst ) //是错误的,不可以被综合。

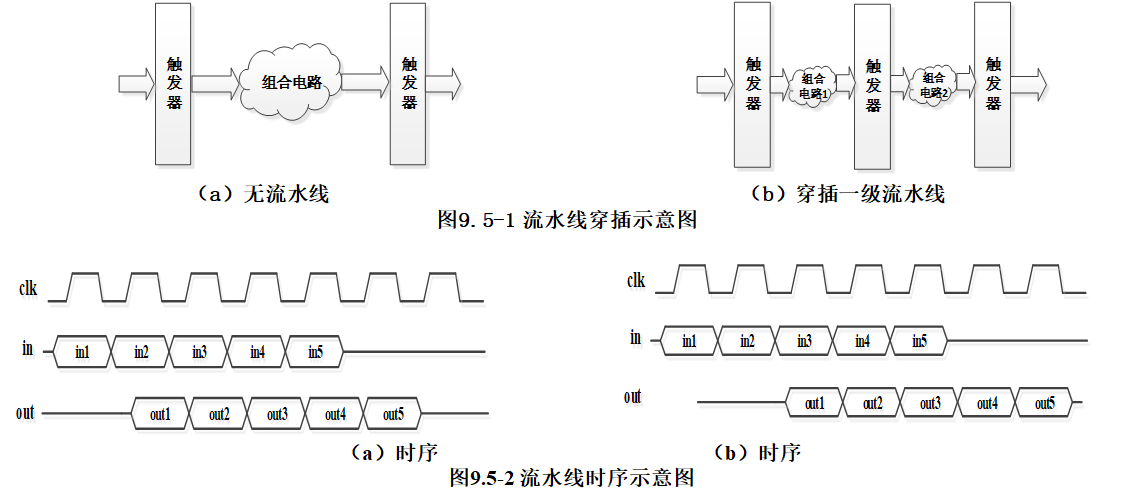

02.流水线设计图示:

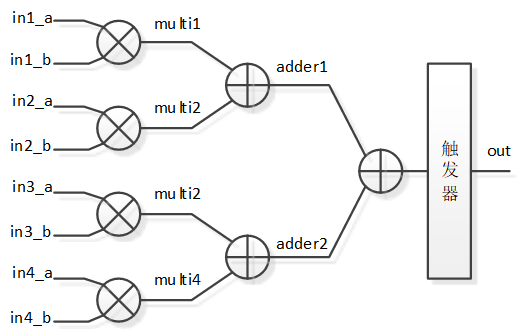

03.流水线设计实例:

乘加器电路(无流水线):

代码:

module muti_add(clk,in1_a,in1_b,in2_a,in2_b,in3_a,in3_b,in4_a,in4_b,out); input clk; input [3:0] in1_a,in1_b,in2_a,in2_b,in3_a,in3_b,in4_a,in4_b; output [8:0] out; reg [8:0]out; reg [6:0] mult1,mult2,mult3,mult4; reg [7:0]adder1,adder2; always@(posedgeclk) begin multi1=in1_a*in1_b; multi2=in2_a*in2_b; multi3=in3_a*in3_b; multi4=in4_a*in4_b; adder1= multi1+multi2; adder2= multi3+multi4; out=adder1+adder2; end endmodule

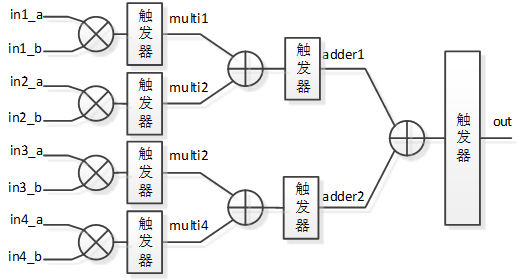

乘加器电路改进(流水线):

代码:

module muti_add(clk,in1_a,in1_b,in2_a,in2_b,in3_a,in3_b,in4_a,in4_b,out); input clk; input [3:0] in1_a,in1_b,in2_a,in2_b,in3_a,in3_b,in4_a,in4_b; output [8:0] out; reg [8:0]out; reg [6:0]mult1,mult2,mult3,mult4; reg [7:0]adder1,adder2; always@(posedgeclk) begin multi1<=in1_a*in1_b; multi2<=in2_a*in2_b; multi3<=in3_a*in3_b; multi4<=in4_a*in4_b; adder1<= multi1+multi2; adder2<= multi3+multi4; out<=adder1+adder2; end endmodule

04.