什么是脉动阵列

脉动阵列,是现在某些智能加速芯片的一种架构;由一组处理单元 Processor Elements组成;处理单元简称是PE,也经常简称为Cell;所有的Cell是用Mesh结构互连起来;每个Cell处理一系列的流经自己的数据;之后传递给邻居的Cell,大部分的Cell都是相同的操作。

SIMD和脉动阵列的区别

SIMD是和其相似的架构,但是SIMD如名字表达的那样,控制指令是唯一的,数据是不同的,并且数据从内存加载到PE;脉动阵列的区别是可能从片上的RAM加载到PE,并且每个PE有自己的控制单元,这样不仅仅是数据的并行了。

脉动阵列设计优势点

脉冲阵列用在专用的加速芯片上的优势是:1. 设计上比较规整,简单;2. 通信或者传递信息的并发性好;3. 平衡了计算和IO,因为一般都是计算等待IO。

脉动阵列分类

一维:适合单一的IO,因此用处不是很大;

二维:一般都是平面矩阵,放了很多的处理单元,但是只允许边界的单元进行IO;

三维:允许IO经过每个处理单元;

举例:使用二维脉动阵列计算矩阵乘

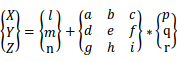

使用三个计算单元计算这个矩阵乘的设计

下面是三个脉动阵列:

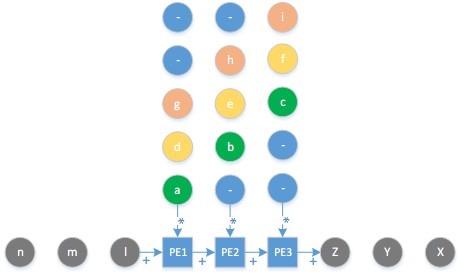

下面是每个步骤的过程数据:

可以看出,五部步可以计算出三个维度的计算结果。

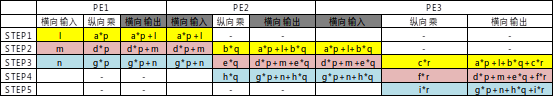

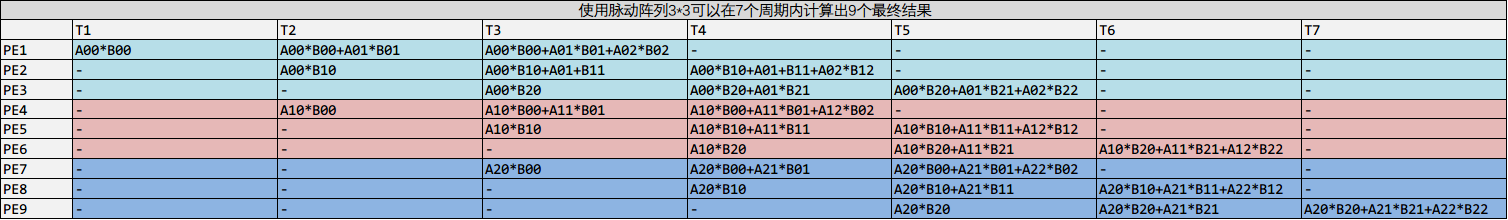

推而广之如果是平面矩阵的脉动阵列,其实可以计算两个二维矩阵的乘积:

*

*

脉动阵列的设计:

过程数据是:

对脉动阵列的设计可以有很多种方式。

脉动阵列的优势

- 对VLSI设计比较友好,适合模块化的设计;速度快,成本低;

- 使用本地化的互联结构;减少了全局广播等消耗;高维度的流水线;高维度的并行;

- 简单的IO子系统;

脉动阵列的劣势

- 全局同步受限于时延;

- 片上RAM的带宽要求比较大;

- 因为缺少互联的协议子系统,而缺少软件上的容错;