前言

当需要大容量数据存储及处理的时候,FPGA内部自带的存储资源是远远不够的,所以问题来了,怎么使用外带的DDR3?

首要问题在于DDR3是什么?有没有协议?当然只是需要用Xilinx MIG IP去配置使用的话,DDR3内部信号变化关系不需要太明了,当然明了会更佳,有时间可以看看底层内部架构,只是使用MIG IP去配置DDR3的话不需要像写一个DDR3控制器那么明白。

所需要预先储备的知识:

(1)阅读JEDEC DDR3 SDRAM STANDARD (标准协议)(有空的童鞋可以阅读);

(2)阅读ug586_7Series_MIS.pdf (XIlinx MIG核配置文档)(必须的);

(3)百度文库中的高富帅教程,百度一下就可以知道(推荐阅读);

Xiinx MIG IP为开发者提供了用户接口,极大的降低了开发者控制DDR3的难度,提升开发效率(然并卵)。

///////////////////////

1.看完上述文章后,你就想着怎么在vivado中生成MIG IP呢?

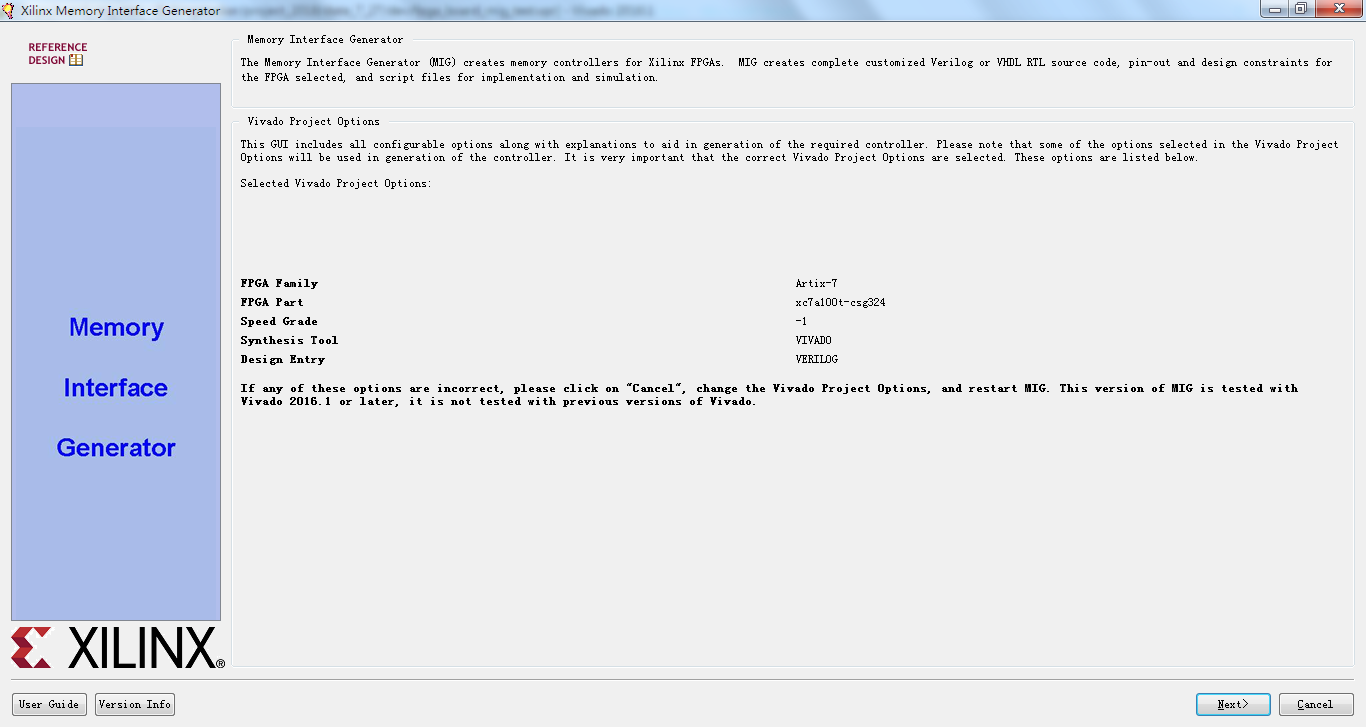

本次配置以NEXYS4开发板作为配置平台;Xilinx vivado 2016.1

NEXY4开发板上自带的DDR为DDR2 型号为MT47H64M16HR-25;

配置DDR3和DDR2基本上是类似的;

(1)打开IP配置界面,搜索MIG:

(2)配置,next:

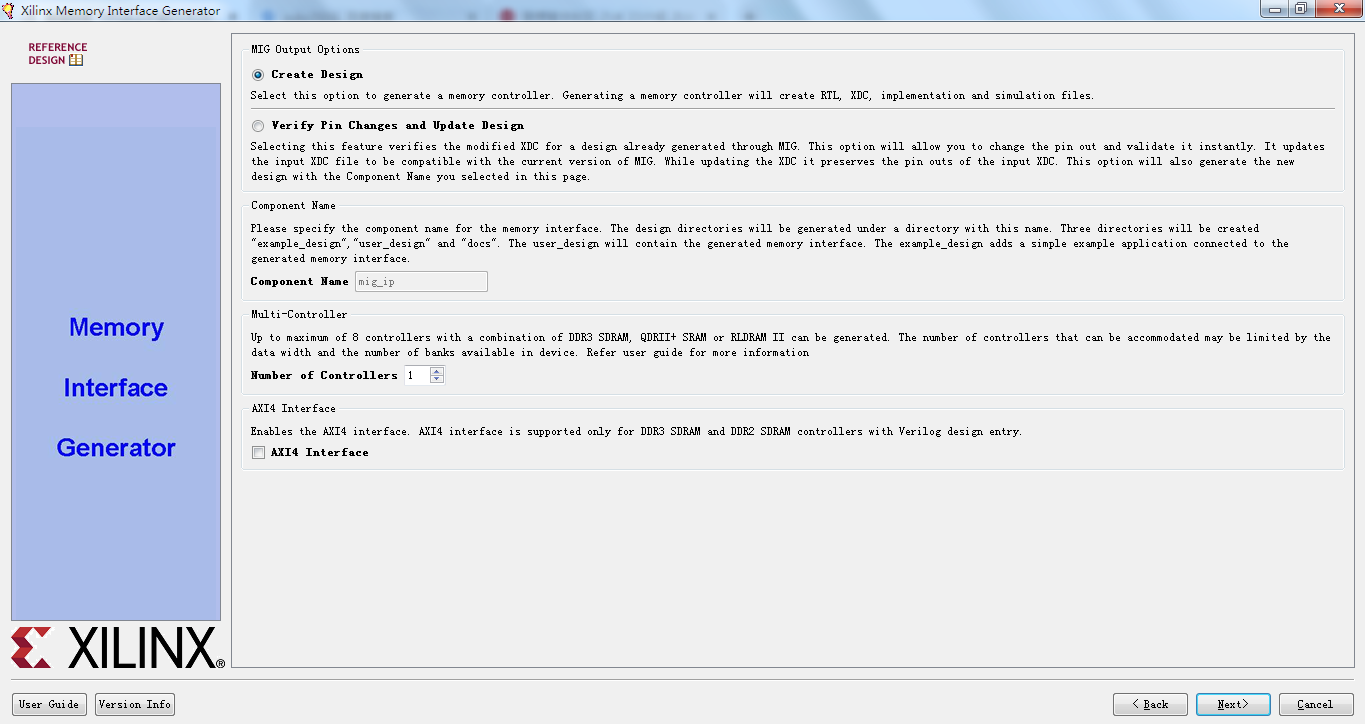

(3)当然是创建新设计,例化IP的名字修改,由于已经生成好的,所以显示为灰色。

然后选择一个控制器。。。next:

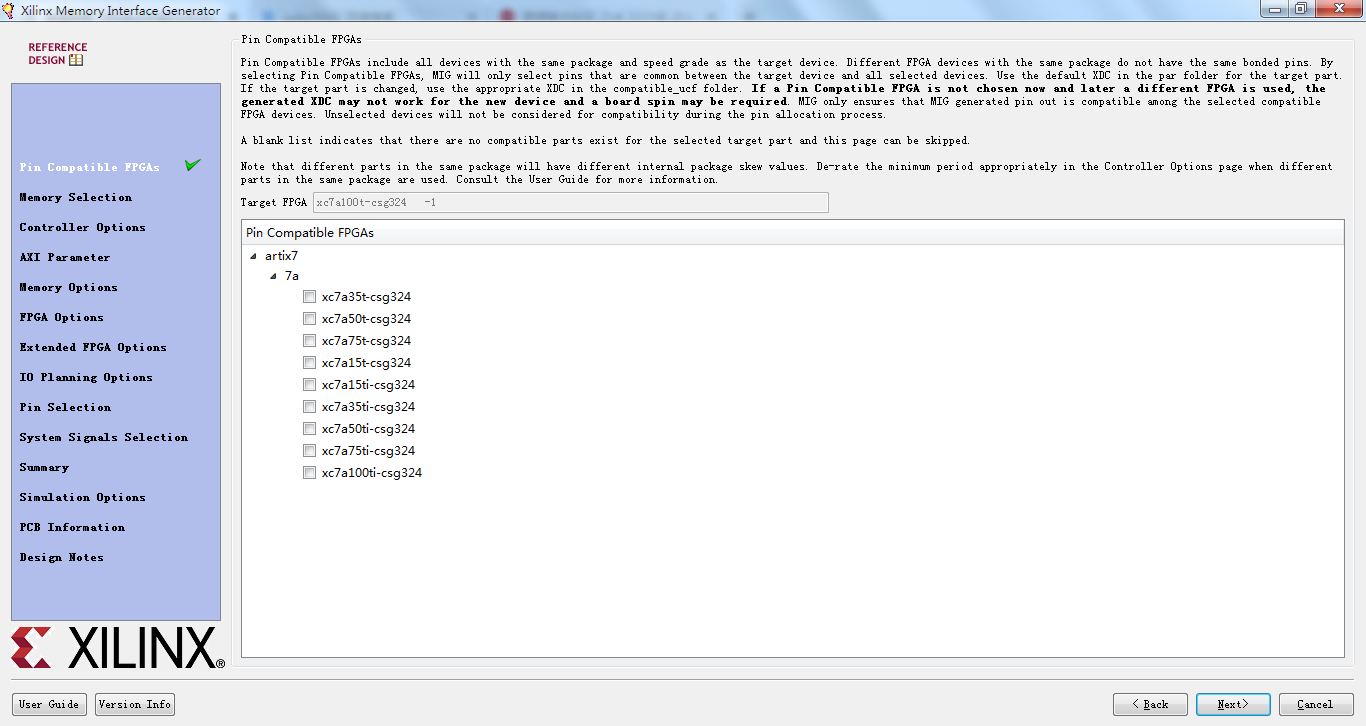

(4)器件引脚适配性选择,目前不需要,next:

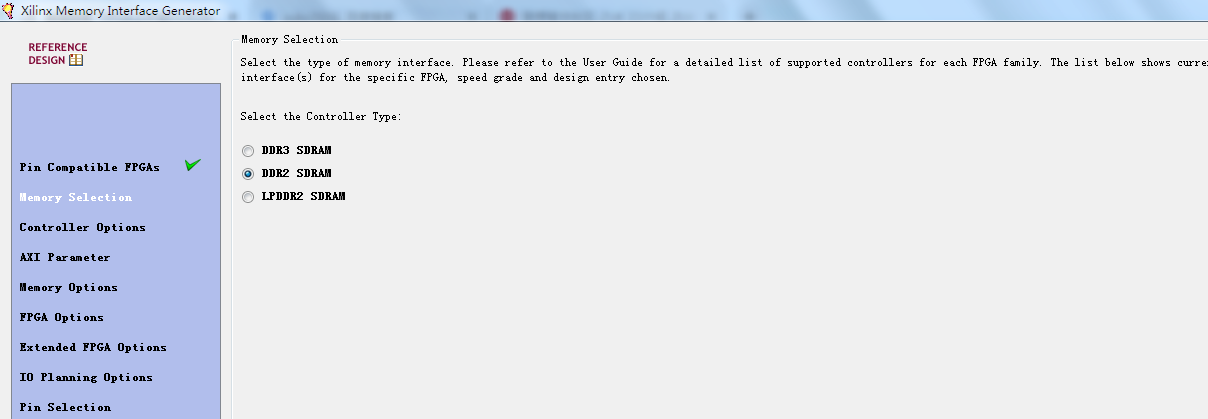

(5)选择DDR2类型,next:

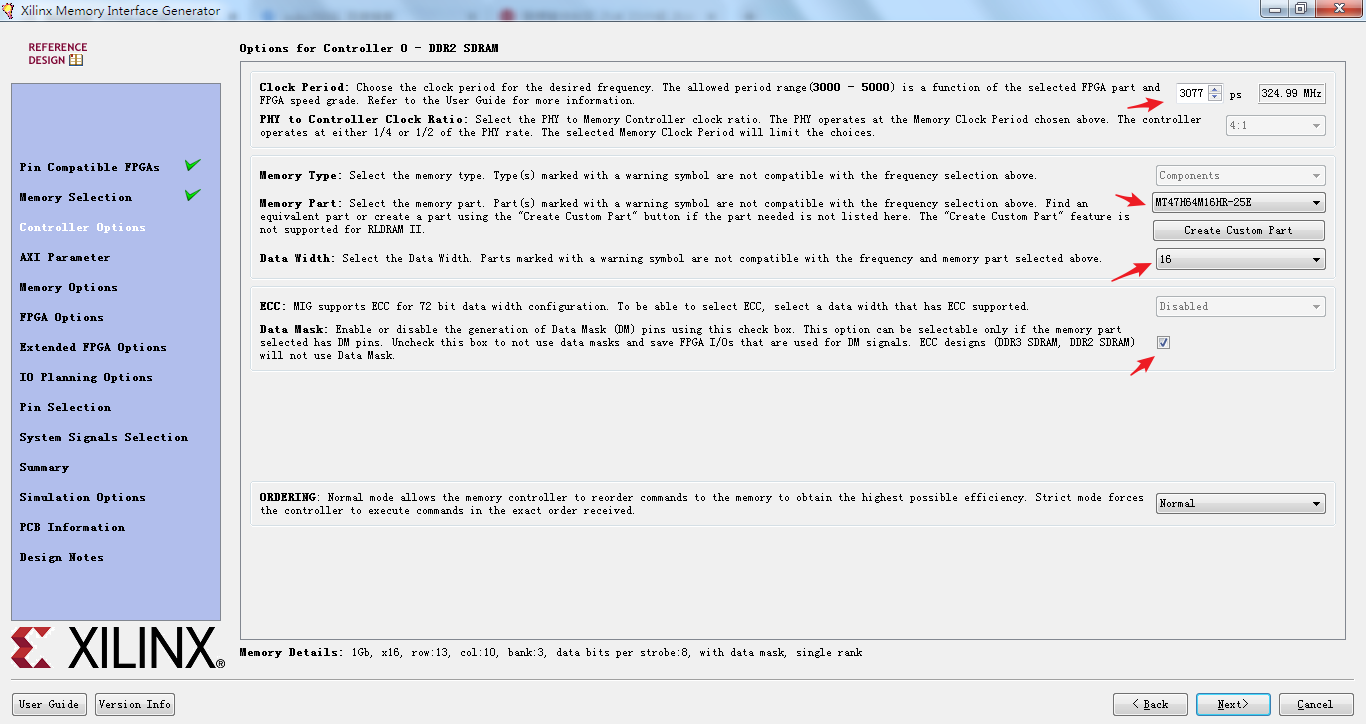

(6)clock period表示的是MIG IP的工作时钟,而DDR是双倍率,则对外接口部分的接口速率为X2,不同的器件可选择的范围是不一致的,如果选择为400M,那么接口速率为800M。

PHY to controller clock ratio:工作时钟和用户接口部分的时钟比,本质体现为ui_clk时钟。可能2:1是不可选的,下图中的4:1就表示clock period :ui_clk = 4:1;

然后选择数据位宽,本次选择为16bit则每次打出的数据为16bit,突发8的话,则rd和wr的data宽度为16*8=128bit。

本DDR2有数据掩模,选上,虽然目前没用到,next:

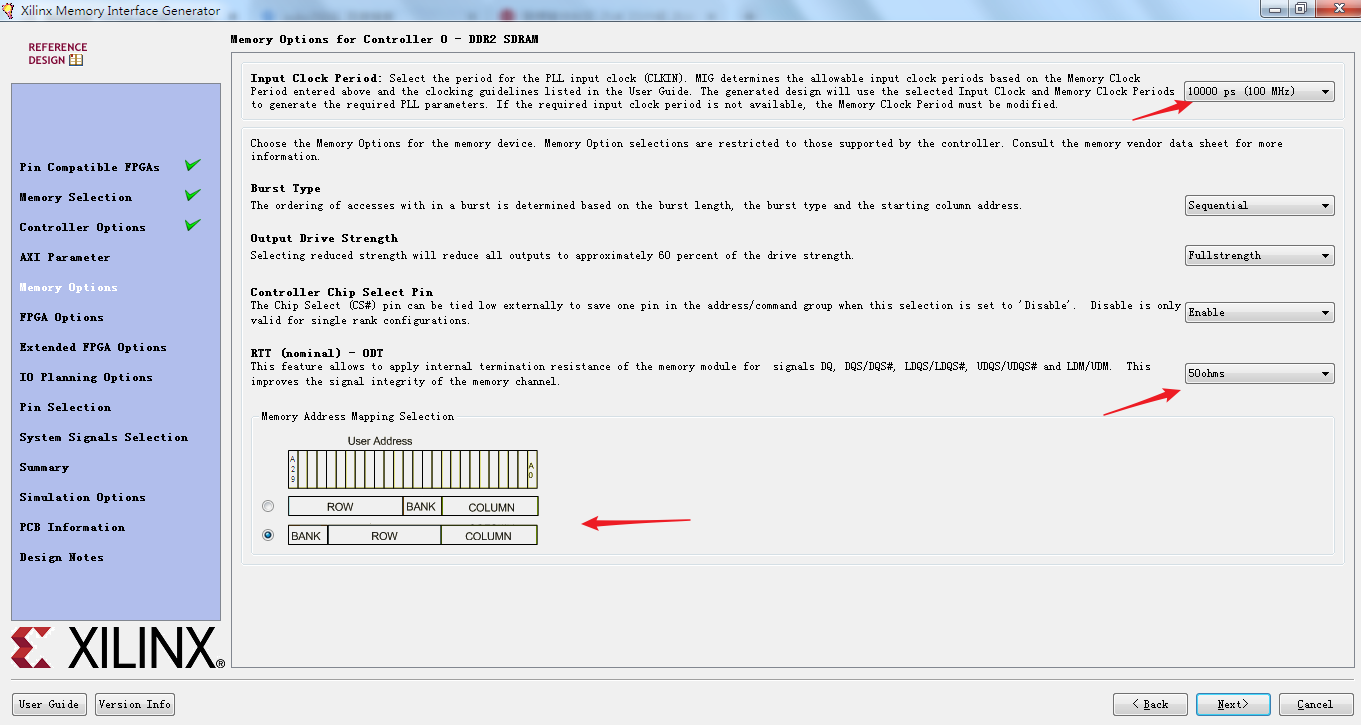

(7)选择input clock period,这是什么意思呢,如果简单起见,选择为200M,后面会有惊喜,推荐200M。你可以使用晶振的时钟或者内部时钟,后面得相关配置才能用。

选择ODT,板子文档说是50ohms,则选择此项。然后是地址映射,选择bank+row+column的方式,next:

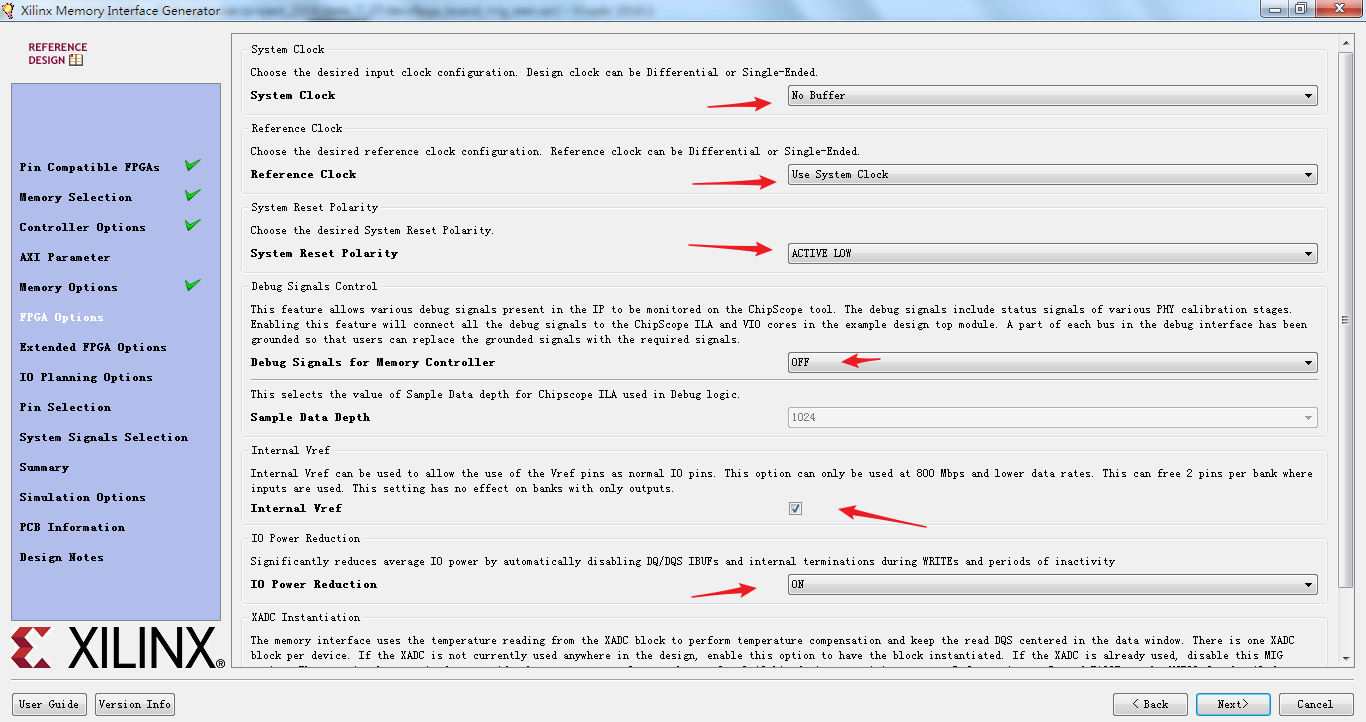

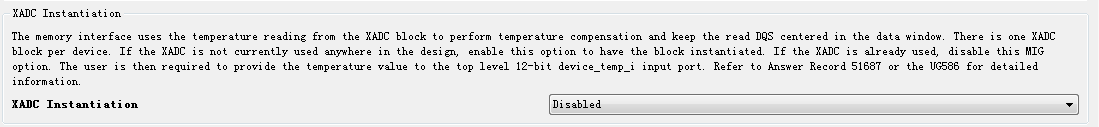

(8)系统时钟与参考时钟的极性选择,如果想用内部的时钟作为系统时钟和参考时钟,那么就选择no buffer选项,如果前面选择了200M系统时钟输入,那么参考时钟会多一个use system clock 的选项,也就是少给一个时钟,不然前面选择的不是200M时钟的话,参考时钟就会贴心的问你要200M时钟。想用PLL的输出作为system clk输入,那么选择no buffer项。参考时钟用use system clock。毕竟对于只有一个外部晶振的话,单独给mig ip就完犊子了,别的时钟不能再使用这个晶振时钟,为了多几个时钟使用,还是用PLL。况且有的板子晶振只有20M的话,你就没得选了,必须用PLL倍频灌入时钟。

debug信号不使用,内部参考引脚做普通输入脚使用,xdc啥的关掉。

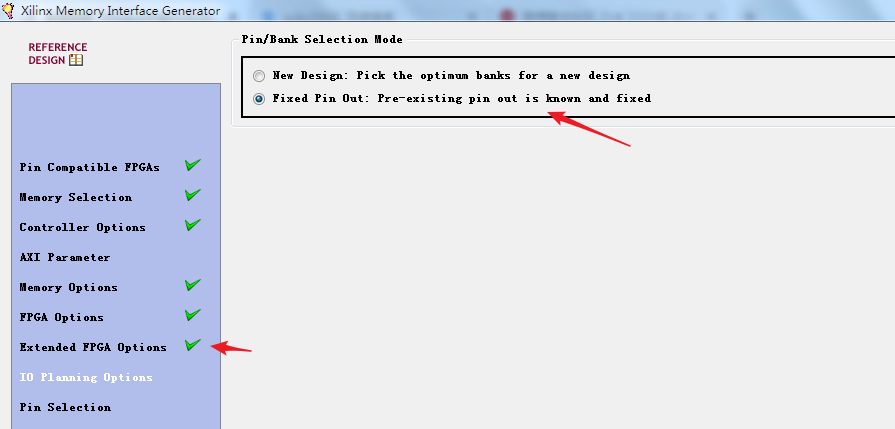

(9)如果有DDR2的引脚分配的,就选择Fixed Pin Out,开发板之类的一般带,自己画的板子就得照着原理图一个个分了,可能会瞎眼。

(10)选择你的引脚约束文件,导入并检查合理性,通过则next:

然后一路next,就可以生成MIG IP了。

/////////////////////////

2.怎么用IP自带的仿真呢?

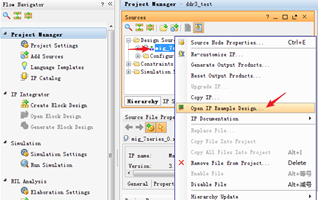

(1)现在我们就有了如下图所示的IP文件架构,右键IP选择打开IP example design,为了仿真使用。

在你的example设计中会有仿真顶层,在哪呢,我的在这,下面是ddr3举例:

E:kingstackerproject_2018date_7_23devmig_7series_0_examplemig_7series_0_example.srcssim_1importssim

这个目录下有什么文件呢:

ddr3_model.sv:DDR3的总线功能模型,相当于个ddr3芯片。

ddr3_model_parameters.vh:一堆模型的相关参数。

sim.do:modalism可用的do文件,不过不能直接使用得修改。

sim_tb_top.v:仿真顶层文件。

wiredly.v:仿真需要用的文件。

其他就没啥卵用了。

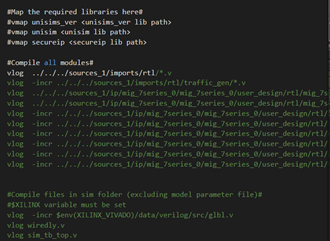

打开sim.do文件应该是下面这个样子,这放到modelsim仿真绝对是会出错的,所以需要修改相关路径。

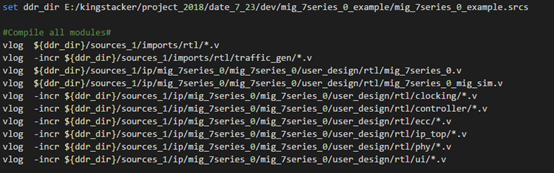

设置一下相关v文件的绝对路径:

修正glbl.v文件的路径,我这里用ISE的glbl文件也没问题。然后修正wiredly.v、sim_tb_top.v、ddr3_model.sv路径。

修改仿真精度fs为ps,加快仿真速度。修改相关库挂载,根据编译的名字修改。

然后就可以切换到sim.do文件所在的路径,do sim.do即可。

3.MIG核顶层文件调用:

生成IP后,我们所关心的就是整个IP的TOP层,下图中为mig_7series_0.v。打开它就可以看到相关的信号了。