目录

学习重点

- 主存扩容(扩展)

- cpu与主存连接

- 汉明码

- 提高访存速度

- 高速器件

- Cache

- 调整主存结构

1.存储器扩展

-

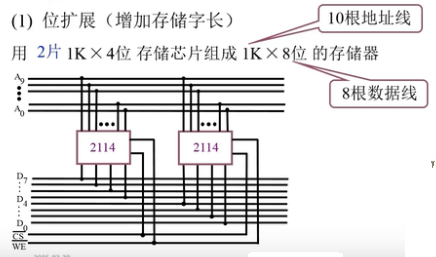

位扩展

- 增加存储字长(每个字的数据位)

- CS:片选信号线

- WE:读写信号线

-

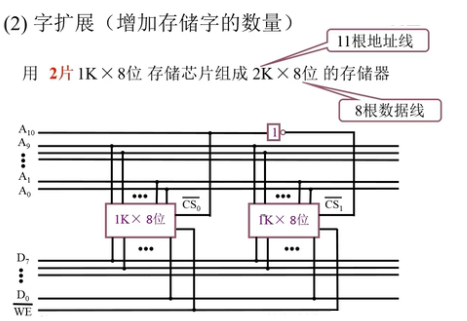

字扩展

- 增加字地址数量(地址数量)

-

字位同时扩展

- 同时扩展字数与字长

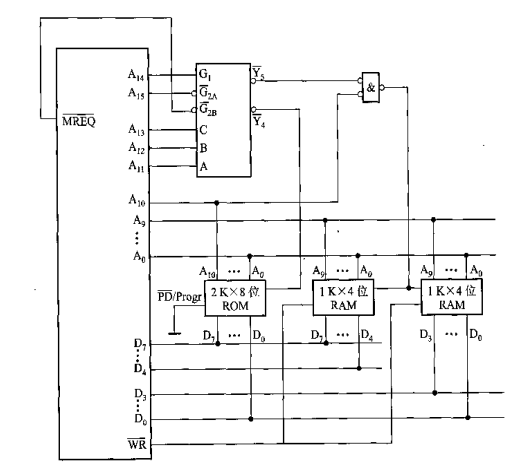

2.CPU与主存连接

- 74138译码器

- MREQ:cpu访存控制信号

- An:地址线

- Dn:数据线

- WE:读写命令线

- CS:片选信号线

- 只读存储器ROM没有读写命令线,可编程端接地

3.存储器校验(汉明码)

- 校验公式:

L-1=D+C(D>=C)- L:合法代码集中任意两个合法代码最小的二进制位差异

- 如000和111差3位,00000和10000差4位

- 合法代码集:合法的二进制编码集合

- D:检错位数

- C:纠错位数

- L:合法代码集中任意两个合法代码最小的二进制位差异

- 汉明码是具有一位纠错能力的编码,有如下特点

- 奇偶校验

- 奇校验:加一个校验位使1的个数为奇数个

- 偶校验:加一个校验位使1的个数为偶数个

- 分组校验

- 非划分方式: 有些位同时处于多个组

- 奇偶校验

- 汉明码分组:

第一组:第 XXXX1 位

第二组:第 XXX1X 位

第三组:第 XX1XX 位

第四组:第 X1XXX 位

第五组:第 1XXXX 位

以此类推 - 汉明码三要素:

-

添加校验位个数(n个检错位)

2^k>=n+k+1n:代码位数,k:多少检测位

-

检测位的位置

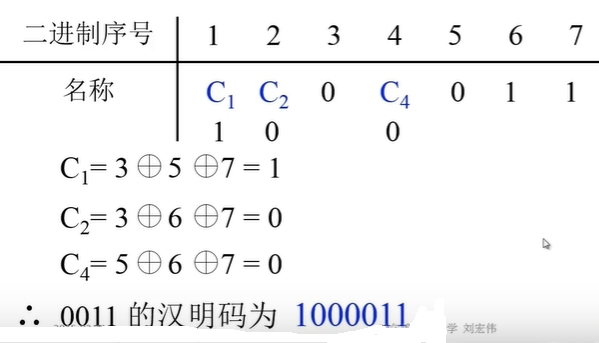

2^i(i=0,1,2,3....)- 如0011,需要添加3个检测位

示意图:(偶校验:1个数为偶数)

- 如0011,需要添加3个检测位

-

检测位取值

使组内1个数满足校验规则 -

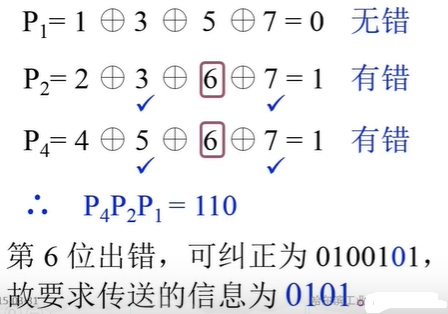

纠错过程: 接收到汉明码0100111,偶校验(仅纠一位错)

-

4.提高访存速度

采用高速器件

使用Cache

调整主存结构

-

调整主存结构

-

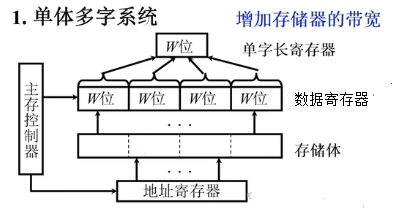

1)单体多字

实际取得和写入的是存储体中的数据 -

2)多体并行—高位交叉

顺序编址

缺点:集中访问,会导致某一存储体负载过大,不能提高访存速度(带宽),只能用作扩容

-

3)多体并行—低位交叉

不改变存储周期情况下提高带宽并扩容

-

-

高速芯片

- SDRAM:同步DRAM,cpu无需等待

- RDRAM:解决存储器带宽问题

- 带Cache的DRAM