学习重点

- 存储器分类(了解)

- 存储器层次

- 主存基本组成

- 主存编址

- 半导体存储芯片

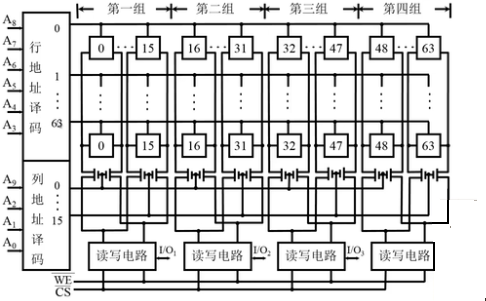

- 示意图

- 译码驱动方式

- RAM:随机存取存储器

- SRAM:静态RAM

- DRAM:动态RAM

- 三管和单管

- 刷新

- ROM:只读存储器

1.存储器分类

冯诺依曼结构计算机性能瓶颈:运算器速度

演变为以存储器为中心

-

按存储介质:

- 半导体存储器:TTL,MOS(易失)

- 磁表面存储器

- 磁芯存储器

- 光盘存储器

-

按存取方式分

- 存取时间与物理地址无关:(随机访问)

- 随机访问存储器:程序执行过程中可读可写(RAM)

- 只读存储器:程序执行过程中只读(ROM)

- 存取时间与物理地址有关:(顺序存储)

- 顺序存取存储器——磁带

- 直接存取存储器——磁盘

- 存取时间与物理地址无关:(随机访问)

-

按在计算机中的作用分类

存储器

├── 主存储器

│ ├── RAM

│ │ ├── 静态RAM (SRAM)

│ │ └── 动态RAM(DRAM)

│ ├── R0M

│ │ ├── MROM

│ │ ├── PROM 可编程

│ │ ├── EPROM 可擦写编程

│ │ └──EEPROM 电可擦写编程

├── FLASH MEMORY 闪存:SSD

├── 高速缓冲存储器:Cache

└──辅助存储器

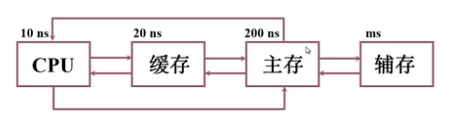

2.存储器层次

-

层次结构

-

缓存-主存和主存-辅存

- 缓存—主存:追求速度,硬件结合

- 主存—辅存:追求容量,软硬件结合

- 主存+辅存:虚拟存储器,虚地址,逻辑地址

- 主存:实地址,物理地址

3. 主存储器

-

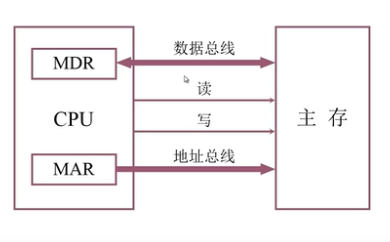

基本组成:

-

主存与CPU关系:

MAR与MDR现在多集成在cpu中

-

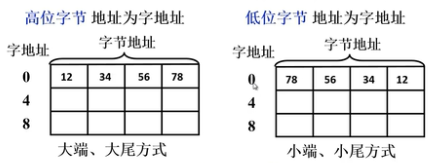

主存中存储单元地址分配(编址):

- 设地址线24根

- 按字节寻址,16MB

- 字长为16位(2字节),按字寻址,8MW(8M字)

- 字长位32位,按字寻址,4MW

-

主存技术指标

- 主存容量:主存内存放二进制代码总位数

- 存储速度:

- 存取时间:存储器的访问时间(访存),读出时间,写入时间

- 存取周期:连续两次独立的存储器操作所需的最小时间间隔

- 存储器带宽: 单位时间内读写数据量(位/秒)

4.半导体存储芯片

-

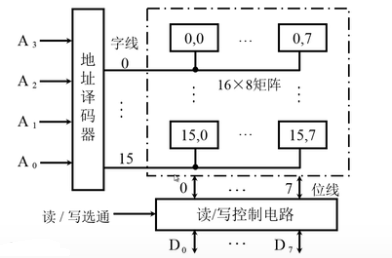

示意图:

-

地址线10位,数据线8位:

芯片容量=2^地址位*数据位=2^10*8位 -

例:

用16k*1位的存储芯片组成64k*8位的存储器,需要的个数:16k*1位的存储芯片:4根地址线,一根数据线64k*8位存储芯片:6根地址线,8根数据线- 需要

8/1*64/16=32片

4.1 译码驱动方式

- 译码:编码—>数据(二进制—>十进制)

- 线选法:

- 不适合容量大的芯片

- 每一行是存储单元,共16行,8列,

- 地址译码器选择哪一行

- 读写控制电路选择哪一列

- 重合法:

- 数据线只有1位,存储单元1位

- Y0前面的是MOS管,相当于开关,短端通电,长端才能连通

5.RAM

随机存取存储器

5.1 SRAM

静态RAM,使用触发器保存0,1

-

基本电路:(六管静态RAM)

- A:触发器原端

- A*:触发器非端

- T5,T6:行开关

- T7,T8:列开关

-

读写操作:根据电路分析

- 读操作:

- 行选T5,T6开,列选T7,T8开

- VA—>T6—>T8—>读放—>Dout

- 写操作:

- DIN—>两个写放—>经过开关存入触发器(两端相反)

- 左端放大器的圈是取反

- 读操作:

-

例:Intel2114芯片 (64*64)

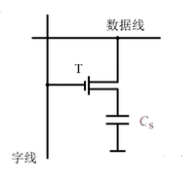

5.2 DRAM

动态RAM,通过电容保存0,1

-

基本单元电路:

-

三管DRAM

- 读:读数据线数据与电容中相反

- 写:写数据线数据与电容中相同

- T4充电,VDD给读数据线充电为1(高电平),读选择线有效,T2导通,Cg存0,T1不通,读数据线为1,Cg存1,T1通,读线接地,为0,读出与写入数据相反

-

单管DRAM

- 读出时数据线有电流为1(Cg内有电)

- 写入时:Cg充电为1,放电为0

- 字线选择的是字地址

-

-

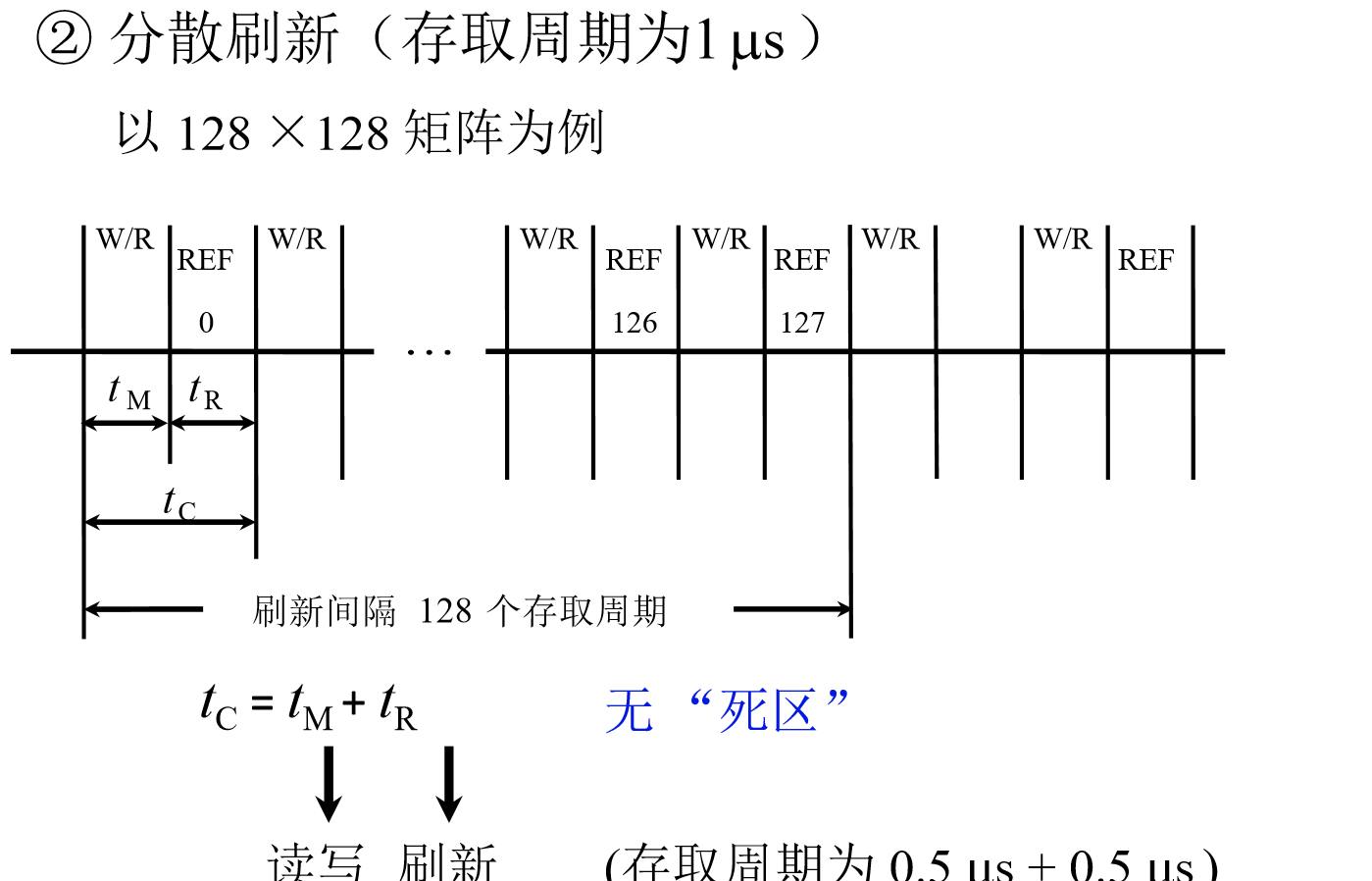

DRAM刷新:(电容易丢失)

刷新与行地址有关,以128*128为例

按行刷新,要刷新128次(2ms内)

刷新时间必须小于栅极电容自然保持信息的时间(小于2ms)-

集中刷新:

有64微秒没有读写操作,死区

-

分散刷新:

每次读写都刷新一次(2ms内刷新了200次)

无死区,但是存储周期增加了1倍,影响性能 -

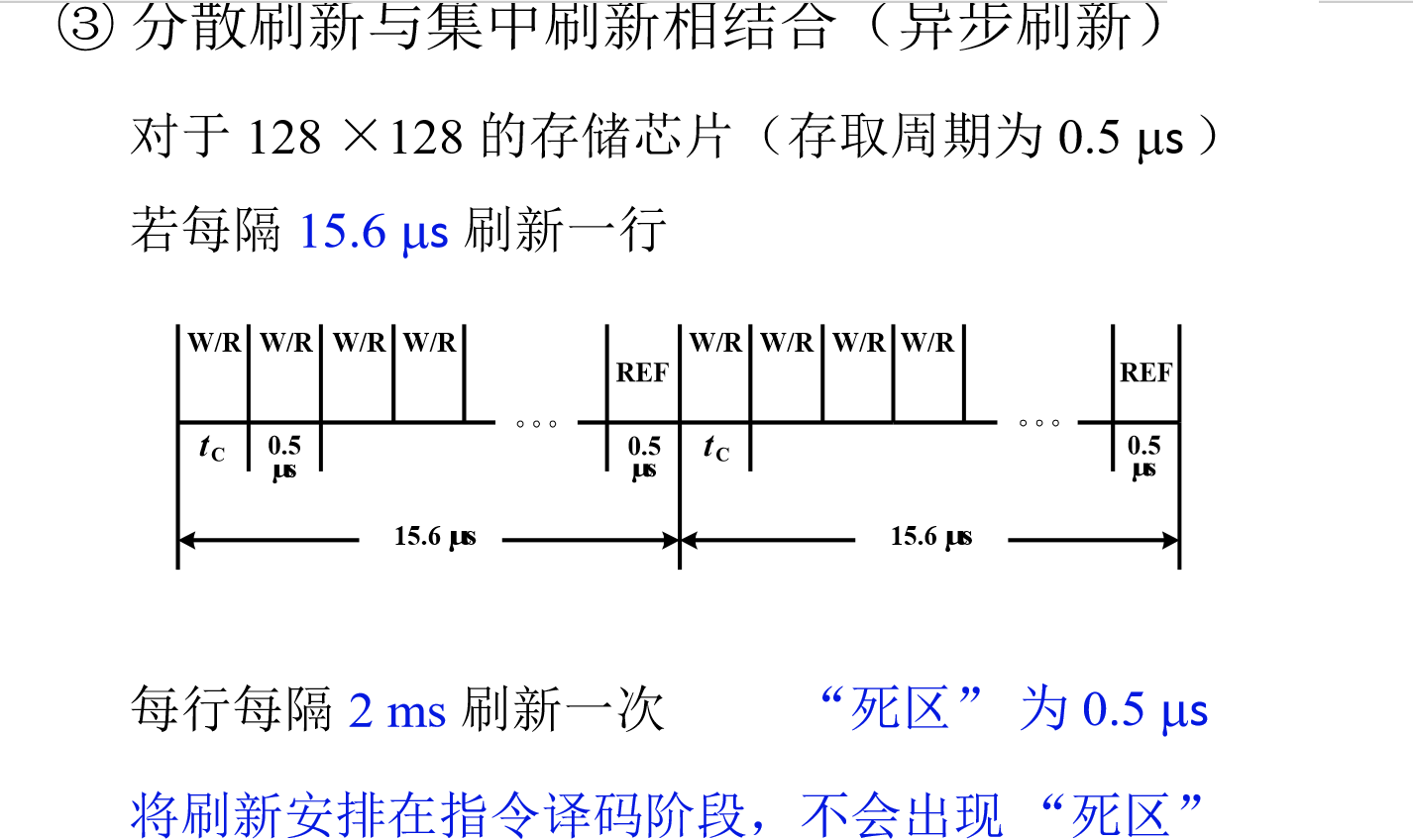

异步刷新:

- 2000/128=15.6

-

5.3 DRAM与SRAM比较

6.ROM

只读存储器,保存系统数据和配置信息

-

发展:

只读—>用户可一次性写—>可多次写—>电可擦写(专用设备)—>电可擦写(可连计算机) -

分类:

- 电模ROM:MROM,无法修改

- PROM:破坏性编程(一次性写)

- EPROM:多次编程,可擦写(紫外线擦除)

- EEPROM:电可擦写

- FLASH MEMORY:闪存SSD(固态硬盘)

比EEPROM性能好,已具备RAM功能