参考 http://blog.chinaunix.net/uid-20528014-id-3050217.html

19.1 硬件原理

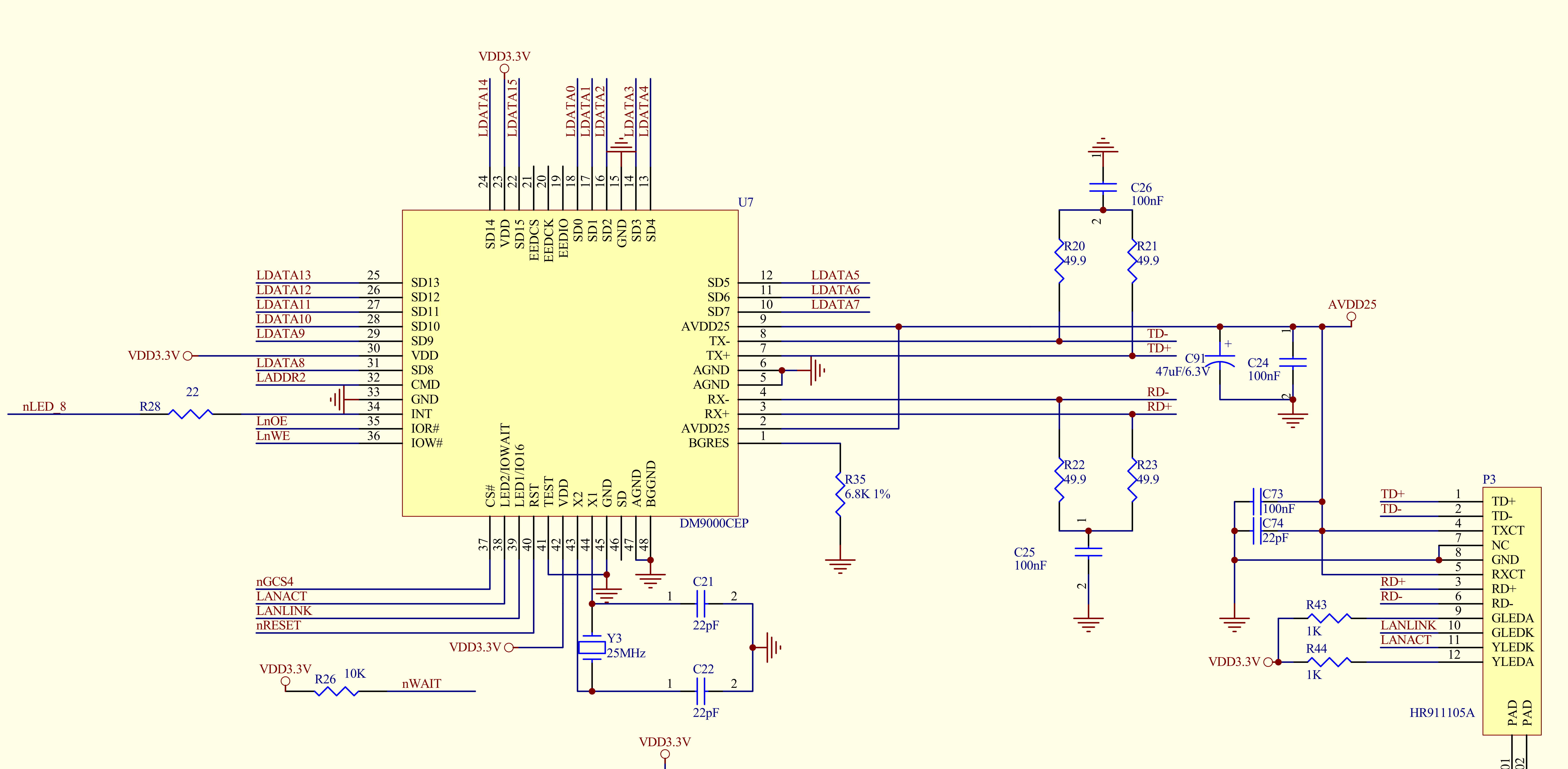

19.1.1 原理图

芯片型号是 DM9000CEP,电源是3.3V 供电,HR911105A 是网口座子,网卡芯片采用 25MHz 外部晶振提供时序。

各引脚说明:

| 分类 | 引脚名 | 说明 |

| 处理器接口 | IOR# |

处理器读命令 默认是低电平有效,但是极性能够被 EEPROM 修改 |

| IOW# |

处理器写命令 默认是低电平有效,但是极性能够被 EEPROM 修改 |

|

| CS# |

片选 默认是低电平有效,但是极性能够被 EEPROM 修改 |

|

| CMD |

命令类型 高电平是访问数据端口,低点平是访问地址端口 |

|

| INT |

中断请求信号 默认高电平有效,但是极性能够被 EEPROM 或 EECK引脚 修改 |

|

| SD0~7 | 处理器数据总线 0~7 | |

| SD08~15 |

处理器数据总线 8~15 在 16 位模式下,这些引脚被作为数据位 8~15。当 EECS 引脚被上拉时,这些引脚另作它用。详细需要参看对 8 位模式引脚的描述 |

|

| 8 位引脚模式 | WAKE(SD15) | 当唤醒事件发生时,输出一个唤醒信号 |

| LED3(SD14) |

全双工 LED 在 LED 模式 1,低电平输出代表内部 PHY 工作在全双工模式,悬空表示内部 PHY 工作在半双工模式 在 LED 模式 0,它低电平输出代表内部 PHY 工作在 10M 模式,悬空表示内部 PHY 工作在 100M 模式 |

|

|

GP6, GP5, GP4 (SD13 ~ SD11) |

通用输出引脚 这些引脚可在寄存器 GPR(1FH) 中设置用于通用目的输出引脚。这些引脚默认位输出 GP6 引脚也可作为 INT 输出类型的捆绑引脚; 当 GP6 被置高,INT 作为开漏输出类型,否则作为强制输出类型 |

|

|

GP3, GP2, GP1 (SD10 ~ SD8) |

通用 I/O 引脚 寄存器 GPCR 和 GPR 可以编程这些引脚,这些引脚默认为输入。 |

|

| EERPOM 接口 | EEDIO | EEPROM 数据输入、输出引脚 |

| EECK |

EEPROM 时钟信号 该引脚也被用于中断极性的设置。当这个引脚为上拉高电平时,中断低有效,否则中断引脚高有效。 |

|

| EECS |

EERPOM 片选信号 该引脚也被用于设置内部存储器数据总线宽度。当引脚为上拉高电平时,总线为 8 位,否则为 16位 |

|

| 时钟引脚 | X2 | 25M 晶振输出 |

| X1 | 25M 晶振输入 | |

| LED 接口 | LED1 |

速度 LED 低电平输出表示内部 PHY 工作于 100M/S 的速率下,悬空表示内部 PHY 工作于 10M/S 的速率下。 该引脚可以在 16 位模式下作为 ISA 总线 IO16(在 EERPOM 中设置) |

| LED2 |

连接/运行 LED 在 LED 模式1, 它作为 PHY 链路通断和载波侦测的公用灯 在 LED 模式0,它作为 PHY 载波侦测的专用灯 该引脚可以在 16 位模式下 作为 ISA IOWAIT 或者 WAKE(在 EERPOM 里设置) |

|

| 10/100 PHY/Fiber | SD |

光纤信号检测 PECL 电平信号,显示光纤接收是否有效 |

| BGGND | 能带隙地信号 | |

| BGRES | 能带隙引脚 | |

| RXVDD18 | 1.8V 接收端口电源 | |

| TXVDD18 | 1.8V 发送端口电源 | |

| RXI+ | 物理层接收端的正极 | |

| RXI- | 物理层接收端的负极 | |

| RXGND | 接收端口地 | |

| TXGND | 发送端口地 | |

| TX+ | 物理层发送端口正极 | |

| TX- | 物理层发送端口负极 | |

| 其他 | TEST |

操作模式 在正常模式时被强制置接地 |

| PWRST# |

复位信号; 复位 DM9000,低电平有效;该引脚被置后,DM9000 将在 5us 完成初始化 |

|

| 电源引脚 | VDD |

数字电源 3.3V 电源输入 |

| GND | 数字地 | |

|

捆绑引脚列表 1:上拉 1K~10K 0:悬空 |

EECK |

中断极性 1,中断引脚低有效,0,中断引脚高有效 |

| EECS |

数据宽度 1:8位;0:16位 |

|

| GP6 |

在 8 位模式下,INT 引脚输出类型 1:开漏输出;0:强制输出 |

通过引脚定义,再查看原理图可以知道,

- EEDCS 引脚即 EECS 为空,那么我们的数据位宽为 16位

- EEDCK 悬空,中断高电平有效

- 输入电源位 3.3V,网口电源位 AVDD25 为2.5 V

- CS# 接在 S3C2440 的 nGCS4 上,DM9000 的在 S3C2440 上的存储器控制器物理地址为 0x20000000

- CMD 引脚接在 LADDR2 上,即 S3C2440 的ADDR2 上,用来让 S3C2440 控制访问 DM9000的数据还是地址

- IOR# 和 IOW# 与 S3C2440 的 nOE 和 nWE 相连,控制 DM9000的读写

- LED2 和 LED1 以及 RST 有由 S3C2440 进行控制

19.1.2 DM9000CEP 说明

DM9000CEP 是一款完全集成的和符合成本效益单芯片快速以太网MAC控制器与一般处理接口,一个10/100M 自适应的 PHY 和 4K DWORD 值的 SRAM 。它的目的是在低功耗和高性能进程的 3.3V 与 5V 的支持宽容。

DM9000CEP 还提供了介质无关的接口,来连接所有提供支持介质无关接口功能的家用电话线网络设备或其他收发器。该 DM9000CEP 支持 8 位, 16 位和 32 位接口访问内部存储器,以支持不同的处理器。DM9000cep 物理协议层接口完全支持使用 10MBps 下 3 类、4 类、5 类非屏蔽双绞线和 100MBps 下 5 类非屏蔽双绞线。这是完全符合 IEEE 802.3u 规格。它的自动协调功能将自动完成配置以最大限度地适合其线路带宽。还支持 IEEE 802.3x 全双工流量控制。这个工作里面 DM9000CEP 是非常简单的,所以用户可以容易的移植任何系统下的端口驱动程序。

- 特性

- 支持处理器读写内部存储器的数据操作命令以 字节/ 字/ 双字的长度进行

- 集成10/100M自适应收发器

- 支持背压模式半双工流量控制模式

- IEEE802.3x流量控制的全双工模式

- 支持唤醒帧,链路状态改变和远程的唤醒

- 支持 100M 光纤接口

- 集成了 16K 字节大小的 SRAM

- 3.3V ~ 1.8V 的参考电压

- 支持早期的传输

- 支持 IP/TCP/UDP 校验码的生成和校验

- 支持自动从 EEPROM 中加载 vendor ID 和 product ID

- 可选的 EEPROM 配置

- 低功耗模式

- 低功耗模式(由电缆检测)

- 掉电模式

- 可选择1:1 YL18-2050s YT37-1107S或5:4变压比例的变压器降低格外功率

- 兼容 3.3V~5.0V I/O 电源

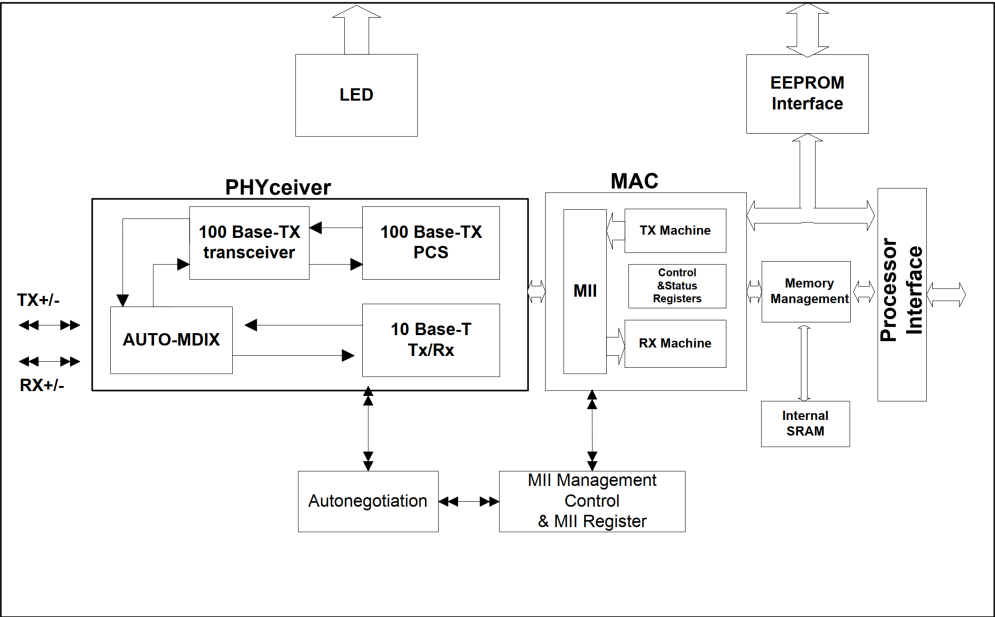

19.2 硬件框图分析

DM9000C 的硬件框图如下所示:

芯片内部主要有 PHY 和 MAC 两个功能模块,PHY 负责物理层,MAC 负责数据链路层。

MAC 和 PHY 之间采用 MII 连接。

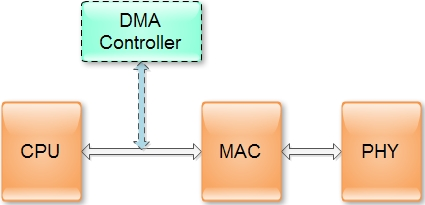

一般来说 CPU 和 MAC 和 PHY 之间的连接如下图所示:

对于上面的三部分,并不一定都是独立的芯片,根据组合形式,可分为下列几种类型:

- CPU 集成 MAC 和 PHY

- CPU 集成 MAC,PHY 采用独立芯片

- CPU 不集成 MAC 与 PHY,MAC 与 PHY 采用集成芯片

我们采用的 DM9000C 集成了 MAC 和 PHY,在外部通过接口与 CPU DMA 控制器相连。

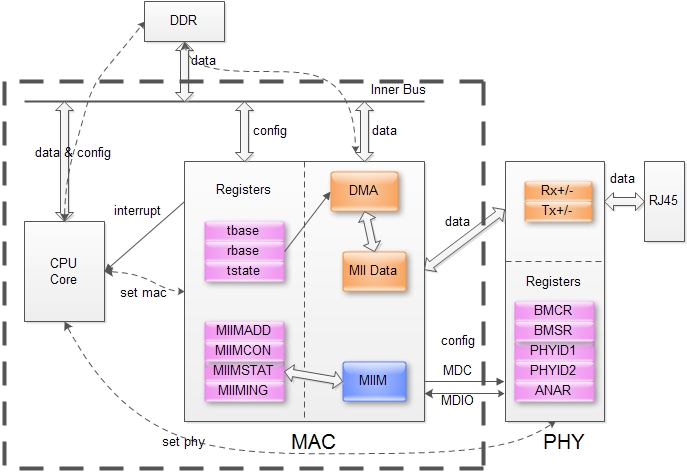

18.2.1 MII

虽然 MII 在 DM9000C 中不可见,但是还是有必要去了解此总线。

当采用 CPU 集成 MAC,PHY 采用独立芯片的时候,PHY 芯片通过 MII 接口与 CPU 上的 MAC 连接。

软件上对网口的操作通常分为下面几步:

- 为数据收发分配内存

- 初始化 MAC 寄存器

- 初始化 PHY 寄存器(通过 MIIM)

- 启动收发

MII 接口是 MAC 与 PHY 连接的标准接口。因为各厂家采用了同样的接口,用户可以根据所需的性能、价格,采用不同型号,甚至不同公司的phy芯片。

需要发送的数据通过 MII 接口中的收发两组总线实现。而对 PHY 芯片寄存器的配置信息,则通过 MII 总的一组串口总线实现,即MIIM(MII Management)。

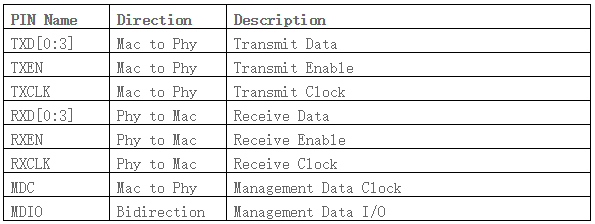

MII 总线中的主要引脚有:

MIIM 只有两个线,时钟信号 MDC 与数据线 MDIO。读写命令均由 Mac 发起,PHY 不能通过 MIIM 主动向 Mac 发送信息。由于 MIIM 只能有 Mac 发起,我们可以操作的也就只有 MAC 上的寄存器。

19.2.2 MAC

MAC 即 Media Access Control,即媒体访问控制子层协议。该协议位于 OSI 七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。在发送数据的时候,MAC 协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层;在接收数据的时候,MAC 协议首先判断输入的信息并是否发生传输错误,如果没有错误,则去掉控制信息发送至 LLC 层。该层协议是以太网 MAC 由 IEEE-802.3 以太网标准定义。

以太网数据链路层其实包含 MAC(介质访问控制)子层和 LLC(逻辑链路控制)子层。一块以太网卡 MAC 芯片的作用要实现 MAC 子层和 LLC 子层的功能。

以太网 MAC 芯片的一端接 ARM 总线,另外一端就接到 PHY 芯片上。以太网的物理层又包括 MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。而PHY芯片是实现物理层的重要功能器件之一,实现了前面物理层的所有的子层的功能。

19.2.3 PHY

PHY 在发送数据的时候,收到 MAC 过来的数据(对 PHY 来说,没有帧的概念,对它来说,都是数据而不管什么地址,数据还是 CRC),每 4bit 就增加 1bit 的检错码,然后把并行数据转化为串行流数据,再按照物理层的编码规则(10Based-T的NRZ编码或100based-T的曼彻斯特编码)把数据编码,再变为模拟信号把数据送出去。

收数据时的流程反之。

PHY还有个重要的功能就是实现 CSMA/CD的 部分功能。它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去。如果两块网卡碰巧同时送出了数据,那样必将造成冲突,这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据。

这个随机时间很有讲究的,并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付出现概率很低的同两台主机之间的第二次冲突。

PHY 和 MAC 之间是如何传送数据和相互沟通的。通过 IEEE 定义的标准的 MII/GigaMII(Media Independed Interfade,介质独立界面)接口连接 MAC 和 PHY。这个界面是 IEEE 定义的。MII 接口传递了网络的所有数据和数据的控制。

而 MAC 对 PHY 的工作状态的确定和对 PHY 的控制则是使用 SMI(Serial Management Interface)接口通过读写 PHY 的寄存器来完成的。PHY 里面的部分寄存器也是 IEEE 定义的,这样 PHY 把自己的目前的状态反映到寄存器里面,MAC 通过 SMI 总线不断的读取 PHY 的状态寄存器以得知目前 PHY 的状态,例如连接速度,双工的能力等。当然也可以通过 SMI 设置 PHY 的寄存器达到控制的目的,例如流控的打开关闭,自协商模式还是强制模式等。

不论是物理连接的 MII 接口和 SMI 总线还是 PHY 的状态寄存器和控制寄存器都是有 IEEE 的规范的,因此不同公司的 MAC 和 PHY 一样可以协调工作。当然为了配合不同公司的 PHY 的自己特有的一些功能,驱动需要做相应的修改。