最近再singaltap上探索了FIFO的wrreq和rdreq与q之间的关系问题,详情如下:

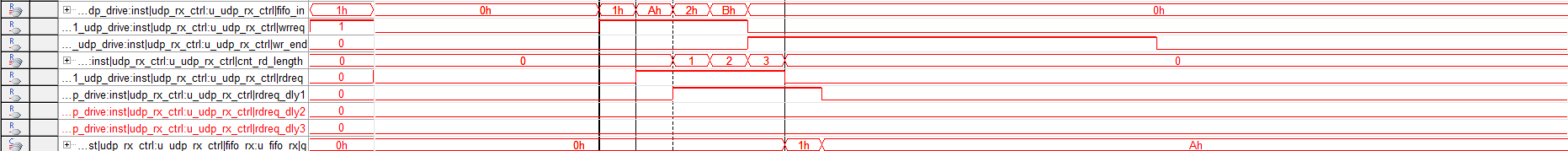

a. 读使能(rdreq)与wrreq间隔1个时钟周期时,输出q的情况:

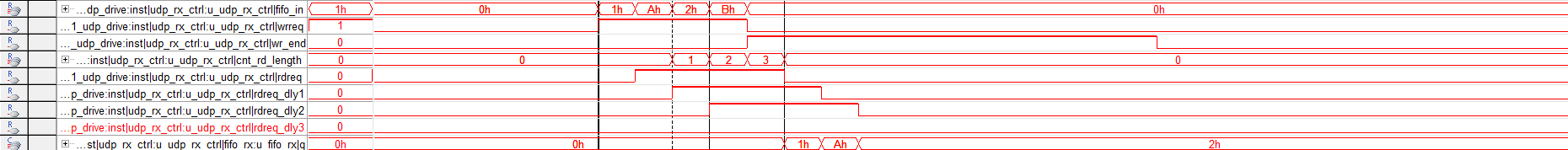

b. 读使能(rdreq_dly1)与wrreq间隔2个时钟周期时,输出q的情况:

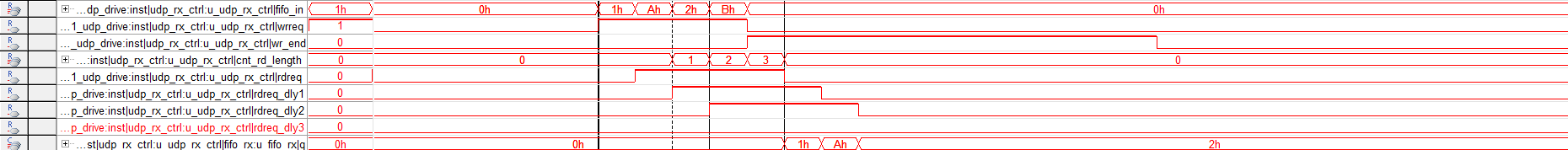

c. 读使能(rdreq_dly2)与wrreq间隔3个时钟周期时,输出q的情况:

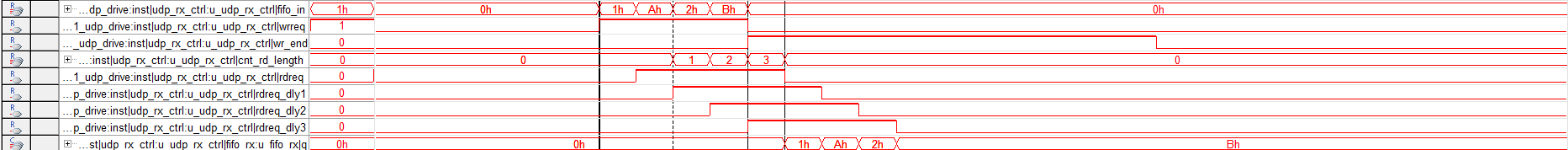

d. 读使能(rdreq_dly3)与wrreq间隔4个时钟周期时,输出q的情况:

总结:

不管FIFO的输入多少数据(这里不给予证明),当wrreq为高电平时,输出q与wrreq之间的间隔时钟是5个clock的时间间隔,由此推出rdreq至少应与wrreq间隔4个时钟周期,否则输出会错误。