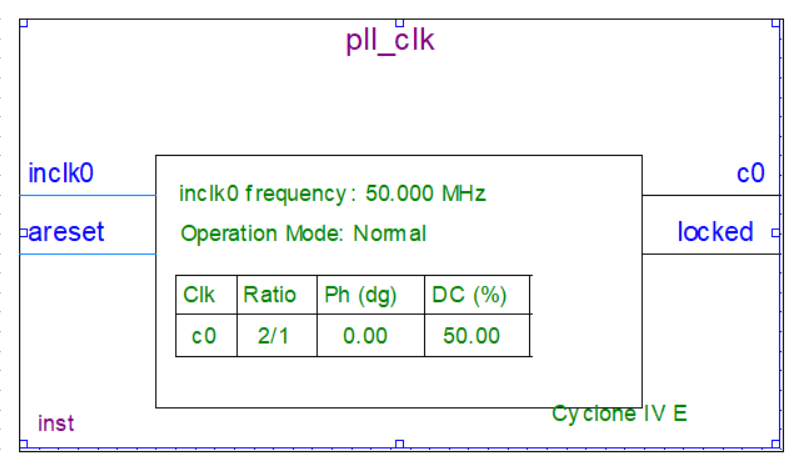

先说明一下pll的端口功能,原理图如下:

| 端口 | 位宽 | 输入/输出 | 说明 |

| inclk0 | 1 | input | 时钟50M(初始时钟) |

| areest | 1 | input | pll复位信号,高电平有效 |

| c0 | 1 | output | 倍频后的时钟,这里设置成了100M |

| locked | 1 | output | 判断pll是否已锁定(稳定)信号,高电平有效。(信号独立) |

带有pll的异步复位,同步释放的方式有两种:(输出Q为同步处理后的全局复位)

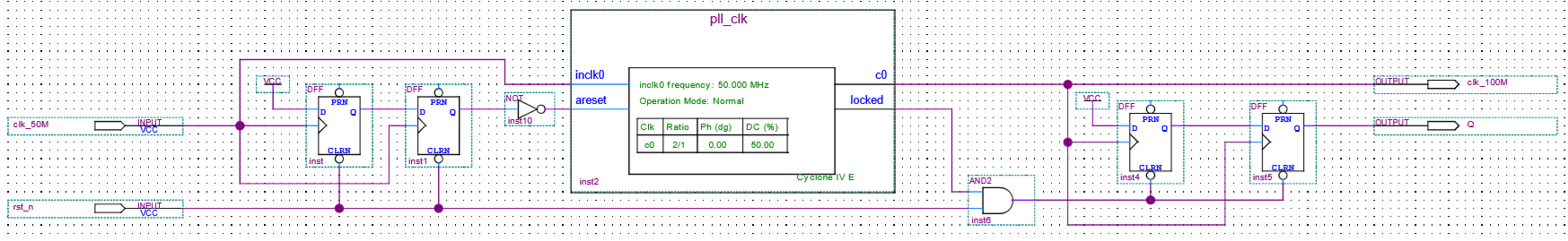

第一种原理图、代码和RTL图如下:

1 module sys_ctrl( 2 input clk_50M, 3 input rst_n, 4 output clk_100M, 5 output reg syn_rst_n 6 ); 7 8 reg rst_dly_1; 9 reg syn_rst_1; 10 reg com_rst_dly_1; 11 wire locked; 12 wire com_rst; 13 14 15 always@(posedge clk_50M or negedge rst_n) 16 begin 17 if(rst_n == 1'b0)begin 18 rst_dly_1 <= 1'b0; 19 syn_rst_1 <= 1'b0; 20 end 21 else begin 22 rst_dly_1 <= 1'b1; 23 syn_rst_1 <= rst_dly_1; 24 end 25 end 26 27 assign com_rst = rst_n & locked; 28 29 30 always@(posedge clk_100M or negedge com_rst) 31 begin 32 if(com_rst == 1'b0)begin 33 com_rst_dly_1 <= 1'b0; 34 syn_rst_n <= 1'b0; 35 end 36 else begin 37 com_rst_dly_1 <= 1'b1; 38 syn_rst_n <= com_rst_dly_1; 39 end 40 end 41 42 43 pll_clk u_pll_clk( 44 .inclk0 (clk_50M), 45 .areset (!syn_rst_1), 46 .c0 (clk_100M), 47 .locked (locked) 48 ); 49 50 endmodule

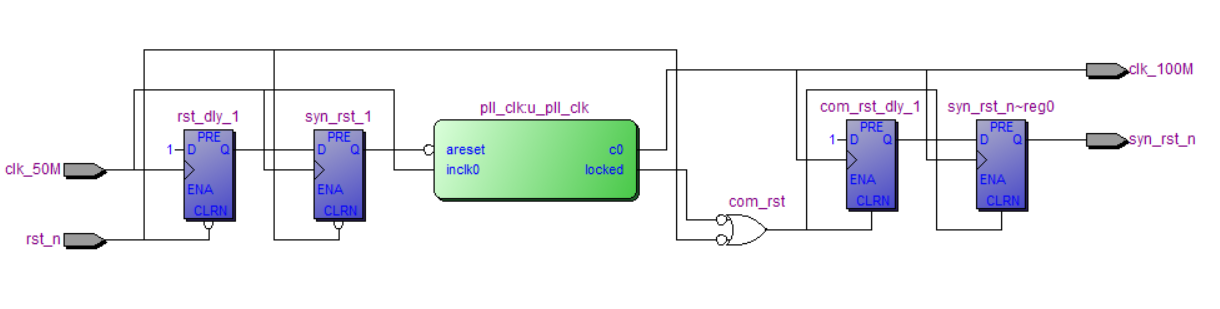

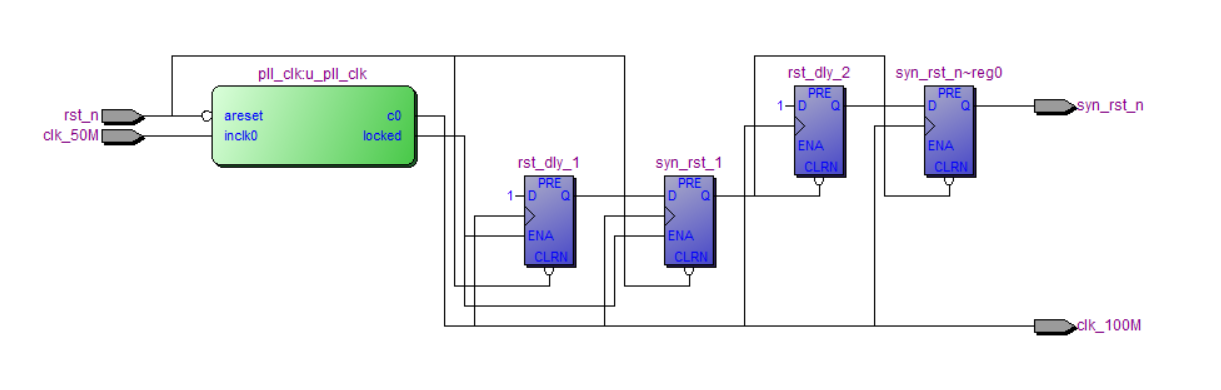

第二种原理图、代码和RTL图如下:

1 module sys_ctrl( 2 input clk_50M, 3 input rst_n, 4 output clk_100M, 5 output reg syn_rst_n 6 ); 7 8 reg rst_dly_1; 9 reg syn_rst_1; 10 reg rst_dly_2; 11 wire locked; 12 13 always@(posedge clk_100M or negedge rst_n) 14 begin 15 if(rst_n == 1'b0)begin 16 rst_dly_1 <= 1'b0; 17 syn_rst_1 <= 1'b0; 18 end 19 else begin 20 if(locked == 1'b1)begin 21 rst_dly_1 <= 1'b1; 22 syn_rst_1 <= rst_dly_1; 23 end 24 else begin 25 rst_dly_1 <= rst_dly_1; 26 syn_rst_1 <= syn_rst_1; 27 end 28 end 29 end 30 31 always@(posedge clk_100M or negedge syn_rst_1) 32 begin 33 if(syn_rst_1 == 1'b0)begin 34 rst_dly_2 <= 1'b0; 35 syn_rst_n <= 1'b0; 36 end 37 else begin 38 rst_dly_2 <= 1'b1; 39 syn_rst_n <= rst_dly_2; 40 end 41 end 42 43 pll_clk u_pll_clk( 44 .inclk0 (clk_50M), 45 .areset (!rst_n), 46 .c0 (clk_100M), 47 .locked (locked) 48 ); 49 50 51 endmodule

第二种方式的寄存器用的是带有使能端,它同时受到locked信号信号的控制,高点评有效。

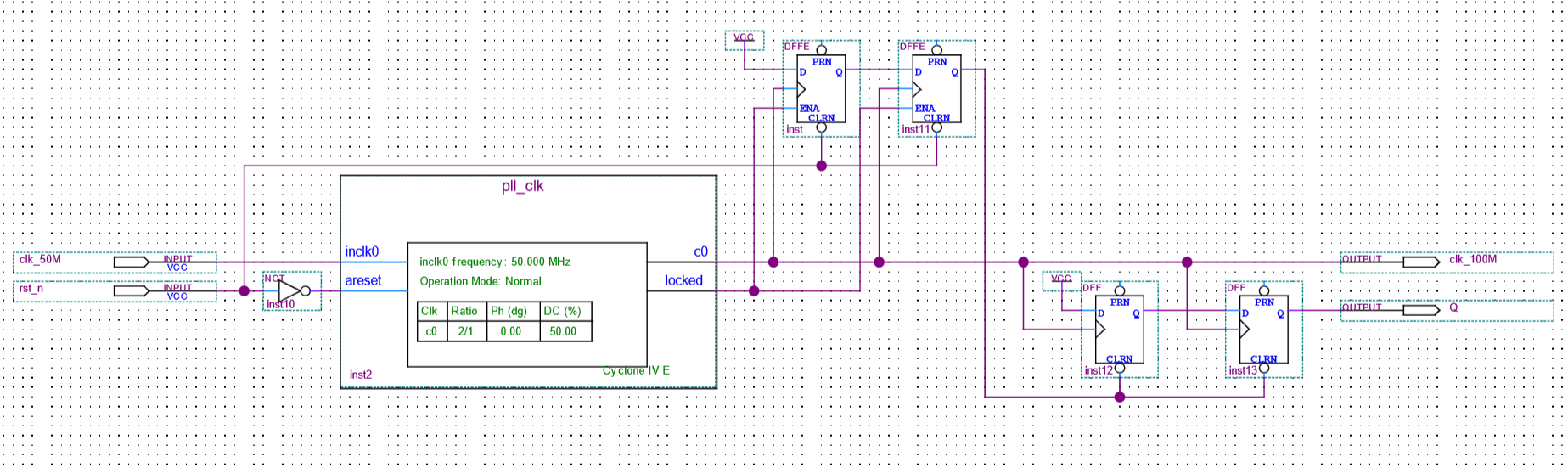

下面这种方式是为了使FPGA上电复位后达到更加稳定的状态,在第一个异步复位同步化的处理上加上了50ms的延迟,代码如下:(这里采用第一种方式进行编写)

1 module sys_ctrl( 2 input clk_50M, 3 input rst_n, 4 output clk_100M, 5 output reg syn_rst_n 6 ); 7 8 parameter RST_TIME = 24'd2_500_000; //50ms 9 10 reg rst_dly_1; 11 reg syn_rst_1; 12 reg com_rst_dly_1; 13 wire locked; 14 wire com_rst; 15 16 reg [23:0] cnt_rst; 17 18 always@(posedge clk_50M or negedge rst_n) 19 begin 20 if(rst_n == 1'b0) 21 cnt_rst <= 24'd0; 22 else 23 if(cnt_rst < RST_TIME) 24 cnt_rst <= cnt_rst +1'b1; 25 else 26 cnt_rst <= cnt_rst; 27 end 28 29 always@(posedge clk_50M or negedge rst_n) 30 begin 31 if(rst_n == 1'b0)begin 32 rst_dly_1 <= 1'b0; 33 syn_rst_1 <= 1'b0; 34 end 35 else begin 36 if(cnt_rst == RST_TIME)begin 37 rst_dly_1 <= 1'b1; 38 syn_rst_1 <= rst_dly_1; 39 end 40 else begin 41 rst_dly_1 <= 1'b0; 42 syn_rst_1 <= 1'b0; 43 end 44 end 45 end 46 47 assign com_rst = rst_n & locked; 48 49 50 always@(posedge clk_100M or negedge com_rst) 51 begin 52 if(com_rst == 1'b0)begin 53 com_rst_dly_1 <= 1'b0; 54 syn_rst_n <= 1'b0; 55 end 56 else begin 57 com_rst_dly_1 <= 1'b1; 58 syn_rst_n <= com_rst_dly_1; 59 end 60 end 61 62 63 pll_clk u_pll_clk( 64 .inclk0 (clk_50M), 65 .areset (!syn_rst_1), 66 .c0 (clk_100M), 67 .locked (locked) 68 ); 69 70 endmodule