- 前言

之前主要都在做FPGA算法层面的东西,最近觉得对于接口方面的知识比较欠缺,打算以PCI-E为例来系统的学习一下接口方面的知识。

- PCI-E全称PCI Express,是一种高速总线技术。各种PCI-E设备通过PCI-E协议互相连接,形成PCI-E系统,其拓扑结构如下所示:

其中,根联合体是连接CPU,主储存器到PCI-E总线结构的设备,相当于PCI系统中的北桥。FSB为Front Side Bus,是连接CPU与北桥的总线。可以根联合体上延伸出多个PCI-E接口。交换开关也可以引出多个PCI-E端口,从而连接更多的PCI-E端点设备。这里的端点设备也类似于显卡等PCI-E设备,可以是网卡,蓝牙设备,硬盘等。PCI-E-PCI桥保证了PCI设备也能接入PCI-E系统,增加了兼容性。

- 下面分析PCI-E的传输协议

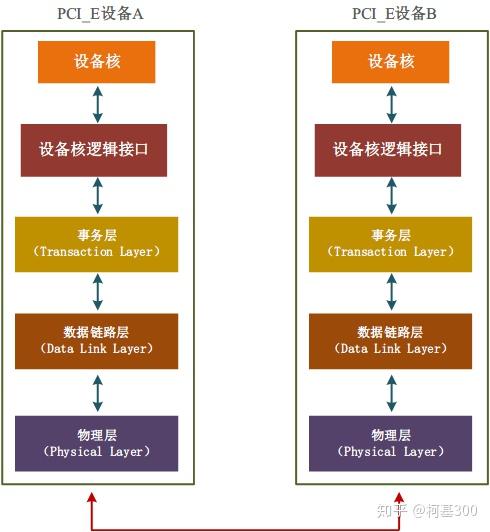

PCI-E协议规定采用三层分层协议来实现数据的传输,类似于网络通信中的TCP/IP通信协议,如下图所示:

上图展示了PCI-E设备A喝PCI-E设备B的通信协议,其中设备核和设备核接口可以简单的理解为应用层和应用层的接口,我们主要关心的是下面的三层,即事务层(TL层),数据链路层(DL层)和物理层(PL层)。

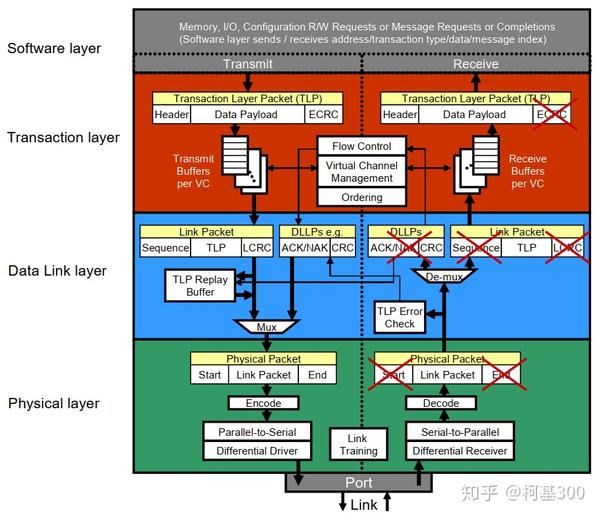

PCI_E设备之间通过数据包的形式进行传输,因此可以将三层的数据包分别表示为TLP(Transcation Layer package),DLLP和PLP。PCI-E设备发送端首先通过应用层和应用层接口传输TLP对应协议的数据格式给TL层,随后DL层对TLP进行二次打包形成DLLP在传输到PL层,PL层对数据DLLP进行编码后通过模拟信号来进行传输,接收端进行逆向操作得到最后的TLP,并最终解码成应用层需要的数据。

- TL层为数据添加包头(Header)和ECRC,这里的ECRC表示(End to end CRC),表示事务层的校验CRC编码。一个TLP如图所示:

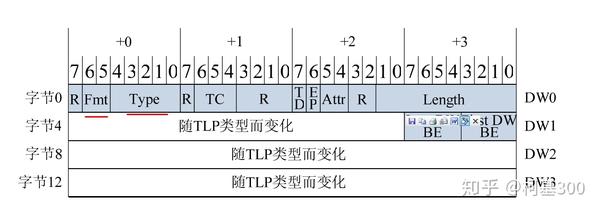

Header是TLP的核心部分,其大小主要在3DW或4DW(12字节或16字节,96bit or 128bit),以4DW(128bit为例),其DW0~DW3的结构如图所示:

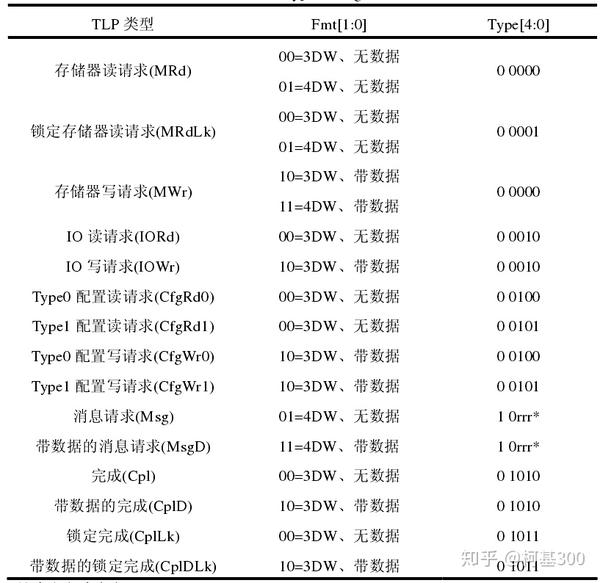

以DW0为例,DW0[9:0]表示数据长度(length),其最大值为1DW*2^10 = 4KB;DW0[13:12]表示数据包的属性,DW0[13] == 1表示使能PCI-X式的宽松排序,DW0[12] == 1表示不要求系统硬件去监控Cache;DW0[22:20]可以设置TC0~TC7四种不同的状态,默认TC0,用于流量控制;DW0[16] TD==1表示TLP包含ECRC;至于DW0[30:29]的Fmt和DW0[28:24]的Type,主要负责配置寄存器的一些读写请求和配置,如下表所示:

除此之外还有很多字段是根据不同的TLP类型而变化的,具体的可以配置TLP可以查询:PCI_Express_Specification这本PDF第二章。

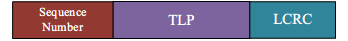

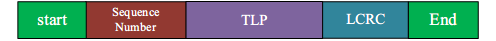

- DL层介于TL层和PL层,在发送端对TLP进行打包后发送到PL层,接收端则对PL层接包在传输到TL层,一个DL层传输的Package如下图所示:

DL层主要实现了三个功能:数据交换;错误检测/重试;初始化以及电源管理。

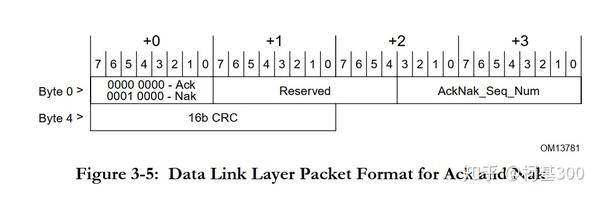

在错误检测/重试功能的实现中,DL层通过为TLP添加了Sequence Number和LCRC来实现。需要注意的是,PCI-E 设备B的DL层在接收到对应的Package时需要,返回一个应答包来确认或否定确认,即Ack/Nak DLLP,如下所示:

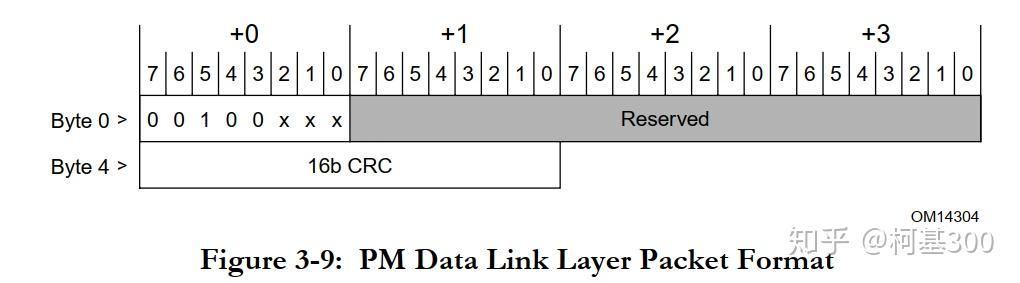

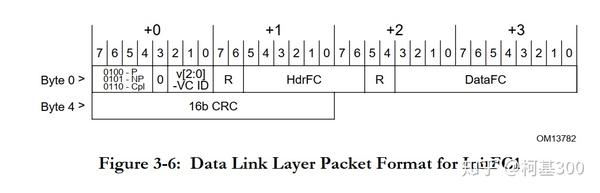

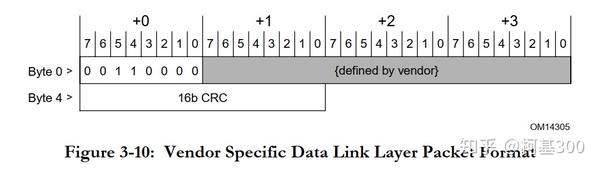

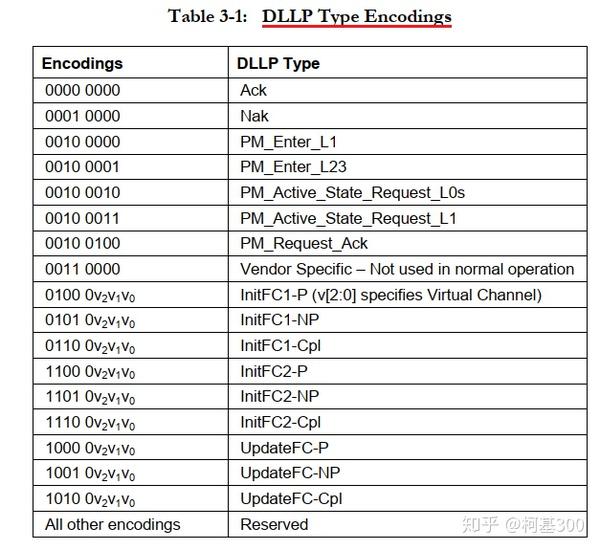

除此之外,根据不同的用途,DLLP可以分为很多种,大致可以分为四种常用类型,即对TLP的应答包—Ack/Nak DLLP,电源管理DLLP,流控制DLLP以及厂商自定义DLLP,分别如下所示:

其中,Ack/Nak DLLP中的Ack和Nak分别表示确认Sequcence Number——成功收到一定数量的TLP和否定确认Sequcence Number——来启动重试功能;fig3-6中的FC1表示流控制(Flow Control);fig 3-9中的PM表示Power Management。关于Byte 0[31:24]表示DLLP Type字段,其各个字段的编码以及对应功能如下标所示:

除了上述功能,DL层还提供了数据完整性检查和CRC校验等功能,具体可以参考 PCI_Express_Specification第三章。

- 发送端PL层将DL层过来的package进行编码并发送,其中涉及逻辑子模块和电气子模块。逻辑子模块将上层的数据处理后送入电气层,在逻辑层对上层传输过来的Package进行的操作主要是添加一个帧头和帧尾:

一个完成的PCI-E发送-接收模型如下图所示:

PCI_E协议的总体介绍到这里就告一段落了,如果以上协议的逻辑部分通过FPGA去纯撸代码实现感觉还是比较困难的,后面有空再去研究一下xilinx 的IP实现。