ARM架构支持跨大范围性能点的实现。ARM处理器的架构简单性导致了非常小的实现,而小的实现意味着设备可以具有非常低的功耗。实现大小、性能和非常低的功耗是ARM体系结构的关键属性。

ARM架构是一个精简指令集计算机(RISC)架构,因为它包含了这些RISC架构特性:

- 一个大的统一寄存器文件

- 一种加载/存储体系结构,其中数据处理操作只对寄存器内容进行操作,而不是直接对内存内容进行操作。

- 简单的寻址模式,所有加载/存储地址仅由寄存器内容和指令字段决定

此外,ARM架构还提供:

- 将移位与算术或逻辑运算相结合的指令。

- 自动递增和自动递减寻址模式,以优化程序循环。

- 加载和存储多个指令,

- 以最大限度地提高数据吞吐量。

- 许多指令的条件执行,以最大化执行吞吐量。

这些对基本RISC体系结构的增强意味着ARM处理器实现了高性能、小程序大小、低功耗和小硅区之间的良好平衡。

本体系结构参考手册定义了一组实现必须遵循的行为,以及一组软件使用实现的规则。它没有描述如何构建实现。

除非体系结构指定不同,否则实现的程序员可见行为必须与程序的简单顺序执行相同。这种程序员可见的行为不包括程序的执行时间。

指令集:

ARM指令集是一组32位指令,提供全面的数据处理和控制功能。

Thumb 指令集是作为一个16位指令集开发的,带有ARM指令集功能的子集。它提供了显著提高的代码密度,但性能有所降低。执行拇指指令的处理器可以更改为执行ARM指令来处理性能关键段,特别是处理中断。

ARMv6T2引入了Thumb-2技术。该技术使用许多32位指令扩展了原始Thumb指令集。ARMv6T2中包含的32位Thumb指令的范围允许拇指代码实现与ARM代码类似的性能,代码密度比早期的Thumb代码更好。

在ARMv6T2中,ARM和Thumb指令集提供了几乎相同的功能。

体系结构版本、概要文件和变体:

自引入以来,ARM体系结构已经发生了显著的变化,并且ARM还在继续开发它。到目前为止,已经定义了该体系结构的7个主要版本,用版本号I到7表示。其中,前三个版本现在已经过时了。

ARMv7提供了三个概要文件:

ARMv7-A :

- 实现具有多种模式的传统ARM体系结构。

- 支持基于内存管理单元(MMU)的虚拟内存系统体系结构(VMSA)。

- ARMv7-A实现可以称为VMSAv7实现。支持ARM和Thumb指令集。

ARMv7-R :实时配置文件

- 实现具有多种模式的传统ARM体系结构。

- 支持基于内存保护单元(MPU)的受保护内存系统体系结构(PMSA)。

- ARMv7-R实现可以称为PMSAv7实现。支持ARM和Thumb指令集。

ARMv7-M :在ARMv7-M体系结构参考手册中描述的 微控制器配置文件:

- 实现一个为低延迟中断处理设计的程序员模型,使用寄存器的硬件堆栈和对用高级语言编写中断处理程序的支持。

- 实现ARMv7 PMSA的变体。

- 支持ARM和Thumb指令集。

A1.5 The ARM memory model

ARM指令将地址设置为232个8位字节的单向地址空间。这个地址空间也被认为是230个32位 字 或231个16位 半字 。

该架构提供以下设施:

- 在未对齐的内存访问上生成异常。

- 限制应用程序对指定内存区域的访问。

- 将执行指令提供的虚拟地址转换为物理地址。

- 在大词尾和小词尾之间改变对单词和半单词数据的解释

- 控制对内存的访问顺序

- 控制缓存。

- 同步多个处理器对共享内存的访问

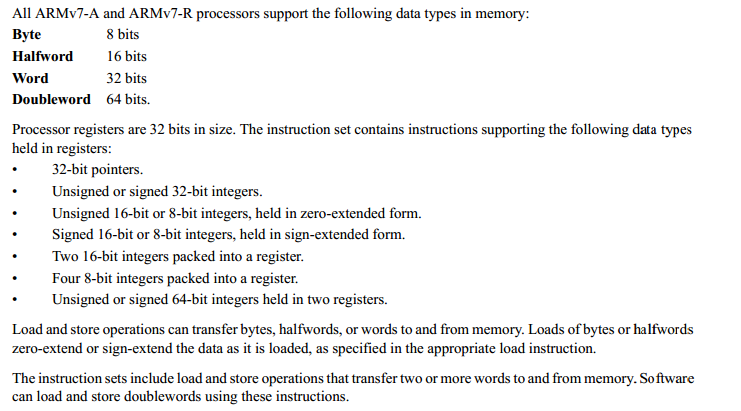

A2.2 ARM core data types and arithmetic

加载和存储操作可以向内存传输字节、半字或字。加载字节或半字零扩展或符号扩展数据,如在适当的加载指令中指定的那样。

指令集包括加载和存储操作,这些操作将两个或多个单词从内存中传输到内存。软件可以使用这些指令加载和存储双单词。

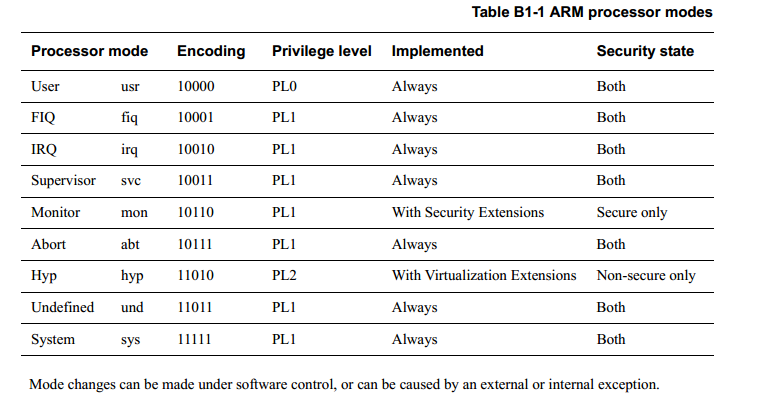

B1.3.1 ARM processor modes

模式更改可以在软件控制下进行,也可以由外部或内部异常引起。

Notes on the ARM processor modes

User mode

操作系统以用户模式运行应用程序,以限制系统资源的使用。以用户模式执行的软件在PLO上执行。用户模式下的执行有时被描述为无特权执行。应用程序通常在用户模式下执行,任何程序在用户模式下执行:

- 只对系统资源进行无特权访问,这意味着它不能访问受保护的资源。

- 系统资源。只对内存进行无特权访问。

- 除非引发异常,否则无法更改模式,请参阅B1-1164页的异常处理。

System mode

以系统模式执行的软件在PLI上执行。系统模式具有与用户模式相同的可用寄存器,并且不会由任何异常输入。

Supervisor mode

管理器模式是执行SVC(管理器调用)指令生成一个管理器调用异常的默认模式,该异常被带到管理器模式。

处理器在重置时进入管理模式。

Abort mode

中止模式是执行数据中止异常或预取中止异常的默认模式。

Undefined mode

未定义模式是执行与指令相关的异常(包括任何执行未定义指令的尝试)的默认模式。

FIQ mode

FIO模式是执行FIO中断的默认模式。

IRQ mode

IRQ模式是IRQ中断的默认模式。

Hyp mode

Hyp模式是非安全的PL2模式,作为虚拟化扩展的一部分实现。

Hypervisor调用异常和Hyp Trap异常是作为虚拟化扩展的一部分实现的异常,它们总是在Hyp模式下执行。

Monitor mode

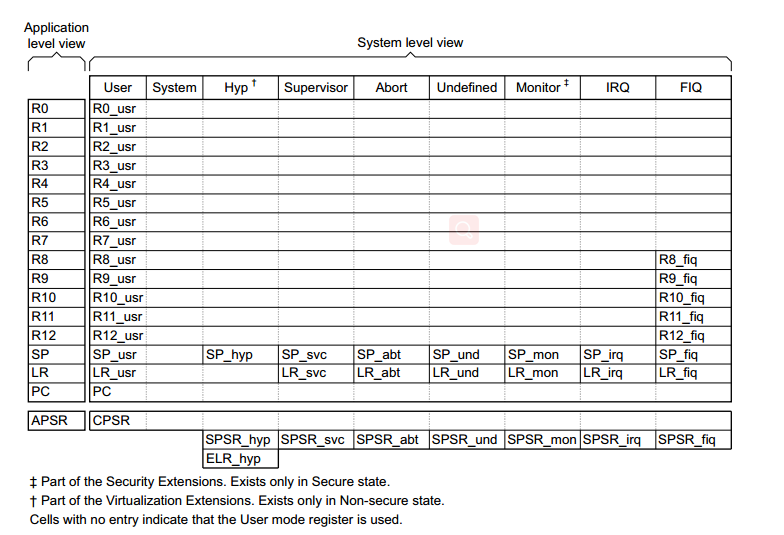

B1.3.2 ARM core registers

SP, the stack pointer

处理器使用SP作为指向活动堆栈的指针。在拇指指令集中,大多数指令不能访问SP。

唯一能够访问SP的指令是那些设计成使用SP作为堆栈指针的指令。

ARM指令集提供了对SP更通用的访问,并且它可以用作通用寄存器。然而。ARM不赞成将SP用于除堆栈指针之外的任何用途。

LR, the link register

链接寄存器是一种特殊的寄存器,它可以保存返回的链接信息。本手册中描述的一些情况要求使用LR。当软件不需要LR进行链接时,它可以将LR用于其他目的。它可以将LR称为R14。

PC, the program counter

执行ARM指令时,PC读取当前指令加8的地址

执行Thumb指令时,PC读取当前指令加4的地址

向PC写入一个地址会导致该地址的分支。

大多数Thumb指令无法访问PC。

B1.3.3 Program Status Registers (PSRs)

开始学习汇编指令: A8 Instruction Descriptions

以 mov指令为例:

32位数据为编译后的机器码。

1 #include <stdio.h> 2 3 int main() 4 { 5 __asm__ __volatile__( 6 "nop " 7 "mov r0,#98 " 8 "mov r0,#0xff0000 " 9 "mov r0,#0xf000000f " 10 "nop " 11 12 13 ); 14 15 return 0; 16 }

反汇编后:

1 e320f000 nop {0} 2 e3a00062 mov r0, #98 ; 0x62 3 e3a008ff mov r0, #16711680 ; 0xff0000 4 e3a002ff mov r0, #-268435441 ; 0xf000000f 5 e320f000 nop {0}

分析:

1110 0011 1010 0000 0000 0000 0110 0010 //e3a00062

1110 0011 1010 0000 0000 1000 1111 1111 //e3a008ff 0xff0000 循环左移16位才能得到小于256 再除以2 放在16位开始的位置

1110 0011 1010 0000 0000 0010 1111 1111 //e3a002ff 0xf000000f 循环左移4位,除以2 放在16位开始的位置

没有条件:1110 None (AL) d

add、adc、sub、sbc、and、

mrs、msr

ldr、ldrh、ldrb

str、strh、strb