欢迎关注个人公众号摸鱼范式

网络课程《数字集成电路静态时序分析基础》的笔记

鲁棒性检查

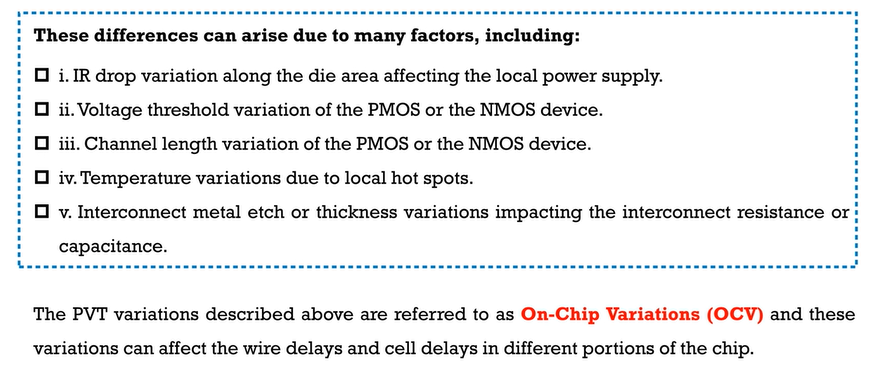

工艺制成和环境因素会导致die上的延迟不均匀,影响因素包括:

这些偏差被称为OCV,在做STA时也需要考虑到OCV

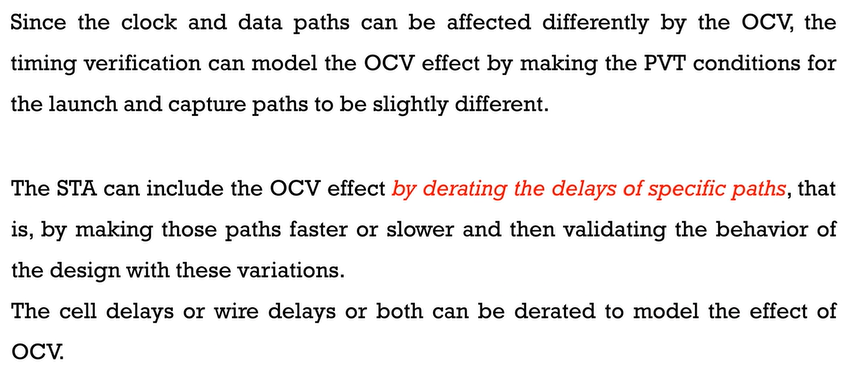

通过derating把延迟加到特定的路径上,模拟OCV的影响

建立时间检查

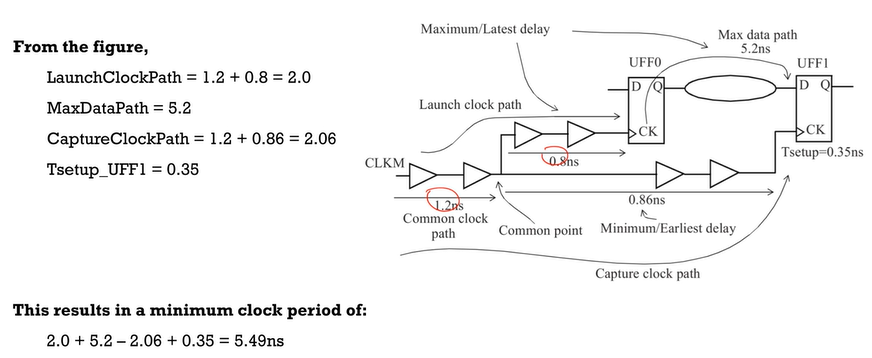

下面考虑测建立时间的OCV影响

最坏的情况就是发射路径变大,而捕获路径减小。

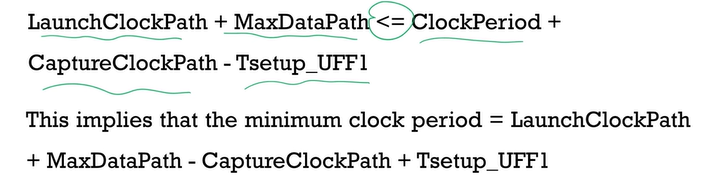

建立时间的关系为:

那么就有

最小的时钟周期为5.49ns,如果考虑OCV,可以添加derate参数,放大发射路径,缩小捕获路径,让检查更加严格

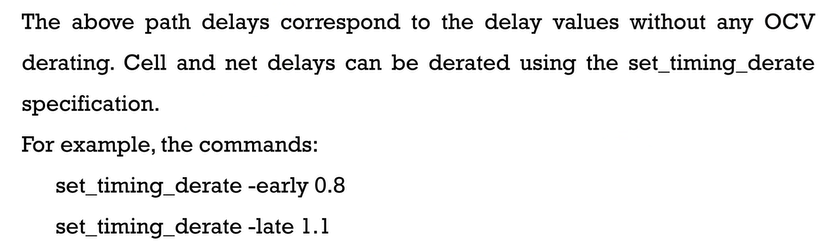

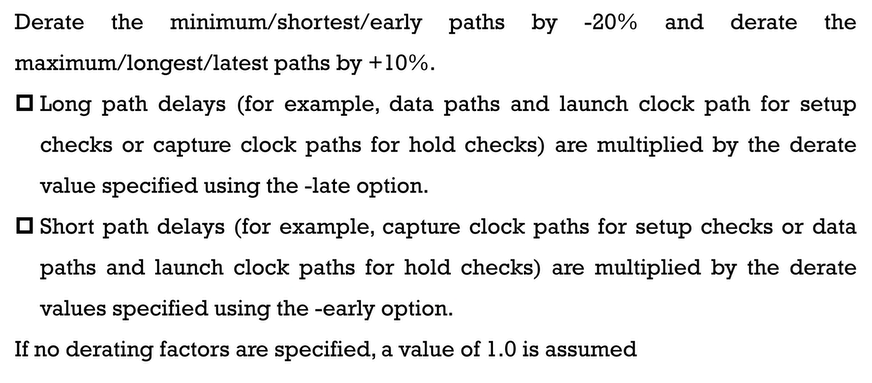

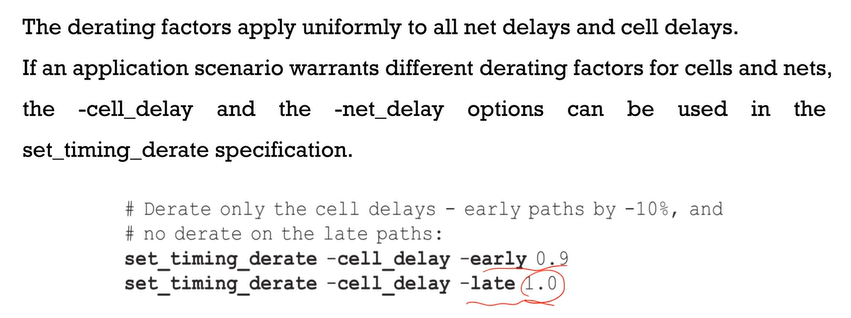

总而言之通过derate让约束变紧,下面是一个例子,cell和net延迟都可以用derate进行索方

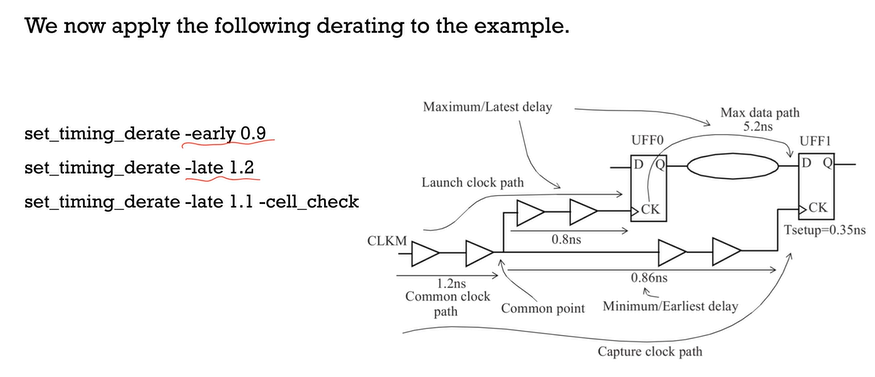

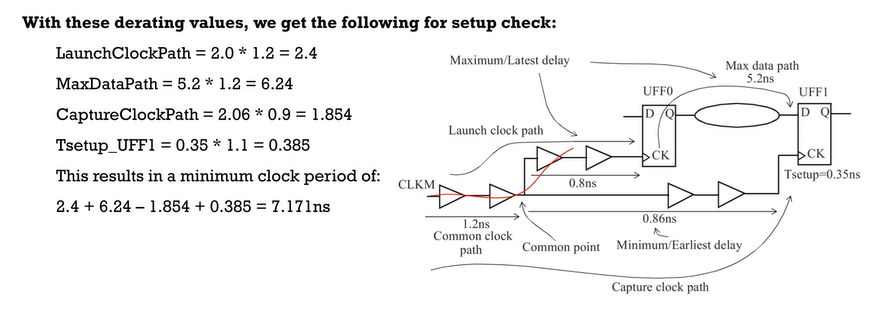

对于刚刚的例子,如果施加下面的derate

那么计算参数的变化如下

时序变紧,最大时钟周期为7.171ns。对于建立时间,early会施加在捕获路径上,late会施加在发射路径上,cell会施加在cell的建立时间上。

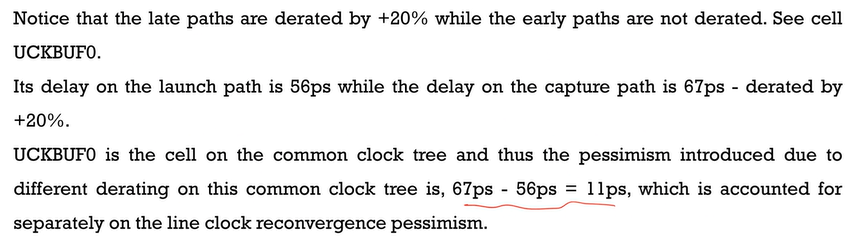

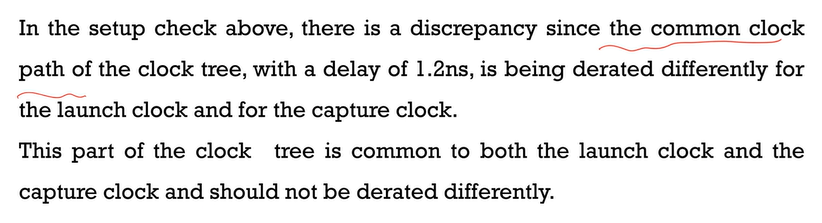

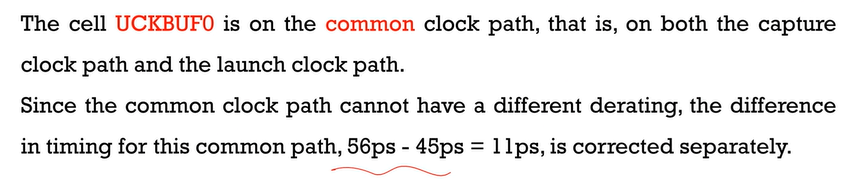

值得注意的是,在公用的路径中,在发射路径和捕获路径中,一个放大,一个缩小,实际上不应该这样计算。

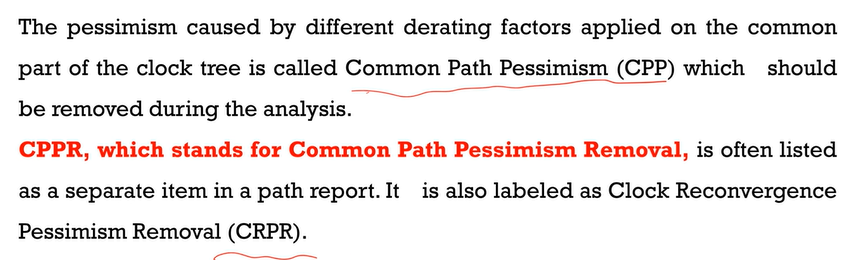

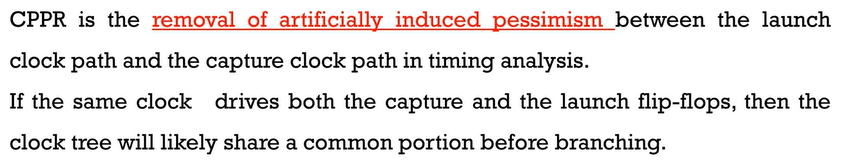

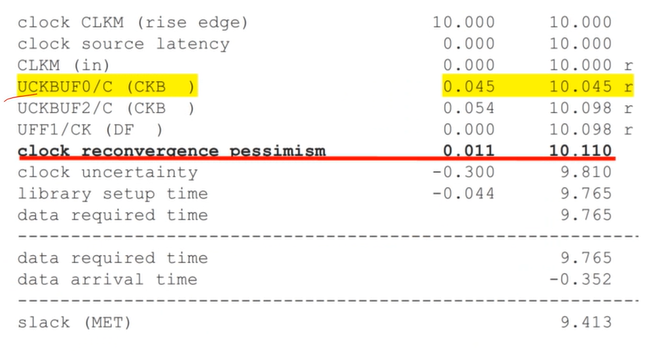

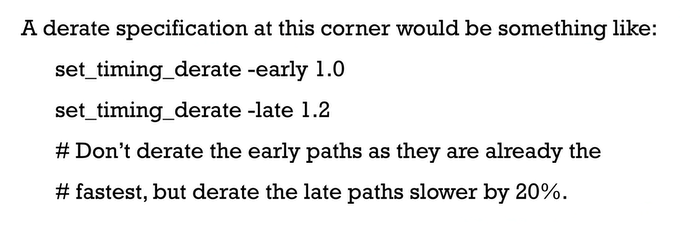

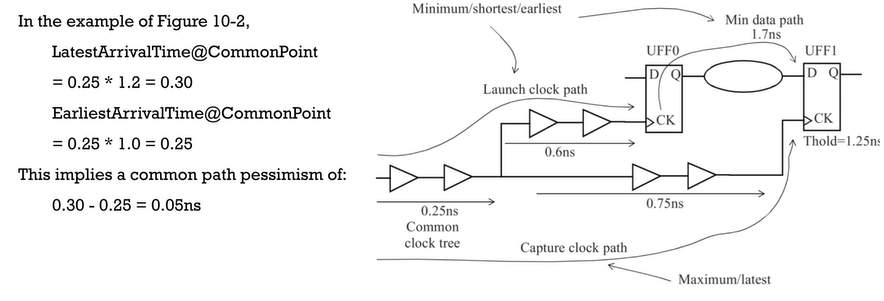

共用路径计算不一致会导致STA结果过于悲观,被称作CPP,而移除的方法被称为CPPR

CPP的计算是通过公用路径的终点计算的,计算差值然后再进行补偿。

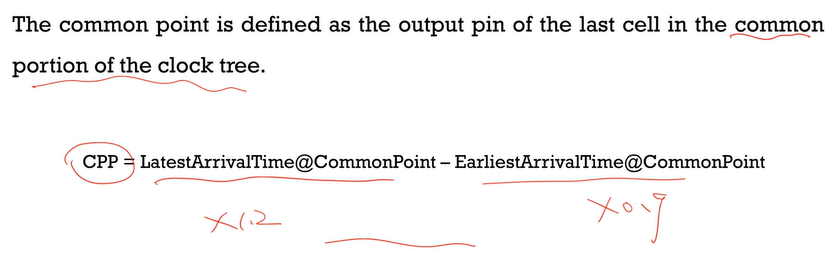

那么在刚刚的例子中,CPP的值为0.36,补偿以后时钟周期从7.171减小到6.811

总的来说,引入OCV然后再移除CPPR,时钟周期从5.49增加到6.81

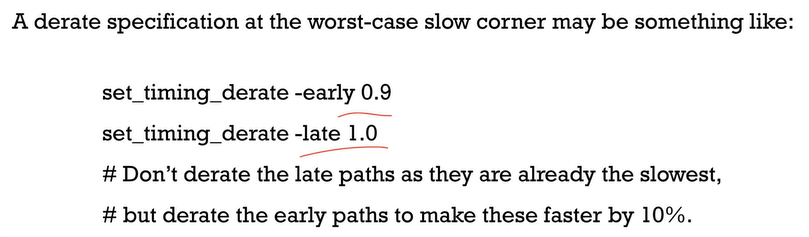

如果建立时间检查的时候已经在最差的PVT中,那么发射路径已经很慢了,不需要derate再去悲观考虑,只考虑将捕获路径缩小

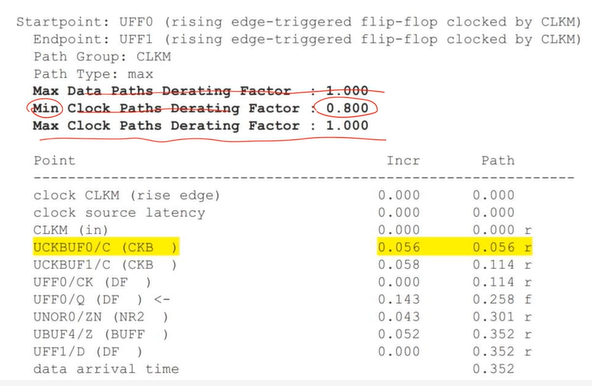

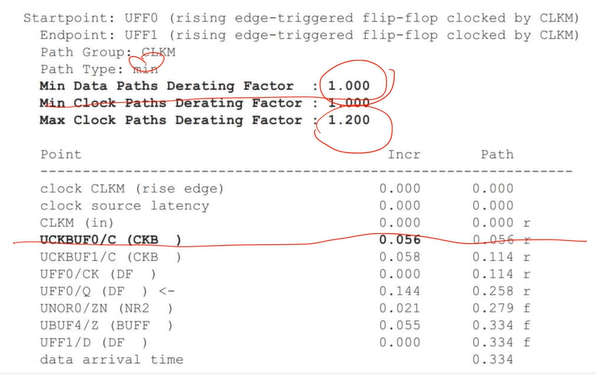

引入OCV以后的时序报告,发射路径

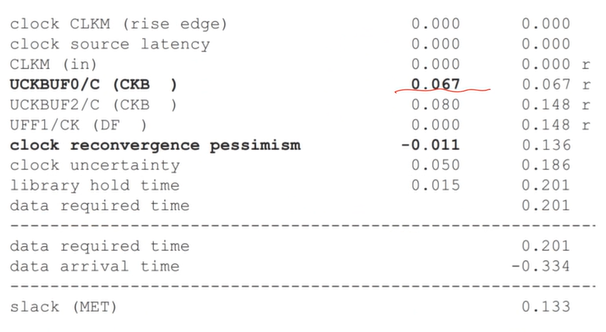

看到高亮处,在发射路径和捕获路径不一样,这是由于derate参数设置的问题,而红线标识的CPP就是在补偿。

保持时间检查

收紧保持时间检查就需要在OCR条件里,缩短发射时间,延长捕获路径。保持时间检查公式为:

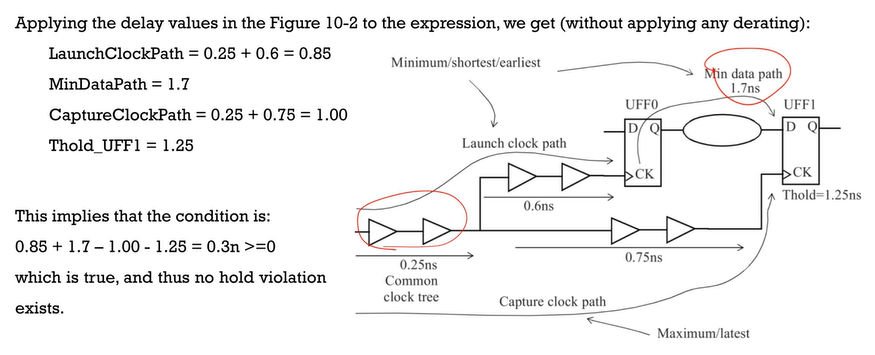

下面举例

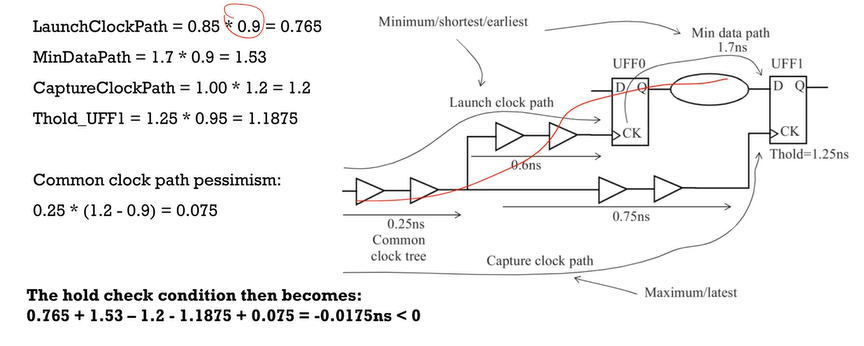

考虑OCV,施加约束

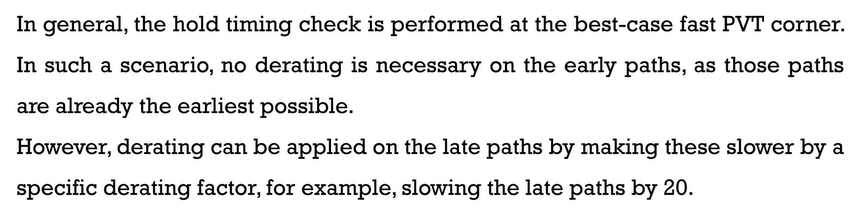

考虑OCV以后,保持时间不满足。保持时间检查时,PVT条件是最快的,那么只让捕获路径变慢就好了,发射路径已经不能再快了

和建立时间中的也是一样的,共用路径的CPP也要考虑

那么时序报告如下

CPP也被去掉了