欢迎关注个人公众号摸鱼范式

网络课程《数字集成电路静态时序分析基础》的笔记

建立时间和保持时间检查

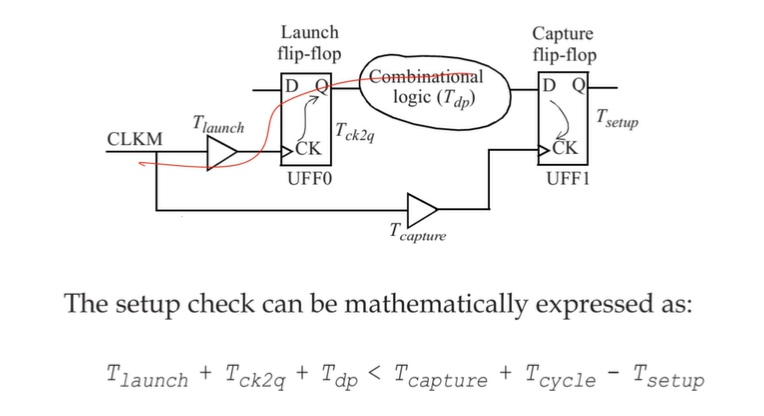

建立时间检查

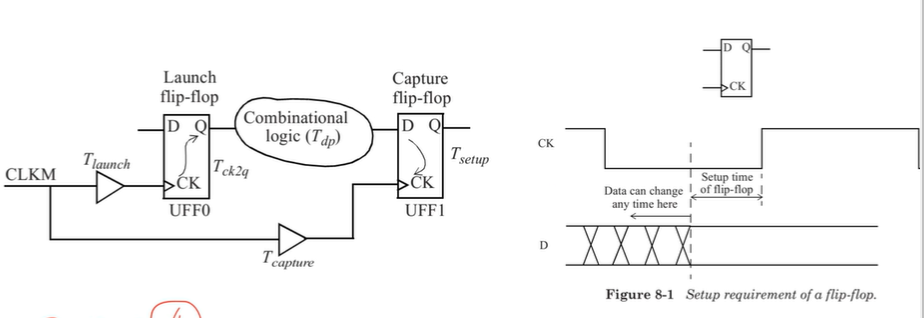

最常见的路径:CK-D。

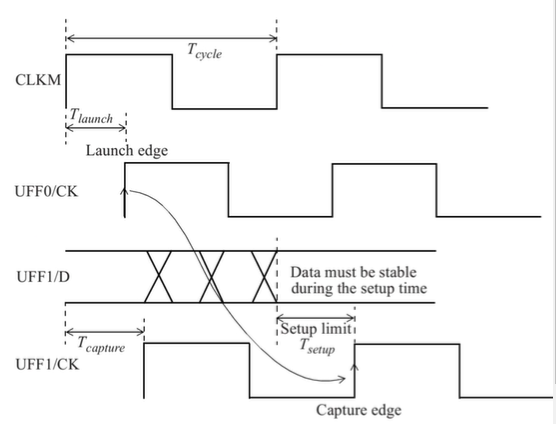

区分launch clk和capture clk

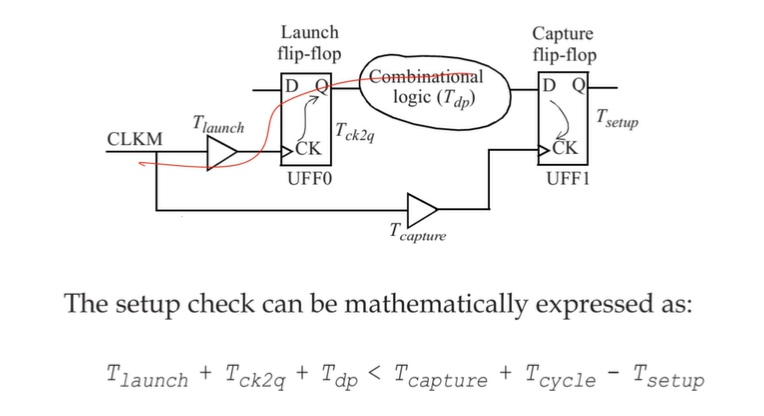

建立时间检查表达式:

ck to d

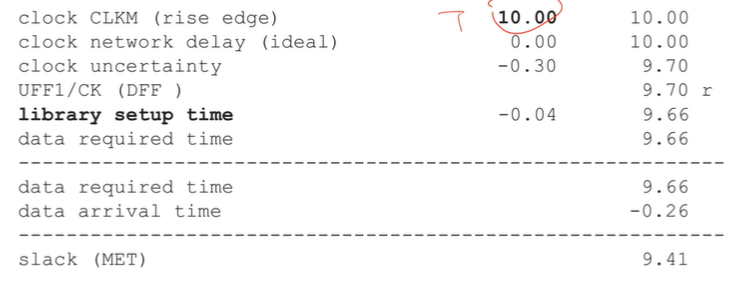

下面是一个timing report,起点是UFF0,终点是UFF1,path group是按照终点时钟分类的,所以是CLKM。path type max代表检查最大的路径延迟,point表示途径点,incr代表经过这个点的增量,path代表累计延迟。r和f代表rise和fall。

data arrival time代表总延迟,这是一个launch path的报告。

下面的是一个capture path的报告,首先经过时钟周期,时钟网络理想,建立时间0.04,时钟误差0.3,uncertainty为了让建立时间检查更加严苛。最终得到一个data required time,数据要求到达时间,必须要此之前,要求slack>=0,才算是时序满足要求。

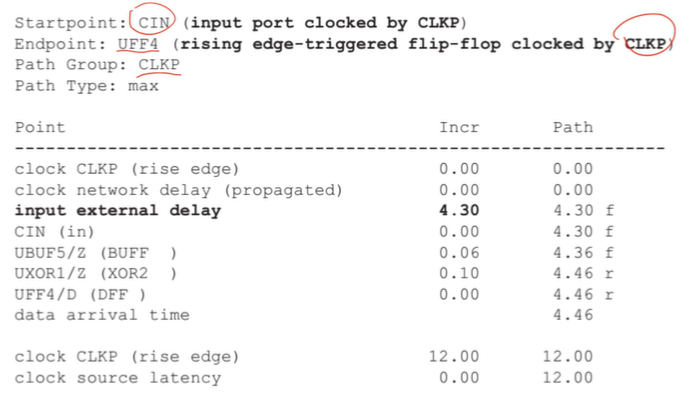

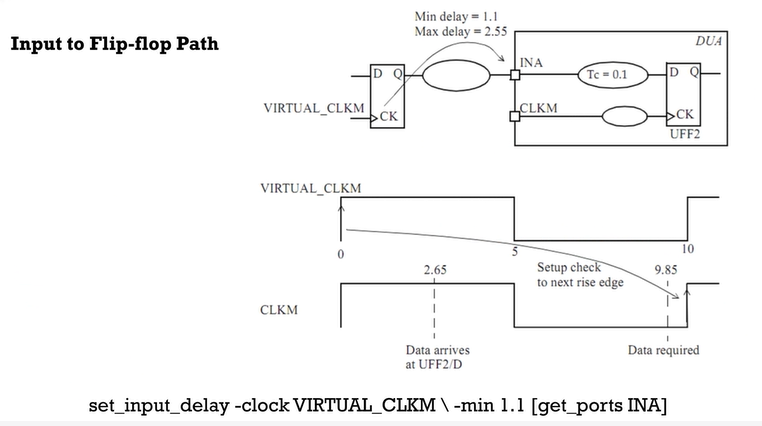

input port to flip-flop

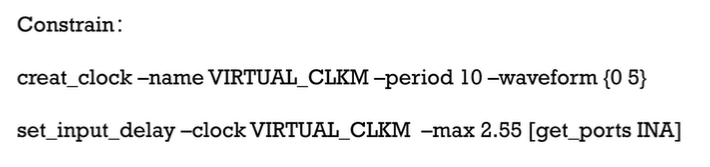

时序检查之前,由于外部没有时钟设定,要先设定虚拟时钟

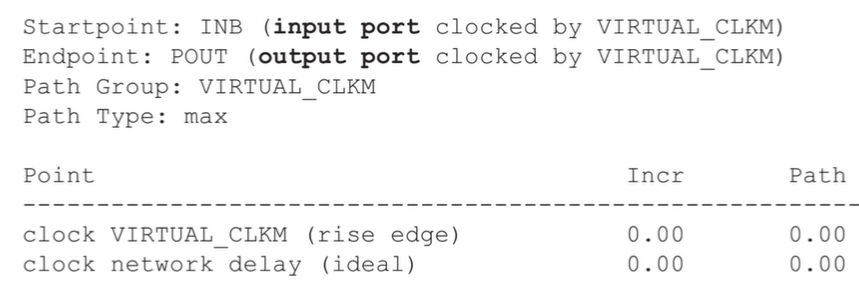

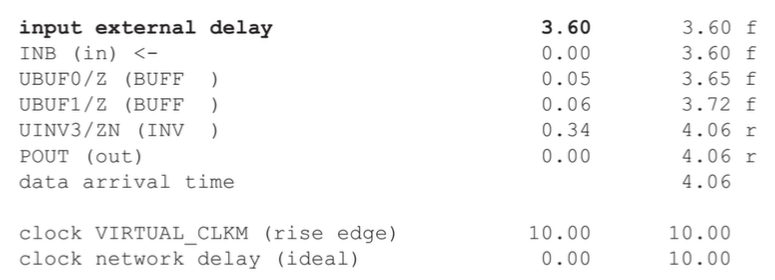

时序报告如下

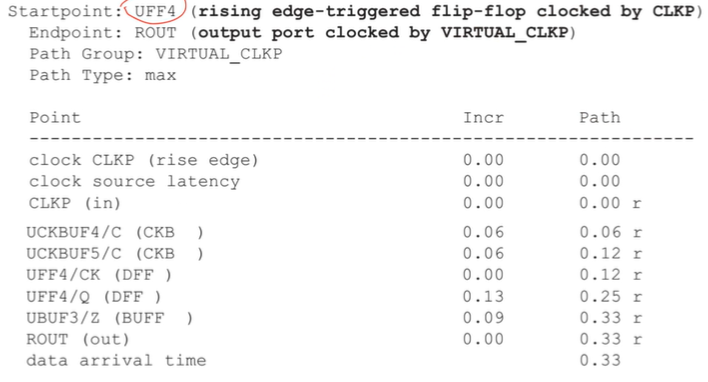

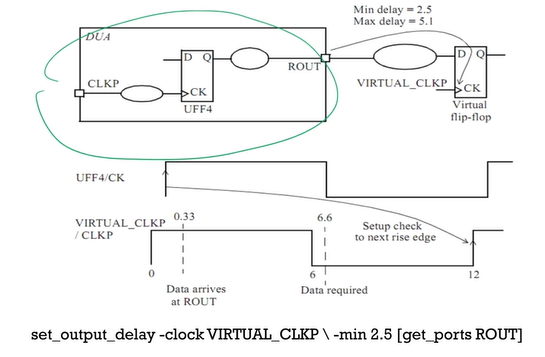

flipflop to output

要额外设定load约束

同样设定了虚拟时钟

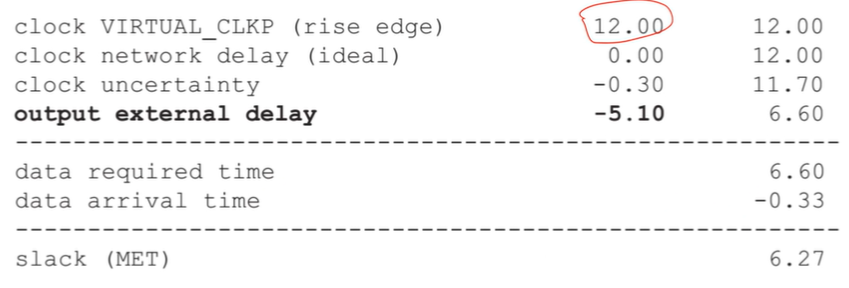

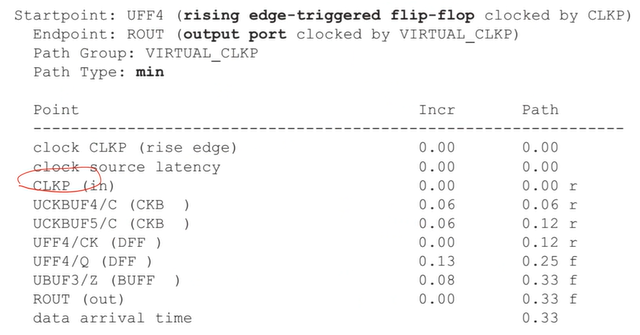

时序报告,注意path group是虚拟时钟,按照终点时钟分类。

launch path,output delay不在这里

captured path,output delay在这里,这里的5.1包含了setup time,所以要放在captured path这里。

input to output

时序报告:

这样时序不满足,需要修改

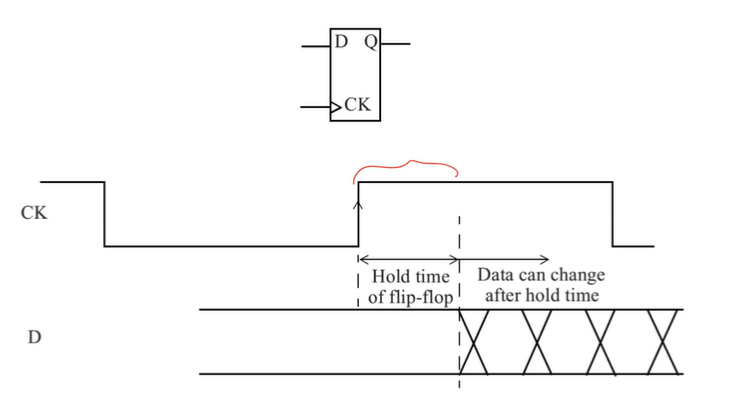

保持时间检查

与建立时间一致,通过launch path和captured path进行检查

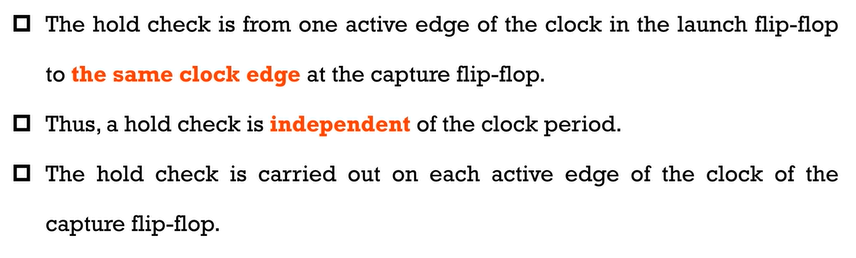

但是存在一些区别,保持时间是在launch flip-flop和captured flip-flop的同一个时钟边沿进行检查,因此保持时间检查与时钟周期无关。

路径分析

保持时间检查

reg to reg

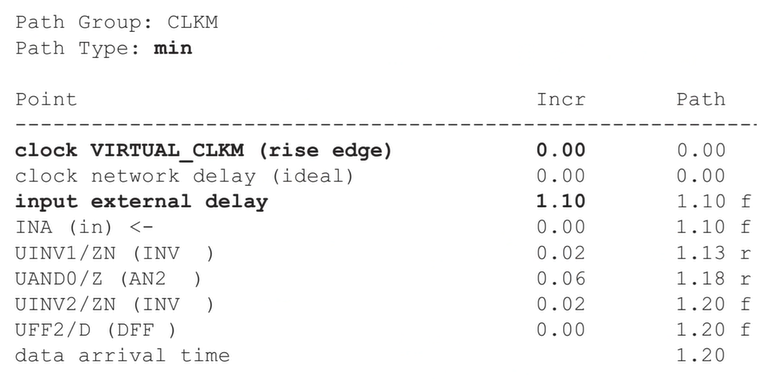

保持时间检查要使用min delay进行检查

一个保持时间检查报告,launch path

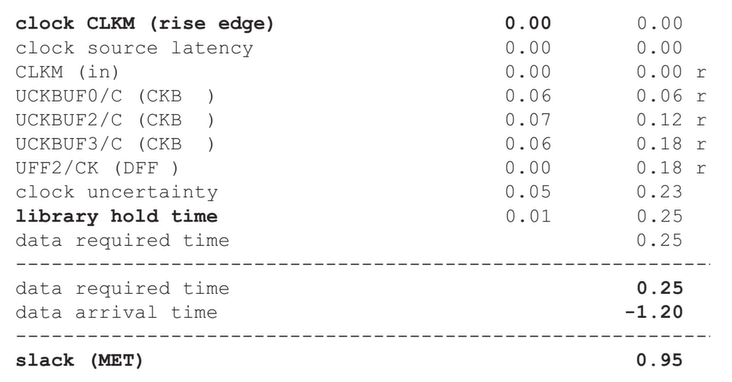

capture path

要求required time<arrival time

与setup time的区别

input to reg

时序报告

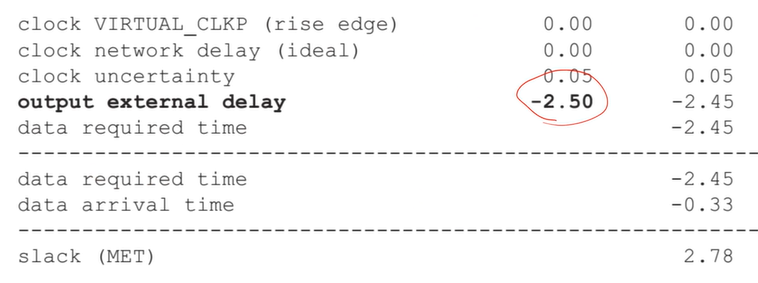

reg to output

时序报告

依然没有hold time,全部算在output delay里

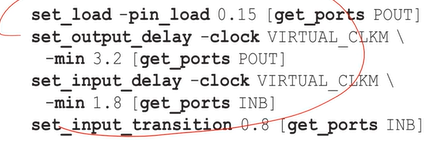

input to output

外加约束

时序报告

总结

建立时间检查

保持时间检查