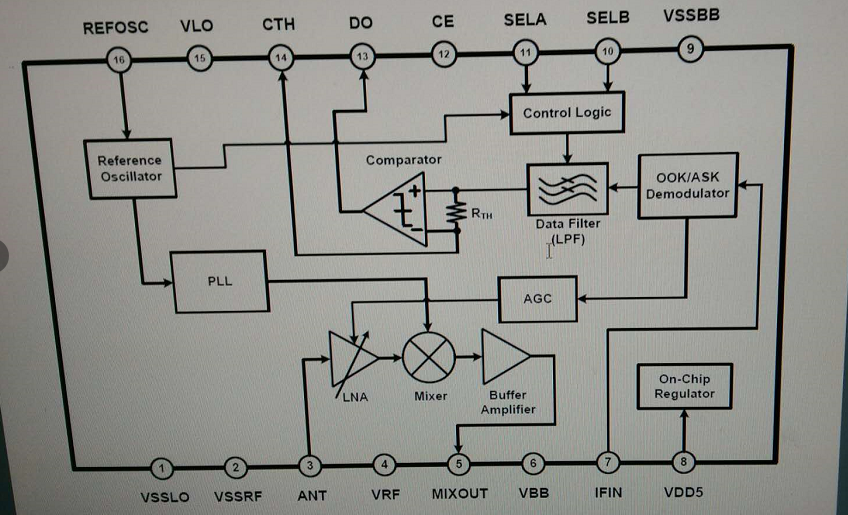

1. IC内部组成:

Reference Oscillator:基准参考晶振-后续会放大32 倍

Comparator:比较器,输出RF信号

control logic:控制晶振倍频,控制LF,power模块。

data Filter:(loop filter) 环路滤波器,属于encode的一个模块,用来滤除不想要的谐波和波段。

Demodulator:ASK解调

low-noise amplifier (LNA):低噪声放大器,其中AGS会给一个负反馈、阻值其放大失真。

down-conversion mixer:下变混频器(频率的混合是加减的计算规则)-将基波和载波混合。

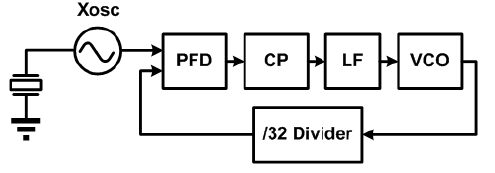

phase-locked loop (PLL):锁相环,用来统一整合时脉讯号,使高频器件正常工作,当data发出时,需要开启PLL,锁住内部晶振。

Buffer Amplifier:信号放大器

AGC:auto gen-control 自动增益控制,是一个负反馈控制电路.

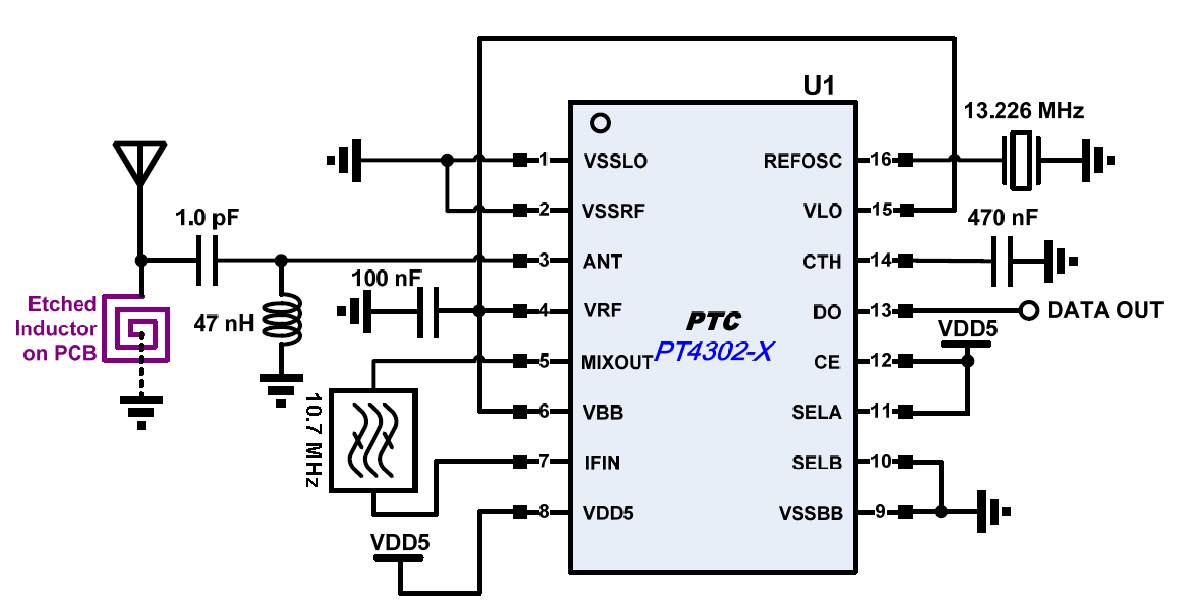

2应用电路分析

1外围元器件参数选择:

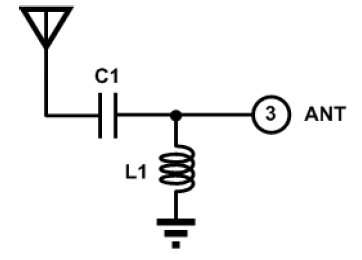

L1: 47 n H Antenna input matching, coil inductor

L2 :27 n H Antenna ESD protection, coil inductor

C1: 1.0 p F Antenna input matching

C2, C3, C4: 100 n F Power supply de-coupling capacitor

C5: 470 n F CTH (affects coding type and start-up time)

C6 :220 p F Depends on crystal oscillator vendor, for frequency fine tuning

R1 :10 Ω Power supply de-coupling resistor (optional)

R2, R3, R4, R5 : 10 K Ω MCU interface resistor (optional)

R6 :8.2 M Ω For reducing data output noise (optional)

F1 : 10.7 MHz Band-pass filter

X1 :13.226 MHz Reference crystal oscillator (关键器件) 要做可靠性测试

3性能参数测试

a 灵敏度 -111dB ,工程应用中应该达到-108dB的直连灵敏度

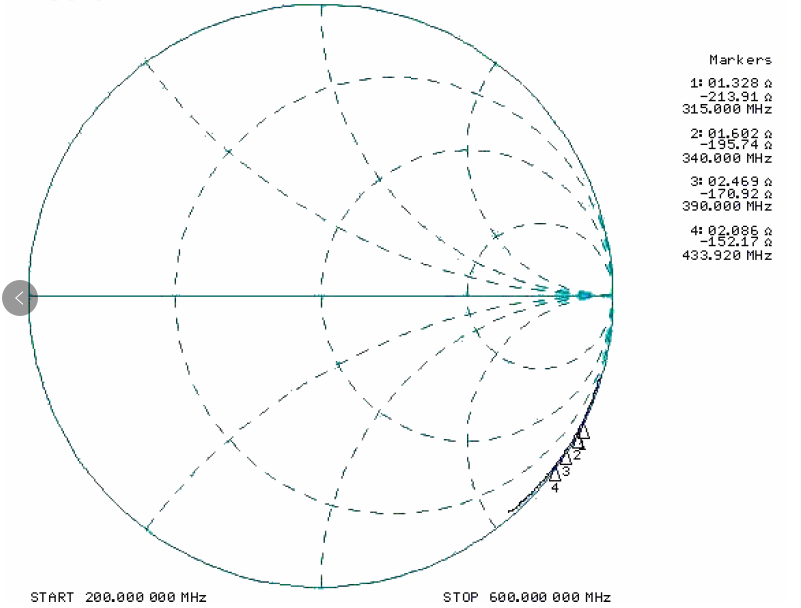

b 天线匹配:标准的50 Ω L-type (整改看前一篇内容)

c 阻抗匹配分析: 2.086 - j152.17

d 晶振选型: f = fLO / 32 = (f TX - 10.7) / 32.

计算得参考晶振为13.226 Mhz (+-75KhZ)

晶振可靠性测试:取20pcs样品在线测量,中心频率和参考dB值,一致性要控制在5%以内。

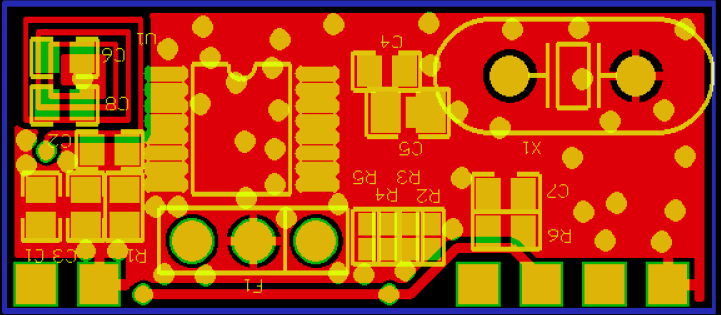

4 RF- layout

根据参考的Layout,我们取消天线旁边的GND 和VCC

5 RF 认证

已通过