为什么计算setup time的slack时需要考虑加周期,hold time时不需要?

总结一:

因为计算setup time时,由于存在数据传输data delay,Launch edge与Capture edge并不对应时钟信号source clock的同一个时钟沿,因此需要考虑加周期。单时钟周期检查的时候工具默认capture edge-launch edge=1个周期。

Hold time时由于二者对应的是同一个时钟沿,所以不考虑周期。

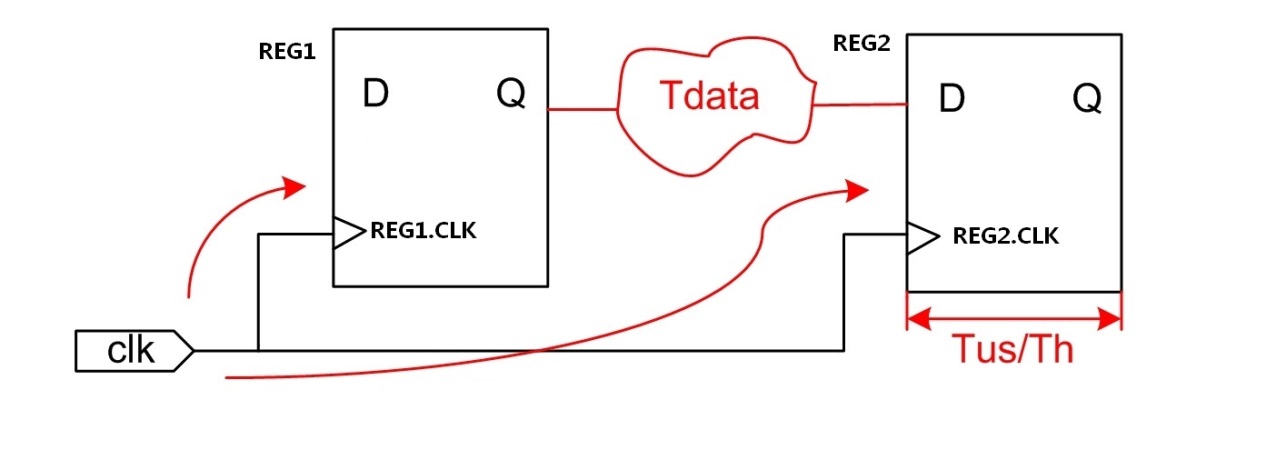

如图所示:REG1.CLK的第一个时钟上升沿对应launch edge,REG2.CLK的第二个时钟上升沿对应capture edge。二者分别对应时钟源source clock CLK的第一个上升沿和第二个上升沿。

总结二:

时钟源CLK经过network latency后,第一个上升沿到达REG1.CLK端,并触发REG.1数据输入端REG.1.D数据输入。此时CLK第一个上升沿同时发送往REG2.CLK,它所需要的时间相比data latency非常之短,因而此时检查setup time对此次数据传输没有意义,增加周期后,才有意义。

Hold time时,第一波数据稳定输入REG2.D与第二波数据传输至REG2.D对应REG2.CLK同一个时钟信号,因而不用加周期计算。

对于多周期:

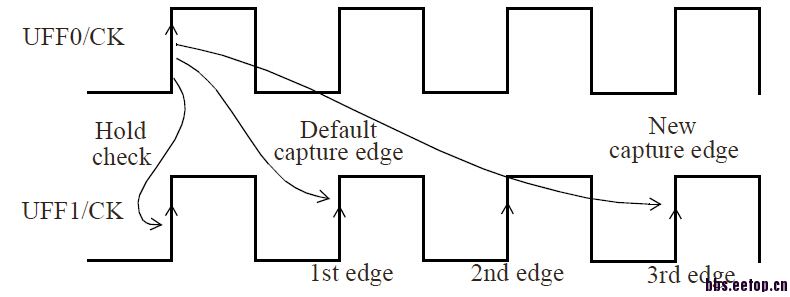

多时钟周期或者多周期路径检查的时候,如果setup设置成N,那么hold需要设置成N-1;即是说

Thus, in most designs, a multicycle setup specified as N (cycles) should be accompanied by a multicycle hold constraint specified as N-1 (cycles).

解释有两种,本质都是一样的

说法一: hold的capature edge is prior to setup capature edge,This imposes a restriction that data can only change in the one cycle before the setup capture edge as the figure shows. Thus the data path must have a min delay of at least two clock cycles tomeet this requirement. Here is such a path report.

说法二:hold 是对前后两个flip flop在相同时钟沿的检查.设了n-1就是返回n-1个周期做hold的检查,满足了两个flip flop在同一个时钟沿。如果没有-hold默认是检查n前一个有效时钟沿,如果n>=2,hold的检查就不是在同一个时钟效沿,对hold的要求就要多n-1个周期,那样太苛刻了,一般时序无法收敛。

Skew的大小对setup和hold的影响是什么?

根据原理可以修改下slack的计算方式得:

Setup: slack=(period+clock skew-setup time)-(REG1 cell delay+combinatinal logic delay)

Hold:slack=(REG1 cell delay+combinatinal logic delay)-(clock skew+hold time)

其中clock skew=Tclk2-Tclk1

因此无论对于setup还是hold时计算slack,clock skew都是越趋于0越悲观。如果clock skew可为负值,则对setup time越小越悲观,对hold time越大越悲观。

【我的理解】

有关setup和hold相关的计算与概念时,最大的难点在于,对于不同的模型和分析角度,它们对应的计算方式和概念理解算法和说法都不一样,大家在讨论的时候,因为角度不同,很容易造成理解偏差。其实根本概念都只是针对时钟信号和数据信号两部分来看,本质互通,并没有涉及到特别难的原理或公式。

转至: https://www.cnblogs.com/kylechiang/p/4773196.html