Lab07--数码管电路驱动

本实验的目的是实现常用的7段码数码管电路的驱动,用动态扫描的方式实现,而且是同步动态扫描,因为DE2的数码管是直接驱动的,不能列扫描,所以本实验不适合DE2,但同样很经典。

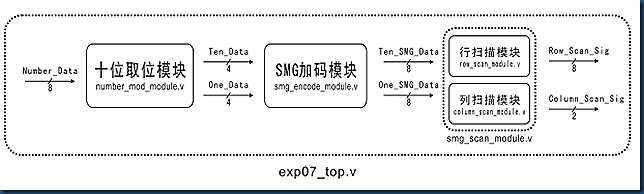

期颐完成上图所示个各模块,构成数码管驱动电路。

模块说明:

1.取位模块:number_mod_module.v

简单说就是我的输入数据时00-99的两位数,那么我要分别取出十位和个位的数字待用,这个模块实现很简单,用求商/得到十位的数字,用求余%得到个位的数字。

2. 译码模块:smg_encoder_module.v

译码模块将我们前面得到的十位和个位数字译成数码管的7位码(若用到那个小数点,就是8位码)。这里的电路里的数码管是共阳极的,所以0有效。

3. 扫描模块:smg_scan_module.v

扫描模块分为两部分,因为是同步扫描,所以要同时选定数码管(列扫描)和显示的数字(行扫描)。这里用50Hz的频率扫描,即10ms扫描一次,符合视觉暂留。

代码

number_mod_module.v

1 /**

2 * File name: number_mod_module.v

3 *

4 */

5

6 module number_mod_module

7 (

8 clk, rst_n,

9 number_data,

10 ten_data, one_data

11 );

12

13 input clk;

14 input rst_n;

15 input [7:0] number_data;

16 output [3:0] ten_data;

17 output [3:0] one_data;

18

19 reg [31:0] rten;

20 reg [31:0] rone;

21

22 always @(posedge clk or negedge rst_n)

23 if (!rst_n)

24 begin

25 rten <= 32'd0;

26 rone <= 32'd0;

27 end

28 else

29 begin

30 rten <= number_data / 10;

31 rone <= number_data % 10;

32 end

33

34 assign ten_data = rten[3:0];

35 assign one_data = rone[3:0];

36

37 endmodule

38

smg_encoder_module.v

1 /**

2 * File name : smg_encoder_module.v

3 *

4 */

5

6 module smg_encoder_module

7 (

8 clk, rst_n,

9 ten_data, one_data,

10 ten_smg_data, one_smg_data

11 );

12

13 input clk;

14 input rst_n;

15 input [3:0] ten_data;

16 input [3:0] one_data;

17 output [7:0] ten_smg_data;

18 output [7:0] one_smg_data;

19

20 parameter _0 = 8'b1100_0000, _1 = 8'b1111_1001, _2 = 8'b1010_0100,

21 _3 = 8'b1011_0000, _4 = 8'b1001_1001, _5 = 8'b1001_0010,

22 _6 = 8'b1000_0010, _7 = 8'b1111_1000, _8 = 8'b1000_0000,

23 _9 = 8'b1001_0000;

24

25 reg [7:0] rten_smg_data;

26

27 always @(posedge clk or negedge rst_n)

28 if (!rst_n)

29 begin

30 rten_smg_data <= 8'b1111_1111;

31 end

32 else

33 case (ten_data)

34

35 4'd0: rten_smg_data <= _0;

36 4'd1: rten_smg_data <= _1;

37 4'd2: rten_smg_data <= _2;

38 4'd3: rten_smg_data <= _3;

39 4'd4: rten_smg_data <= _4;

40 4'd5: rten_smg_data <= _5;

41 4'd6: rten_smg_data <= _6;

42 4'd7: rten_smg_data <= _7;

43 4'd8: rten_smg_data <= _8;

44 4'd9: rten_smg_data <= _9;

45 endcase

46

47 reg [7:0] rone_smg_data;

48

49 always @(posedge clk or negedge rst_n)

50 if (!rst_n)

51 begin

52 rone_smg_data <= 8'b1111_1111;

53 end

54 else

55 case (one_data)

56 4'd0: rone_smg_data <= _0;

57 4'd1: rone_smg_data <= _1;

58 4'd2: rone_smg_data <= _2;

59 4'd3: rone_smg_data <= _3;

60 4'd4: rone_smg_data <= _4;

61 4'd5: rone_smg_data <= _5;

62 4'd6: rone_smg_data <= _6;

63 4'd7: rone_smg_data <= _7;

64 4'd8: rone_smg_data <= _8;

65 4'd9: rone_smg_data <= _9;

66 endcase

67

68 assign ten_smg_data = rten_smg_data;

69 assign one_smg_data = rone_smg_data;

70

71 endmodule

72

73

smg_scan_module.v

1 /**

2 * File name: smg_scan_module.v

3 *

4 */

5

6 module smg_scan_module

7 (

8 clk, rst_n,

9 ten_smg_data, one_smg_data,

10 row_scan_sig, column_scan_sig

11 );

12

13 input clk;

14 input rst_n;

15 input [7:0] ten_smg_data;

16 input [7:0] one_smg_data;

17 output [7:0] row_scan_sig;

18 output [1:0] column_scan_sig;

19

20 row_scan_module U1

21 (

22 .clk (clk),

23 .rst_n (rst_n),

24 .ten_smg_data (ten_smg_data),

25 .one_smg_data (one_smg_data),

26 .row_scan_sig (row_scan_sig)

27 );

28

29 column_scan_module U2

30 (

31 .clk (clk),

32 .rst_n (rst_n),

33 .column_scan_sig (column_scan_sig)

34 );

35

36 endmodule

37

column_scan_module.v

1 /**

2 * File name : column_scan_module.v

3 *

4 */

5

6 module column_scan_module

7 (

8 clk, rst_n, column_scan_sig

9 );

10

11 input clk;

12 input rst_n;

13 output [1:0] column_scan_sig;

14

15 parameter T10MS = 18'd199_999;

16

17 reg [17:0] count;

18

19 always @(posedge clk or negedge rst_n)

20 if (!rst_n)

21 count <= 18'd0;

22 else if (count == T10MS)

23 count <= 18'd0;

24 else

25 count <= count + 18'b1;

26

27 reg [1:0] t;

28

29 always @(posedge clk or negedge rst_n)

30 if (!rst_n)

31 t <= 2'd0;

32 else if (t == 2'd2)

33 t <= 2'd0;

34 else if (count == T10MS)

35 t <= t + 1'b1;

36

37 reg [1:0] rcolumn_scan;

38

39 always @(posedge clk or negedge rst_n)

40 if (!rst_n)

41 rcolumn_scan <= 2'b10;

42 else if (count == T10MS)

43 case (t)

44

45 2'd0: rcolumn_scan <= 2'b10;

46 2'd1: rcolumn_scan <= 2'b01;

47

48 endcase

49

50 assign column_scan_sig = rcolumn_scan;

51

52 endmodule

53

row_scan_module.v

1 /**

2 * File name : row_scan_module.v

3 *

4 */

5

6 module row_scan_module

7 (

8 clk, rst_n,

9 ten_smg_data, one_smg_data,

10 row_scan_sig

11 );

12

13 input clk;

14 input rst_n;

15 input [7:0] ten_smg_data;

16 input [7:0] one_smg_data;

17 output [7:0] row_scan_sig;

18

19 parameter T10MS = 18'd199_999;

20

21 reg [17:0] count;

22

23 always @(posedge clk or negedge rst_n)

24 if (!rst_n)

25 count <= 18'd0;

26 else

27 count <= count + 18'b1;

28

29 reg [1:0] t;

30

31 always @(posedge clk or negedge rst_n)

32 if (!rst_n)

33 t <= 2'd0;

34 else if (t == 2'd2)

35 t <= 2'd0;

36 else if (count == T10MS)

37 t <= t + 1'b1;

38

39 reg [7:0] rdata;

40

41 always @(posedge clk or negedge rst_n)

42 if (!rst_n)

43 rdata <= 8'd0;

44 else if (count == T10MS)

45 case(t)

46

47 2'd0: rdata <= ten_smg_data;

48 2'd1: rdata <= one_smg_data;

49

50 endcase

51

52 assign row_scan_sig = rdata;

53

54 endmodule

55

exp07_top.v

1 /**

2 * File name: exp07_top.v

3 *

4 */

5

6 module exp07_top

7 (

8 clk, rst_n,

9 number_data,

10 row_scan_sig, column_scan_sig

11 );

12

13 input clk;

14 input rst_n;

15 input [7:0] number_data;

16 output [7:0] row_scan_sig;

17 output [1:0] column_scan_sig;

18

19 wire [3:0] ten_data;

20 wire [3:0] one_data;

21

22 number_mod_module U1

23 (

24 .clk (clk),

25 .rst_n (rst_n),

26 .number_data (number_data),

27 .ten_data (ten_data),

28 .one_data (one_data)

29 );

30

31 wire [7:0] ten_smg_data;

32 wire [7:0] one_smg_data;

33

34 smg_encoder_module U2

35 (

36 .clk (clk),

37 .rst_n (rst_n),

38 .ten_data (ten_data),

39 .one_data (one_data),

40 .ten_smg_data (ten_smg_data),

41 .one_smg_data (one_smg_data)

42 );

43

44 smg_scan_module U3

45 (

46 .clk (clk),

47 .rst_n (rst_n),

48 .ten_smg_data (ten_smg_data),

49 .one_smg_data (one_smg_data),

50 .row_scan_sig (row_scan_sig),

51 .column_scan_sig (column_scan_sig)

52 );

53

54 endmodule

55

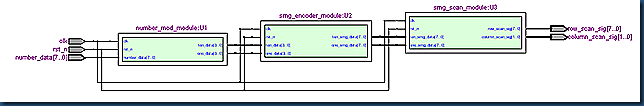

RTL图

小结

本实验同样是低级建模,特点是模块多,各模块功能单一,易读易修改,各个模块的构造容易,直接.用简单的模块组合起来,实现复杂的功能.