看到代码里面的:

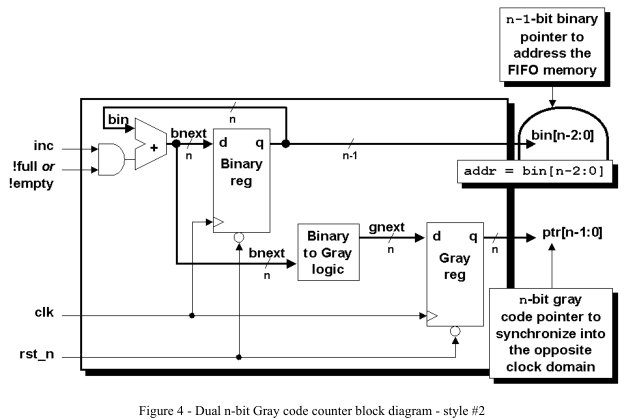

assign wgraynext = (wbinnext>>1) ^ wbinnext;

感到有点奇怪,毕竟卡诺图转成4种基本gate容易,但是Reed Muller则很好的直接用XOR给出答案。这在点击打开给出了解释,我还下了这本书,通俗易懂,有些trick很有意思。例如这种棋盘型的卡诺图以后就可以直接用Reed Muller了。

注意:full的条件要多一句,因为gray code的最高位并不队称。

代码和波形都贴在gitlab里面了。两个的输出都是一致的。

看到代码里面的:

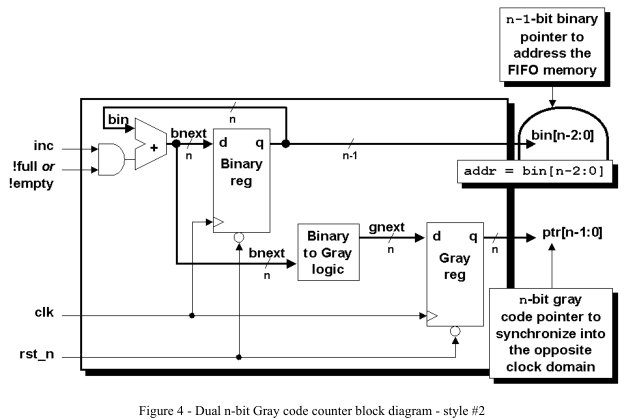

assign wgraynext = (wbinnext>>1) ^ wbinnext;

感到有点奇怪,毕竟卡诺图转成4种基本gate容易,但是Reed Muller则很好的直接用XOR给出答案。这在点击打开给出了解释,我还下了这本书,通俗易懂,有些trick很有意思。例如这种棋盘型的卡诺图以后就可以直接用Reed Muller了。

注意:full的条件要多一句,因为gray code的最高位并不队称。

代码和波形都贴在gitlab里面了。两个的输出都是一致的。