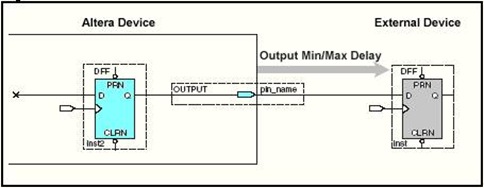

定义Output Maximum Delay(OMD)和Output Minimum Delay(OmD)。

OMD定义为数据离开FPGA输出脚、到达外部触发器数据输入端的时间延迟。

同理定义OmD。

一、Clock Setup Slack

根据之前的结论:

Clock Setup Slack = SR + Tcs(min) – uTsu – uTco – Td(max) (1)

调整如下:

1、SR不变;

2、Td为从FPGA管脚到外部寄存器输入端的路径延时;

3、Tcs为时钟到外部寄存器时钟输入端相对于时钟到FPGA时钟管脚的时钟抖动;

4、Tsu代替uTsu,Tsu是外部寄存器的clock-to-output时间;

5、Tco代替uTco,Tco反应的是FPGA输出管脚处时钟与数据的时序关系;Tco的值应由Quartus II布线布局后计算得出。

新的Clock Setup Slack可以表示为:

Clock Setup Slack = SR – Tco – (Td_ext(max) + Tsu_ext – Tcs(min)) (2)

可定义OMD为:

OMD = Td_ext(max) + Tsu_ext – Tcs(min) (3)

这样,FPGA输出数据到外部的Clock Setup Slack可以表示为:

Clock Setup Slack = SR – Tco – OMD (4)

二、Clock Hold Slack

按照之前结论:

Clock Hold Slack = Td(min) – HR – Tcs(max) – uThd + uTco (5)

调整的时候,Thd代替uThd。Thd表示外部寄存器的保持时间要求。

Tco的调整与Clock Setup Slack的相同。

那么Clock Hold Slack可以表示为:

Clock Hold Slack = Td_ext(min) – Thd_ext – Tcs_ext(max) – HR + Tco (6)

定义OmD为:

OmD = Td_ext(min) – Thd_ext – Tcs_ext(max) (7)

那么,FPGA输出数据到外部的Clock Hold Slack可以表示为:

Clock Hold Slack = OmD – HR + Tco (8)