1、以8位短整数为例,短整数的最高位是符号位,符号位的正负表示了该值是“正还是负”?。正值的表示方法是以0开始的8位二进制数,反之负值的表示方法是用正数的补码来表示。例如:+127 亦即8'b0111_1111;那么-127 亦即8'b1000_0001(通过相应正数的按位取反加1得到,符号位也要取反);

2、正值可以进行求反又加一之后成为负值。那么负值如何变成正值?同样的一个道理“负值求反又加一后,成为正值”。

3、我们知道短整数的位宽为,8 ,亦即取值范围是0~255。但是符号位的出现吃掉了最高位,所以造成取值范围变成2^7=128,即0到127。

4、在Modelsim中显示数据时,数据格式Decimal表示有符号数(-128~+127),Unsigned表示无符号数(0~255)(二者最终都是整数方式显示)。也即:Modelsim只能对最终结果实现转化,在数据处理过程中则需要人为编程实现正数或者负数。

除法实现及仿真:

1 module divider(Reset,Clock,Start_sig,Done_sig,A,B,C,D); 2 3 input Reset,Clock,Start_sig; 4 output Done_sig; 5 input [7:0] A,B; 6 output [7:0] C,D; 7 8 reg [7:0] A_temp,B_temp,C,D; 9 reg Symbol,Done_sig; 10 reg [2:0] i; 11 12 always@(posedge Clock or negedge Reset) 13 begin 14 if(!Reset) 15 begin 16 C<=8'b0; 17 D<=8'b0; 18 i<=3'b0; 19 Done_sig<=1'b0; 20 end 21 else if(Start_sig) 22 case(i) 23 0:begin 24 Symbol<=A[7]^B[7]; 25 A_temp<=A[7]?(~A+8'b1):A; 26 B_temp<=B[7]?B:(~B+8'b1); 27 i<=i+1'b1; 28 end 29 1:begin 30 if(A_temp<(~B_temp+8'b1)) begin D<=A_temp;i<=i+1'b1;C<=Symbol?(~C+1'b1):C;end 31 else begin A_temp<=A_temp+B_temp;C<=C+8'b1;end 32 end 33 2:begin 34 Done_sig<=1'b1;i<=i+1'b1; 35 end 36 3:begin 37 Done_sig<=1'b0;i<=1'b0; 38 end 39 endcase 40 end 41 42 endmodule

1 `timescale 1ns/1ps 2 module divider_tb(); 3 reg Reset,Clock,Start_sig; 4 reg [7:0] A,B; 5 wire Done_sig; 6 wire [7:0] C,D; 7 8 divider U( 9 .Reset(Reset), 10 .Clock(Clock), 11 .Start_sig(Start_sig), 12 .A(A), 13 .B(B), 14 .C(C), 15 .D(D), 16 .Done_sig(Done_sig)); 17 18 initial 19 begin 20 Reset=0;#10 Reset=1; 21 Clock=0;forever #10 Clock=~Clock; 22 end 23 24 25 always@(posedge Clock or negedge Reset) 26 if(!Reset) 27 begin 28 A<=8'b0; 29 B<=8'b0; 30 Start_sig<=1'b0; 31 end 32 else 33 if(Done_sig) 34 35 Start_sig<=1'b0; 36 37 else 38 begin 39 A<=8'b00110110; 40 B<=8'b11111001; 41 Start_sig<=1'b1; 42 end 43 44 endmodule

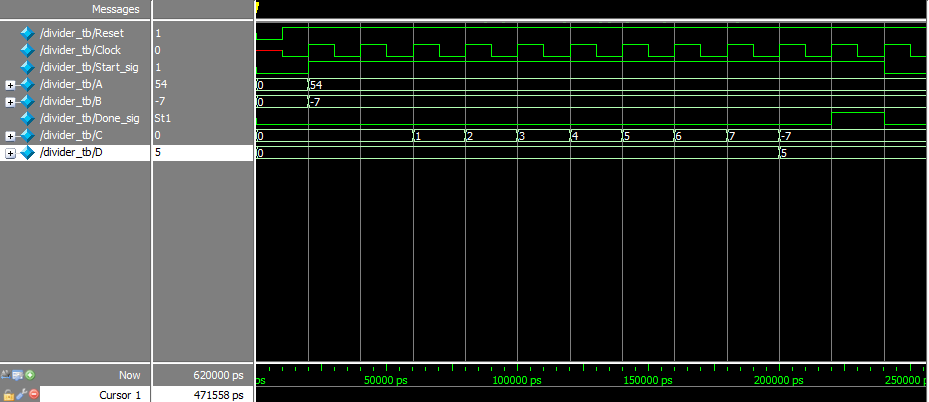

Q9.0,M6.4a的仿真结果:

出现的问题:为什么昨天功能仿真是对的,而今天时序仿真得到的商却是零?