FPGA的片内有很多的存储器资源,可以配置成单端口的ROM、RAM和双端口的ROM、RAM,以及移位寄存器和FIFO等。在学习过程中,笔者遇到过几个小问题,总结如下:

片内是不是有ROM或者RAM?

个人观点:片内没有ROM或者RAM的,有的只是一些功能比较强大的存储器块,可以通过配置变成我们想要的功能。例如将RAM的wren端子和data端子直接接地,那么就变成了ROM。片内有的是一些M9K、M4K等等,M9K代表容量为9Kbits的存储器。

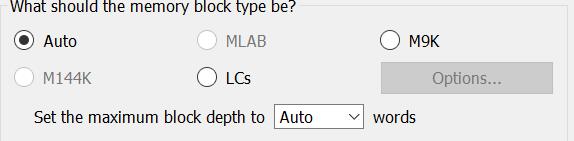

选择组成存储器的类型以及存储器块的最大深度?

图1

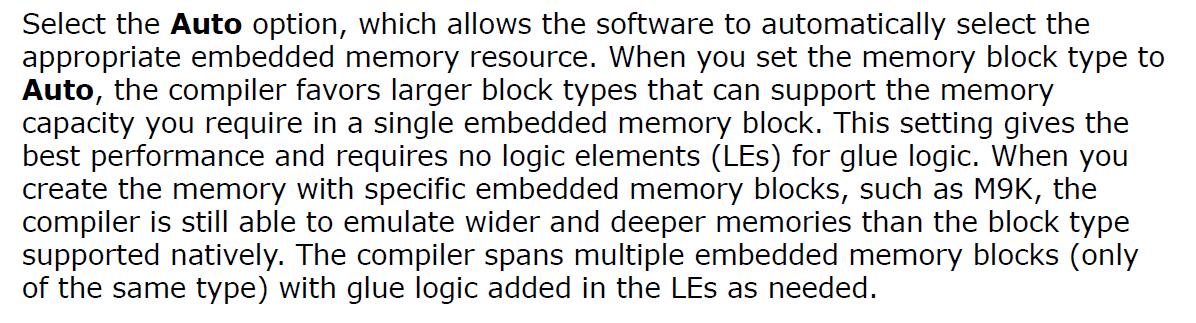

个人观点:对于这两个的话,建议选择“AUTO”。下图是官方给出的建议:

图2

图3

对于RAM和ROM模式,q输出段是否应该被寄存?

个人观点:其实寄存也好,不被寄存也好,结果只是输出的是不是会延迟一个时钟周期。但是笔者建议q应该被寄存一下。在RAM或者ROM中,地址被寄存,而最终的输出是用的组合逻辑进行输出,如果q被引用时也经过了大量的逻辑,那么存储器中的逻辑和被引用时的逻辑就会组成一个比较大的逻辑,整个设计的速度就会变慢。

对于RAM和ROM模式,是否应该引出rden信号?

个人观点:之前我在学习中,rden从来没有引出过,因为自己的设计自己知道,什么时候去读,只要正确的时序就可以了,近期接触到官方文档后,官方推荐引出rden信号,用于降低功耗。

图4

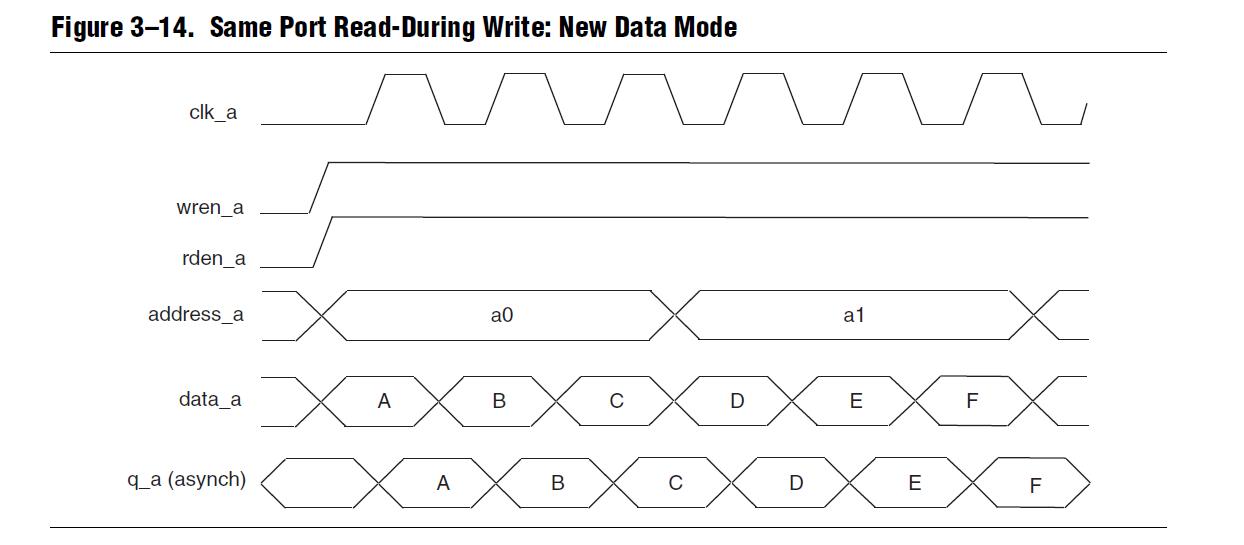

在RAM模式中,如果出现对于同一个地址进行读写会出现什么情况?

图5

个人观点:之前学习中,这个界面几乎从来没有关系过,直接都是略过,保持默认值不变。近期考虑这个问题,查看官方手册,此项可以选择New Data、Old Data和Donot Care,默认值是New Data。

这个问题可以分为两个方向考虑:

同一个端口同时读写,那么时序如下:

图6

图7

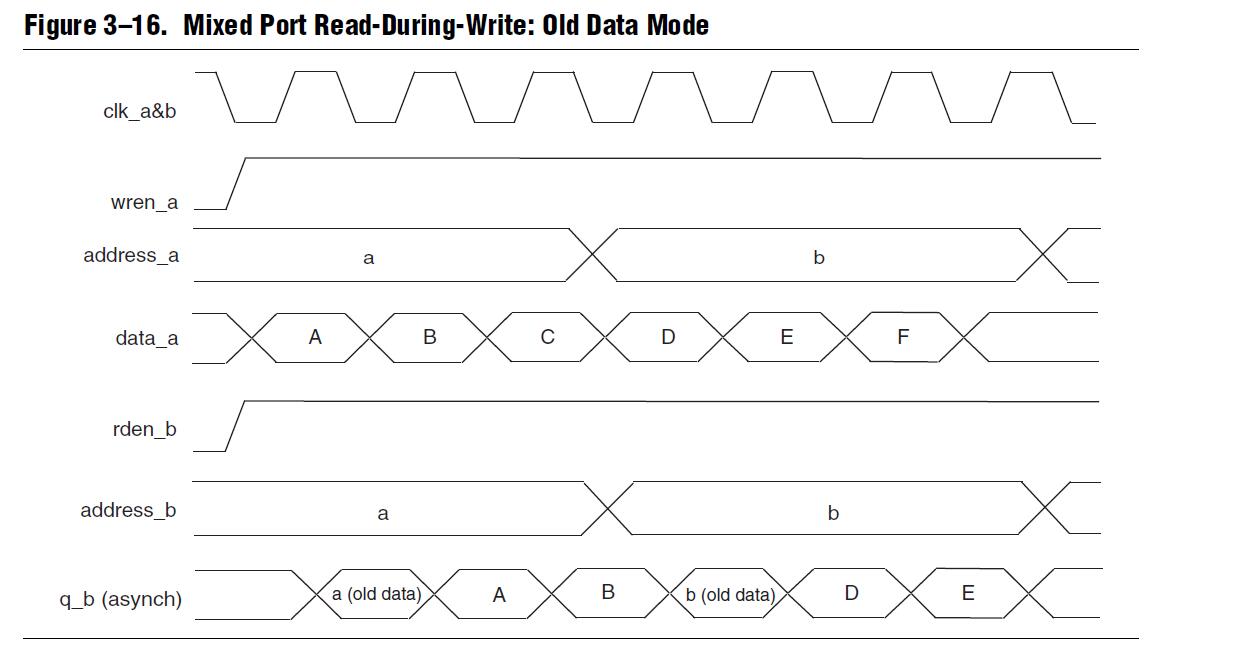

对于不同的端口来说,只有Old DATA,don’t care就不关心了。

图8

对于初始化文件.hex或者.mif文件,当存储器发生写入时,文件内容没有发生改变?

个人观点:.hex或者.mif文件并没有被下板,只是综合器在综合时,将文件中的内容读取出来,配置给存储器而已,本身文件和下板没有关系,所以在仿真也好,或者下板也好,对于存储器的写入并不会改变文件中的值。对于经常使用.txt初始化的设计者,结果也是一样的,.txt的内容并不会被改变。

使用reg [n-1:0] reg_name [m-1:0]定义存储器。

个人观点:此种方法是可以定义存储器的,但是经过笔者实际测试,不同的深度和位宽会影响综合器选择存储器块还是LE构成,并且会综合器在综合过程中会产生很多的警告。笔者在公司研发,使用此种方式进行存储器定义使用,被领导批评过。具体的原因有待发掘,在此,笔者建议设计者在设计时,如果要用到存储器,利用IPCore的插件向导完成还是比较好的。

笔者将上文中所用的存储器官方资料都放到了,QQ群:173560979群文件中,如果有需要的可以下载。

笔者水平有限,如果设计中,有什么不妥的地方,恳请大佬们指出来。

欢迎加好友探讨QQ(奋斗的小孩郝旭帅):746833924,QQ群:173560979。