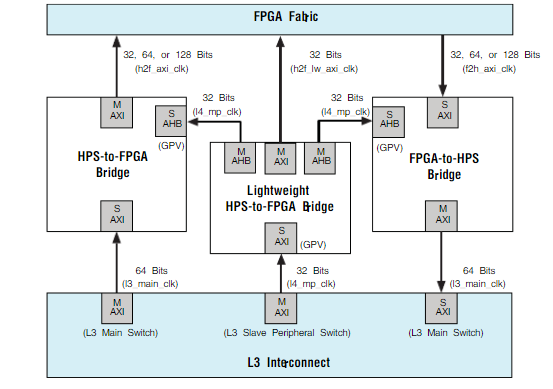

DE1作为ARM+FPGA的组合,ARM和FPGA之间通信,两个区块间有三个通道可以让两部分实现传输数据,统称为 HPS-FPGA AXI Bridges。

分别为:

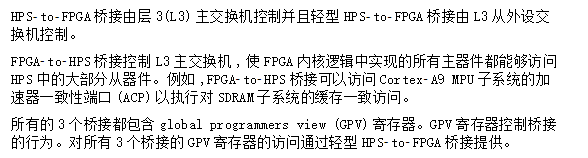

FPGA-to-HPS Bridge

HPS-to-FPGA Bridge

Lightweight HPS-to-FPGA Bridge

FPGA-to-HPS,HPS-to-FPGA 这两个 Bridge 为 FPGA 跟 HPS 间宽带高速的传输通道。

Lightweight HPS-to-FPGA 则为较低速的控制通道

HPS-FPGAAXI桥接支持FPGA内核逻辑中的主器件与HPS逻辑中的从器件进行通信(反之亦然)。例如,您可以例化FPGA内核逻辑中额外的存储器或外设,并且属于HPS逻辑中组件的主接口可以访问它们。也可以例化(例如FPGA内核逻辑中NiosII处理器)的组件并且它们的主接口可以访问HPS逻辑中的存储器或外设。

毎个桥接都包含一-个AXI主从接口対,其中一个接口面向(exposed to )FPGA内核逻辑以及另一个接口面向HPS逻辑。HPS-to-FPGA Bridge和Lightweight HPS-to-FPGA桥接提供(expose)一个AXI主接口,可以连接到FPGA内核逻辑中的AXI或Avalon- JM从接口。

FPGA- to- HPS桥接提供- -个AXI从接口,可以達接到FPGA内核還緝中的AXI主器件或Avalon-MM接口。