设计“十字路口交通灯管理系统”

项目:一条主干道,一条乡间公路。组成十字路口,要求优先保证主干道通行。

设计要求:

(1) 有MR(主红)、MY(主黄)、MG(主绿)、CR(乡红)、CY(乡黄)、CG(乡绿)六盏交通灯需要控制;

(2) 交通灯由绿→红有4秒黄灯亮的间隔时间,由红→绿没有间隔时间;

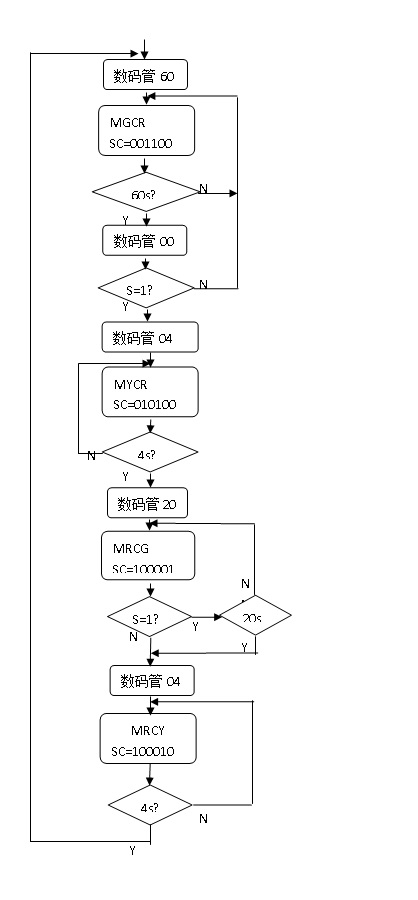

(3) 系统有MRCY、MRCG、MYCR、MGCR四个状态;

(4) 乡间公路右侧各埋有一个传感器,当有车辆通过乡间公路时,发出请求信号S=1,其余时间S=0;

(5) 平时系统停留在MGCR(主干道通行)状态,一旦S信号有效,经MYCR(黄灯状态)转入MRCG(乡间公路通行)状态,但要保证MGCR的状态不得短于一分钟(一分钟以后随时待命接收S信号);

(6) 一旦S信号无效,系统脱离MRCG状态。随即经MRCY(黄灯状态)进入MGCR状态,即使S信号一直有效,MRCG状态也不得长于20秒钟。

分析:

l 系统设置一个两位BCD码倒计时计数器(计数脉冲1HZ),用于记录各状态持续时间;

l 因为各状态持续时间不一致,所以上述计数器应置入不同的预置数;

l 倒计时计数值输出至二个数码管显示;

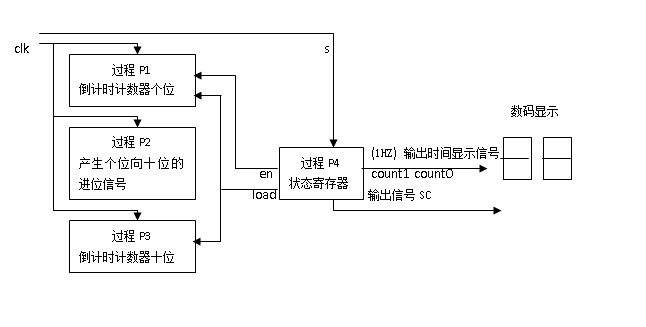

l 程序共设置4个过程P1、P2、P3、P4:

① 过程P1、P2和P3构成两个带有预置数功能的十进制计数器,其中P1和P3分别为个位和十位计数器,P2产生个位向十位的进位信号;

② 过程P4是状态寄存器,控制状态的转换,并输出6盏交通灯的控制信号。

用Rerilog语言编写程序实现“十字路口交通灯管理系统”的原理框图如下:

输出SC = MR MY MG CR CY CG 初值SC=001100

状态State: mgcr → mycr → mrcg → mrcy

过程P4流程图:

我的解答v1版本:

1 //module midtest(ge_wei, shi_wei, clk, en, s); 2 module midtest(ge_wei, shi_wei, current_state, clk, en, s); 3 output reg [7:0] ge_wei, shi_wei; 4 // output [7:0] timer; 5 output [7:0] current_state; 6 input clk,s,en; 7 // parameter mgcr=6'b001100, mycr=6'b010100, 8 // mrcg=6'b100001, mrcy=6'b100010; 9 parameter mgcr=6'b000000, mycr=6'b000001, 10 mrcg=6'b000010, mrcy=6'b000011; 11 reg [7:0] timer; 12 reg [7:0] current_state; 13 initial begin 14 timer = 0; 15 ge_wei = 0; shi_wei = 0; 16 current_state <= mgcr; 17 end 18 19 always @(negedge clk) begin 20 if(en) begin 21 case(current_state) 22 mgcr: begin 23 timer = timer + 1; 24 if(s) begin 25 if(timer >= 60) begin 26 timer = 0; 27 current_state <= mycr; 28 end 29 end 30 end 31 mycr: begin 32 timer = timer + 1; 33 if(timer >= 4) begin 34 timer = 0; 35 current_state <= mrcg; 36 end 37 end 38 mrcg: begin 39 timer = timer + 1; 40 //if(timer >= 20 || !s) begin 41 if(timer >= 20) begin 42 timer = 0; 43 current_state = mrcy; 44 end 45 end 46 mrcy: begin 47 timer = timer + 1; 48 if(timer >= 4) begin 49 timer = 0; 50 current_state <= mgcr; 51 end 52 end 53 endcase 54 ge_wei = timer%10; 55 shi_wei =timer/10; 56 end 57 end 58 59 60 endmodule

19:48:19|| v2 版本

1 //module midtest(ge_wei, shi_wei, clk, en, s); 2 module midtest(ge_wei, shi_wei, current_state, clk, en, s); 3 output reg [7:0] ge_wei, shi_wei; 4 // output [7:0] timer; 5 output [7:0] current_state; 6 input clk,s,en; 7 // parameter mgcr=6'b001100, mycr=6'b010100, 8 // mrcg=6'b100001, mrcy=6'b100010; 9 parameter mgcr=6'b000000, mycr=6'b000001, 10 mrcg=6'b000010, mrcy=6'b000011; 11 reg [7:0] timer; 12 reg [7:0] current_state; 13 initial begin 14 timer = 0; 15 ge_wei = 0; shi_wei = 0; 16 current_state <= mgcr; 17 end 18 19 always @(negedge clk) begin 20 if(en) begin 21 case(current_state) 22 mgcr: begin 23 timer = timer + 1; 24 if(s) begin 25 if(timer >= 60) begin 26 timer = 0; 27 current_state <= mycr; 28 end 29 end 30 end 31 mycr: begin 32 timer = timer + 1; 33 if(timer >= 4) begin 34 timer = 0; 35 current_state <= mrcg; 36 end 37 end 38 mrcg: begin 39 timer = timer + 1; 40 //if(timer >= 20 || !s) begin 41 if(timer >= 20) begin 42 timer = 0; 43 current_state = mrcy; 44 end 45 end 46 mrcy: begin 47 timer = timer + 1; 48 if(timer >= 4) begin 49 timer = 0; 50 current_state <= mgcr; 51 end 52 end 53 endcase 54 ge_wei = timer%10; 55 shi_wei =timer/10; 56 end 57 end 58 59 60 endmodule