硬件

1. 网口

网口使用4根信号线:两根发送,两根接收。一对信号线中一根承载0——+2.5V信号电压,而另一根负载的电压是0——-2.5V,因此可产生一个5Vpp的信号差。RJ45中有用的就是4根信号线。

网络接口控制器与RJ45间需要用网络隔离变压器连接,网络隔离变压器起信号传输、阻抗匹配、波形修复、杂波抑制以及高电压隔离等作用,以确保系统安全。

PHY是物理接口收发器,它实现物理层。

PHY在发送数据时,收到MAC过来的数据(对PHY而言,没有帧的概念,都是数据而不管什么地址、数据还是CRC),每4bit就增加1bit检错码,然后把并行数据转化为串行流数据,再按照物理层的编码规则把数据编码,再变为模拟信号把数据发送出去。

隔离变压器把PHY发送过来的差分信号用差模耦合的线圈耦合滤波以增强信号,并通过电磁场的转换耦合到连接网线的另一端。

2. 控制

网卡工作在OSI的最后两层,物理层(PHY)和数据链路层(MAC)。DM9161是一个物理层单芯片(A PHY),通过MII(Media Independent Interface),DM9161A连接MAC layer。

9260内嵌MAC层。

DM9161A contains the entire physical layer functions of 100BASE-Tx as defined by IEEE802.3u。包括PCS(Physical Coding Sublayer),PMA(Physical Medium Attachment),TP-PMD(Twisted Pair Medium Dependent Sublayer),ENC/DEC(10BASE-TX Encoder/Decoder)和TPMAU(Twisted Pair Media Access Unit)。

MII管理接口包含两根信号线:MDC和MDIO,通过它,MAC层控制器可以访问物理层芯片的寄存器,并通过这些寄存器来对物理层芯片进行控制和管理。MDC与TX_CLK和RX_CLK无任何关系。MDIO是一根双向数据线,用来传送MAC层的控制信息和物理层的状态信息。MDIO数据与MDC时钟同步,在MDC上升沿有效。

注:MII&RMII

MII (Media Independent Interface(介质无关接口),或称为媒体独立接口,它是IEEE-802.3定义的以太网行业标准。它包括一个数据接口,以及一个MAC和PHY之间的管理接口。

数据接口包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII数据接口总共需要16个信号。

管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。MII Management interface只有两条信号线。

MII以4位半字节方式双向传输数据,时钟频率25MHz,其工作速率可达100Mb/s。

RMII是简化的MII接口 ,在数据的收发上它比MII接口少了一倍的信号线,所以它一般要求是50兆的总线时钟 。RMII一般用在多端口的交换机,它不是每个端口安排收、发两个时钟,而是所有的数据端口公用一个时钟用于所有端口的收发 ,这里就节省了不少的端口数目。RMII的一个端口要求7个数据线 ,比MII少了一倍,所以交换机能够接入多一倍数据的端口

RMII用于传输以太网包,在RMII接口是2bit的,在以太网的PHY里需要做串并转换、编解码等才能在双绞线和光纤上进行传输。

3. 引脚

PCS:Physical Coding Sub Layer

PMA:Physical Medium Attachment 物理介质附件

注:DM9161不同于DM9161A,部分引脚定义不同。

共48Pin,其中Pin45保留未用。

1) MII介质无关接口21Pin。

数据接口:发送器信号:数据信号TXER/TXD[4], TXD[0:3]

时钟信号TXCLK

控制信号 TXEN

接收器信号:数据信号 RXER/RXD[4]/RPDR,RXD[0:3]/PHYAD[0:3]

时钟信号RXCLK

控制信号 RXDV/TESTMODE

载波检测信号CRS/RHYAD[4]

碰撞检测信号COL/RMII

注:当选择RMII时,COL需上拉。(上电后,测试为低电平—路由器)

For half-duplex operation, a collision is detected when the transmit and receive channels are active simultaneously. When a collision has been detected, it will be reported by the COL signal on the MII interface. Collision detection is disabled in Full Duplex operation.

管理接口:时钟信号MDC

数据信号MDIO

其他功能接口:复位信号RESET

状态中断输出MDINTR

LED模式选择LEDMODE

MII接口信号:

RMII接口信号:

2) 物理层接口引脚,4Pin。

发送端接口TX+、TX-

接收端接口RX+、RX-

3) 时钟和偏置引脚4Pin

带隙引脚:带隙地面BGRESG,带隙电压基准欧姆电阻6.8K BGRES

晶振引脚:晶振输入XT1,晶振输出XT2(REF_CLK输入RMII模式)

4) LED引脚3Pin

全/半双工指示引脚:FDX/COL LED/OP0

10/100带宽指示引脚:SPEED LED/OP1

连接指示引脚:LINK/ACT LED/OP2

实测上电时N1_LED0,N1_LED1,N1_LED2为高电平(约3.4V),故采用Auto-negotiation enables all capabilities,支持自动协商(接口类型(10M/100M),工作方式(半双工/全双工))。

5) 电源引脚13Pin

模拟电源引脚:模拟接收电源AVDD 1、2

模拟发送电源AVDD 9

模拟接收地 AGND 5

模拟发送地 AGND 6

模拟substrate地 AGND 46

数字电源引脚:数字电源DVDD

数字地 DGND

6) 模式引脚2Pin

掉电模式引脚:PWRDWN

电缆状态/连接状态引脚CABLESTS/LINKSTS

动态MDIX控制引脚DISMDIX

注:MDI/MDIX为网线连接类型,MDI代表直连(straight through),MDIX代表交叉连接(cross over)。The DM9161A supports the automatic detect cable connection type, MDI/MDIX.

注:The DM9161A supports the automatic detect cable connection type, MDI/MDIX (straight through/cross over). A manual configuration by register bit for MDI or MDIX is still accepted. When set to automatic, the polarity of MDI/MDIX controlled timing is generated by a 16-bits LFSR. The switching cycle time is located from 200ms to 420ms. The polarity control is always switch until detect received signal. After selected MDI or MDIX, the polarity status can be read by register bit (20.7).(See page33,8.12 specified config register-20 bit 7)7.3.1 Function Setting. Pin 39 is used to enable Auto MDIX function. Pull pin 39 low will enable it, and pull pin 39 high will disable it. Specified config Register 20 bit 4 (20, 4) is used by programmer to disable Auto MDIX function. Write register 20 bit 4 to “ 1 “ will disable Auto MDIX function. Its default value is “ 0 “. When the register 20 bit 4 (20, 4) is set to “ 1 “, the register 20 bit 5(20, 5) is used to select straight through or cross over mode, “ 0 “ is for straight through, and “ 1 “ is for cross over.

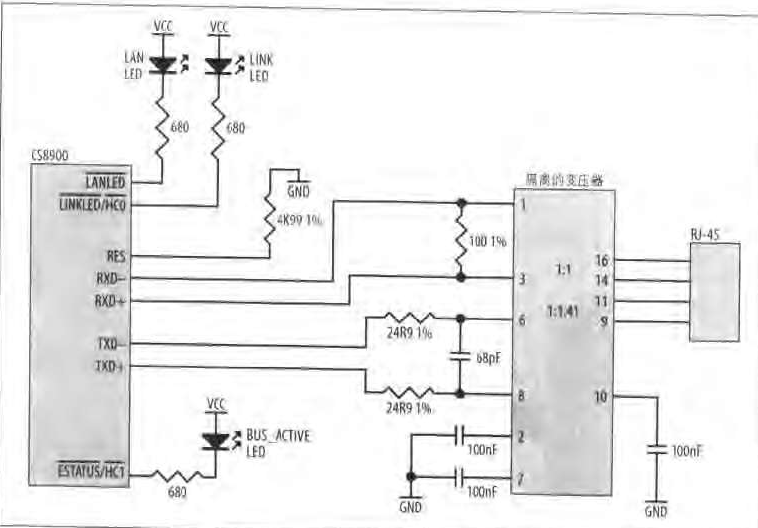

4. 电路

1)网卡部分:

2)RJ45部分

摘自“嵌入式系统硬件设计”

CS8900A通过一个隔离的变压器连接到计算机的10BASE-T端口上。如果CS8900A使用的是5V的电源,则这个变压器必须有两个绕线比为1:1和1:1.41的线圈分别供接收器和发送器使用。如果CS8900A的电源为3.3V,那么变压器供发送器使用的线圈的绕线比必须为1:2.5。发送器要求电阻值为24.9 ohms(1%)的串联终端电阻,而且发送器的两个差动端必须使用一个68pF的电容来相互去耦合。在接收器的两个差动端需要通过一个100 ohms(1%)的电阻进行并行连接。CS8900A另外还有一个引脚RES,这个引脚需要接一个4.99K ohms(1%)的下拉电阻。