AXI4从机总线分析验证之读取寄存器值

1、实验目的

利用前面所学的AXI4总线协议的理论分析,验证如何将一个PL的输入信号通过AXI发送到PS端。大致思路就是取一个按键,信号接入自建的AXI4的IP中,取代AXI4中reg_data_out成为AXI4该寄存器从地址的读取信号。然后通过PS发送到另外一个缓存寄存器,该寄存器再由PL端连接到外部电路。

2、实验操作

(1)打包IP

在tools的create IP中就可以初始化一个AXI4的slave的总线IP,进入编辑界面后即可编辑文件。这里只需要对reg_data_out的赋值语句修改即可发送输入的信号。

assign slv_reg_rden = axi_arready & S_AXI_ARVALID & ~axi_rvalid; always @(*) begin // Address decoding for reading registers case ( axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] ) 2'h0 : reg_data_out <= slv_reg0; 2'h1 : reg_data_out <= BTN; //slv_reg1; 2'h2 : reg_data_out <= slv_reg2; 2'h3 : reg_data_out <= slv_reg3; default : reg_data_out <= 0; endcase end

对应的顶层的IP口及调用口和子模块的端口声明则是纯FPGA的知识,这里不做介绍。

这里有个问题就是打包第一次的IP不会加入自定义的端口,需要第二次打包。也不知道是哪个地方设置有问题。

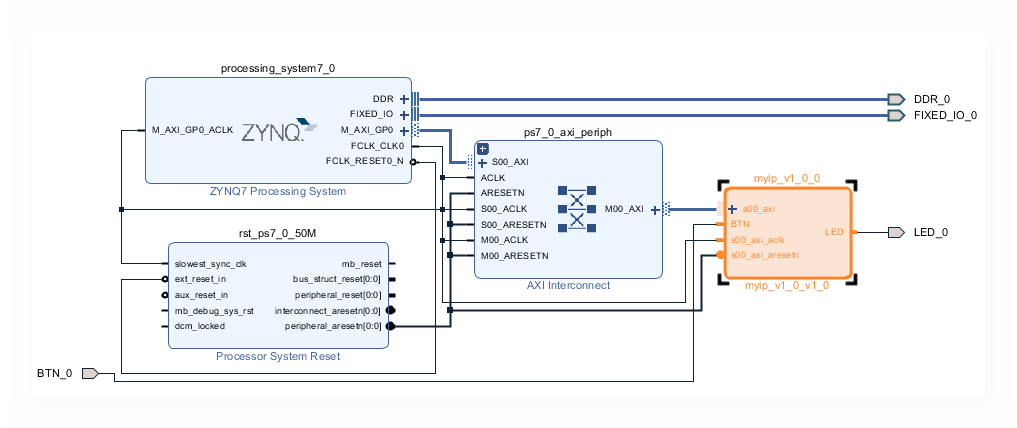

(2)完善硬件

就是调用IP后使用自动连线和自动外延。LED和BTN需要自己引出。

(3)小问题

这里综合时出现了一个缺少DCP的问题,好像是因为自建的IP没有DDR的支持,具体原因可以去网上查找。解决方法就是reset_project指令输到TCL控制台即可解决。

(4)输出bitstream,输出硬件文件xsa

在配置好端口后即可直接生成bit流。

(5)软件设计

vitis创建工程后,使用xil_Out32和xil_In32就可以实现数据的读取操作和写入操作。这里最简单的验证方法就是把读的数据写入到对应的地方。

#include "xil_io.h" #include "sleep.h" #include "stdio.h" #include "xparameters.h" #define IP_BASE XPAR_MYIP_V1_0_0_BASEADDR #define REG0_OFFSET 0 #define REG1_OFFSET 4 int main(){ int BTN; while(1){ BTN=Xil_In32(IP_BASE+REG1_OFFSET); Xil_Out32(IP_BASE+REG0_OFFSET,BTN); } }

含有main函数的文件,代码还是简单的。

3、实验结果

板级验证说明设计是成功的。reg_data_out就是数据发送的缓存器。