三极管的上拉电阻与下拉电阻

1上拉电阻

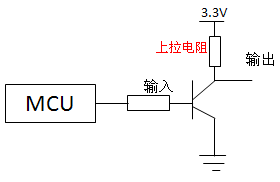

如图所示 NPN 三极管

当输入为0时,三极管截止,输出为1;

当输入为1时,三极管导通,输出为0;

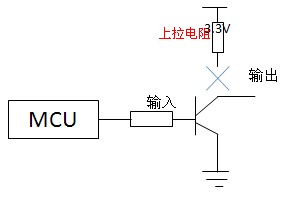

假设不存在此上拉电阻的情况,即断开(如下图所示)。此时,如果输入为0,那么三极管截止,输出未知;如果输入为1,那么三极管也不一定导通,因为三极管要求每一端都有一个电压范围。

2 下拉电阻

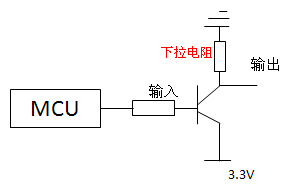

如图所示PNP三极管

当输入为0时,三极管导通,输出为1;

当输入为1时,三极管截止,输出为0;

同样,也可以分析得到,如果没有下拉电阻,输出都是不稳定的。

注意,以上输入,输出是相对于三极管而言,而不是MCU。

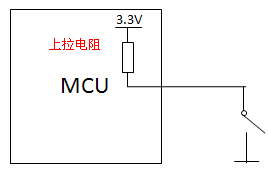

MCU内部集成的上拉/下拉电阻

当开关断开时,MCU的输入处于逻辑1状态;

当开关闭合时,MCU的输入处于逻辑0状态;

如果没有此上拉电阻,当断开时,无法确认输入状态。

综上,可以分析得到,分辨上拉下拉有一个很重要地方发电阻一端是接的电源还是地。

上拉电阻的应用:

1、当TTL 电路驱动COMS 电路时,如果TTL 电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL 的输出端接上拉电阻,以提高输出高电平的值。

2、OC 门电路必须加上拉电阻,才能使用。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在COMS 芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

拓:拉电流与灌电流

拉即泄,主动输出电流,是从输出口输出电流。

灌即充,被动输入电流,是从输出端口流入。

吸则是主动吸入电流,是从输入端口流入。

拉电流和灌电流是衡量电路输出驱动能力(注意:拉、灌都是对输出端而言的,所以是驱动能力)的参数,这种说法一般用在数字电路中。

参考文献:

<1> http://bbs.21ic.com/icview-370862-1-1.html

<2>http://bbs.21ic.com/forum.php?mod=viewthread&tid=535491&reltid=370862&pre_pos=6&ext=