EMC设计着重从三个方面入手,隔离干扰源、切断干扰途径、保护受扰体。

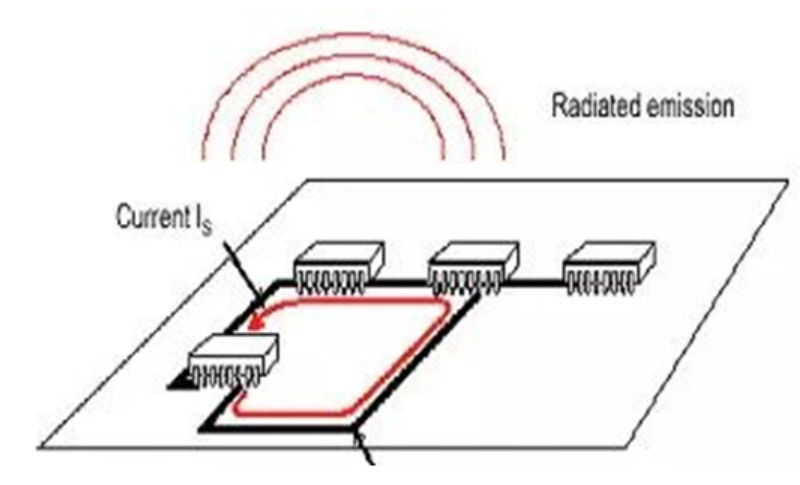

1、差模辐射:电流在信号环路中流动产生

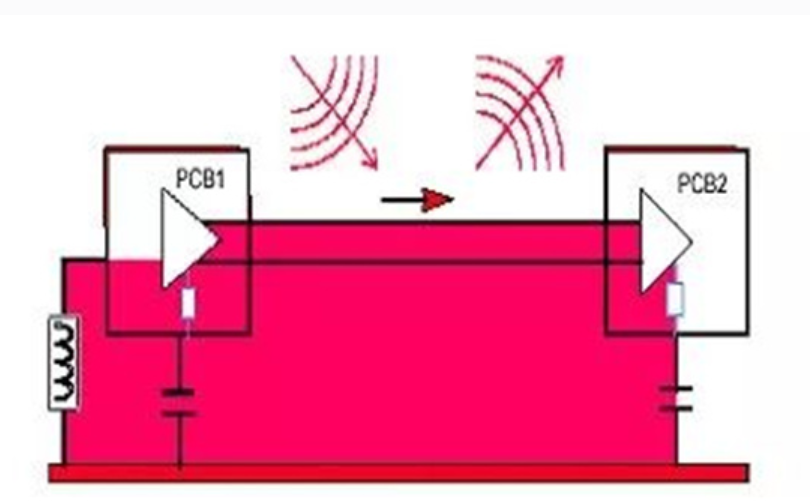

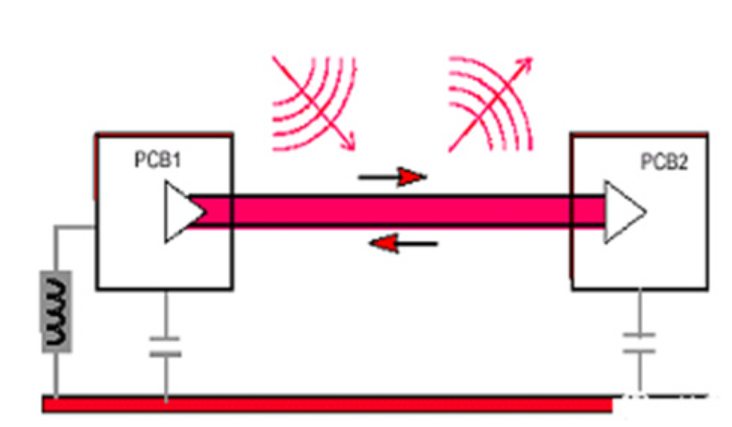

PCB的差模辐射

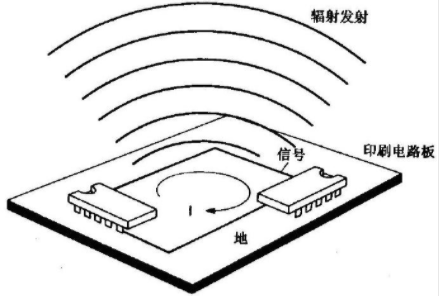

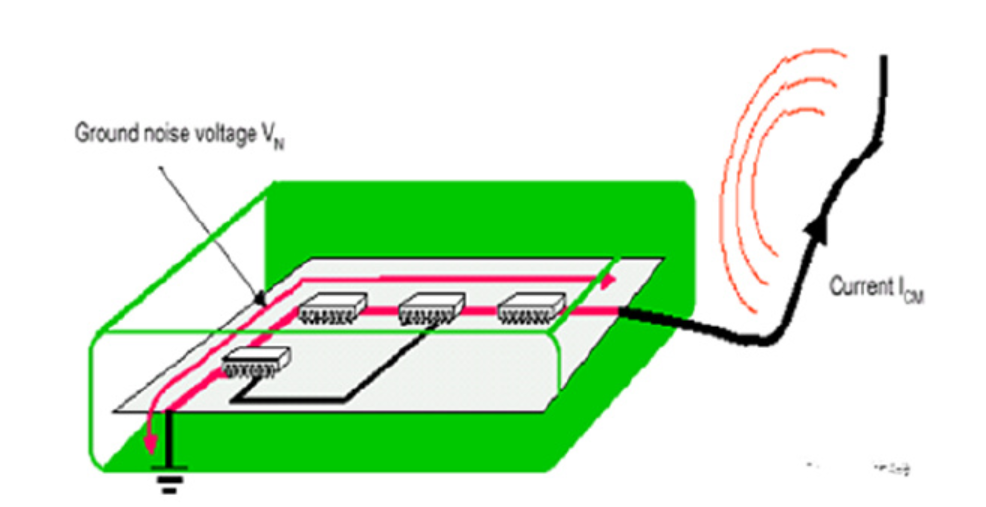

2、共模辐射:共模辐射是因电路中不需要的电压降产生的,这种电压降使系统的某些部件与“真正”的地之间形成一个共模电位差。一般来说,共模辐射来自于系统中的电缆。如图所示,辐射发射的频率由共模电势(通常是地电压)决定。

3、PCB主要产生差模辐射

4、线缆主要产生共模辐射

系统电缆的共模辐射

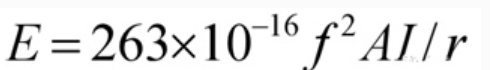

其中 :

E:电场强度(V/m)

f :电流的频率(MHz)

A:电流的环路面积(cm2)

I :电流的强度(mA)

r :测试点到电流环路的距离(m)

由公式可知,差模辐射与信号的有效频率、环路的面积、电流的大小有关,尤其场强与信号有效频率的平方成正比,因此减小差模辐射的要点由以下三项:

要点一:减小信号的频率。可以通过降频、延缓信号的边沿速率、滤波等途径实现。这是减小差模辐射最有效的途径。

要点二:减小环路面积。设计中应尽量避免出现走成环路的现象,同时对差分对信号而言,缩小对内两信号之间的间距,有助于减小环路的面积。

要点三:减小环路上电流的大小。针对这一点,选型时,尽量选择弱驱动能力的芯片,或配置引脚为弱驱动模式。

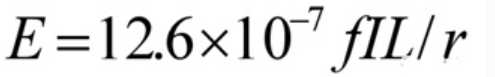

6、共模辐射电场的计算

其中 :

E:电场强度(V/m)

f :电流的频率(MHz)

L:电缆的长度(m)

I :电流的强度(mA)

r :测试点到电流环路的距离(m)

注意:连接到用户面板的信号线必须提供桥接通路,且这些信号的走线需与桥接通道重合,以提高回路完整性。

a针对共模信号,信号的返回路径最容易出现问题。除了要关注信号驱动路径外,还需加倍留意信号的返回路径。

b接口信号受扰,是辐射超标的主要原因,基于此,应使信号波动较大的电路原理接口信号,并推荐使用变压器等器件对接口信号进行隔离处理。

c尽量减少用户面板接口信号走线上的过孔。

d对晶振、时钟驱动其、PLL等器件的电源,必须通过磁珠等器件与其他器件的电源进行隔离。

e时钟信号线上使用串阻,串阻靠近发送端放置。

f差分信号对称走线,避免产生共模分量,产生共模干扰。

g跨分割平面走线,则应该在两平面间实现桥接,使信号的返回路径与桥路重合,桥接的方式可采用电容、磁珠等。

h推荐采用屏蔽电缆,应用时,屏蔽电缆的屏蔽层要良好地接地。

7、屏蔽的基本理论和设计要点

7.1屏蔽效能计算公式:

SE(dB)= R(dB)+A(dB)+B(dB)

R(dB)-reflection loss

A(dB)-absorption

B(dB)-re-reflection loss

7.2屏蔽设计的基本原则:

a、屏蔽体结构简洁,尽可能减少不必要的孔洞,尽可能不要增加额外的缝隙;

b、避免开细长孔,通风孔尽量采用圆孔并阵列排放。屏蔽和散热有矛盾时尽可能开小孔,多开孔,避免开大孔;

c、足够重视电缆的处理措施,电缆的处理往往比屏蔽本身还重要;

d、屏蔽体的电连续性是影响结构件屏蔽效能最主要的因素,相对而言,一般材料本身屏蔽性能以及材料厚度的影响是微不足道的(低频磁场例外);

e、注意控制成本;