System Level Address map figure as shown:

- CPU private address

Include : private timer and watchdog

- System Control Register

- System Level Control Register

- General Purpose Peripherals Control Register

Virtual Address Map to Physical Address

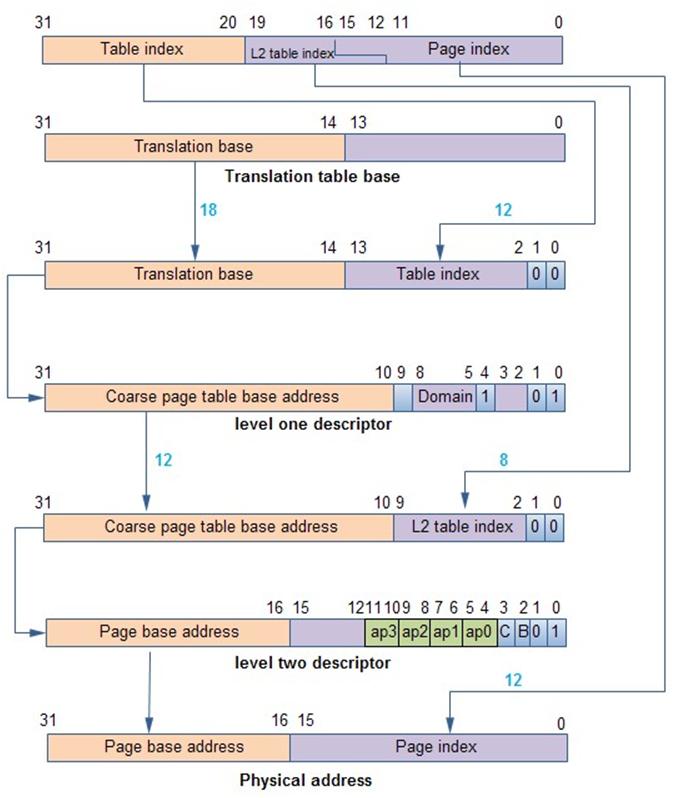

ARM cortex cpu use 2 level translation table to locate the actual page item location. The TTB is saved in coprocessor CP15 C2 register.

VA[31:20] : 12 bit stands for 4096 items, L1 table block is 1MB, thus the 12 bit can express the total 4G memory.

VA[19:12] : 8 bit stands for 256 items. L2 table block is about 4KB, thus the 8bit can express the whole 1MB.

VA[11:0] : 12 bit stands for 4KB offset. So L2 block can be addressed.

TTB is the base address of MMU translation table in the memory. It's stored in the CP15 C2 register.

Use the order to set the base address of MMU:

mrc 15, 0, r0, c2, c0, 0 /* get the TTB for cp15 c2 */

Translation table: 4096 items, each item stands for 1MB, occupied for 4096* 4byte=16KB

Coarse page table: 256 item for each item in Translation table, each item stands for 4KB. Occupied for 256*4Byte= 1KB

Small Page: 4KB in total , use VA[11:0] to locate the byte. The information is not save as a table, so occupy no memeory extra.

Total memory occupy of the MMU IS :

L1 TABLE: 4096*4byte=16KB

L2 Table: 256*4byte=1KB

Total =16KB+1KB*4096=16KB+4MB

As we know , the L1 item pointer to L2 table base address. To express a 16KB table , L1 Table , we need 32-14=18bit , that is , the TTB need 18 bit to save the information of base address of L1 table. Thus the C2 register of TTB is 18-long .

To Express the L2 1KB table , we need 32-10=20 bit to save the information of base address of L2 base table.

Thus , we need 20 bit to save the base address of L2 table and keep 12 bit for other useage. The left 12 bit is necessary for usage such as: access permit, domain control and so on.

We have the following 4 type of format in L1 table , which is called section level 1 descriptor:

As you can see, 4 types is as follows:

- No L2 table , the descriptor[1:0] is 0b00;

- Pointer to a Coarse page, that is 1KB, need descriptor[31:10]=22 bit. Aligned with 10bit=1KB

- Pointer to a Fine page, that is descriptor[31:12]=20bit, aligned with 12bit=4KB

- Pointer to a Section page, that is descriptor[31:20]=12bit, aligned with 20bit=1MB

Each L2 page has a Domain to control the access permit.

Why Section Page need a extra AP and C/B bit?

As the section page need no L2 page table at all. The Section base address is physical address, that means the access control must done in L1 Descriptor as no L2 Descriptor exist.

If the end bit of L1 descriptor is 0b01 or 0b11 , that's the coarse page or fine page, the L2 descriptor have the following 4 types in the same way:

- Pointer to no physical space end with 0b00

- Pointer to Large Page 64KB: need L2 descriptor[31:16] to express the base address

- Pointer to Small Page 4KB: need L2 descriptor[31:12] to express the base address

- Pointer to Tiny Page 1KB: need L2 descriptor[31:10] to express the base address

Actually, the

Means the L1 table is 1MB and L2 table is 4KB.

If you want to use other format such as L1 table is 1MB and L2 table is 16KB, you need to specify the corresponding VA format.

This is about the whole table –query proess:

Section page query process:

Coarse page query process:

Now describe the total process with L1 cache, you should nofity that the address In L1 is about virtual address but not physical.

- Data exist in cache

The CPU send a VA to D-cache and return with the cache data.

- Data not exist in the cache BUT TLB has the MMU buffer

CPU send the VA to D-cache but no match returned.

Then the VA is sent to TLB , a physical address buffer is found out and then send the PA to memory to get the data.

Meanwhile, some other data side will be prefetch by the cache .

- Data not exist in the cache and no TLB buffer found

NO cach and no TLB, so the MMU WILL access the memory by 3times to get the physical address and fetch the data to cpu.