1、使用FPGA做为外部控制器的总线译码时,将总线时钟接在全局时钟脚上(MRCC),就算接在了局部时钟(SRCC)上,也要通过BUFG转为全局时钟走线,否则会因为local clk到各部分的时延较大引起各种问题(时序不稳、观测信号无法正常加载等,血泪教训!)

2、VIO使用时要注意IO及信号走向要在同一时钟域,一个VIO的信号跨时钟域会带来不可预知的问题(时序、时序!!!)

3、使用XDC文件可以改变FPGA启动时的时钟频率和压缩生成的bit文件大小,可大幅加快逻辑加载

4、每个always语句尽量只干一件事!使用FIFO的empty信号作为标志位控制状态机切换及为某一信号赋值,状态机正常切换了,赋值延迟了一个时钟。。怀疑是因为always里的敏感信号是普通信号的原因(always @ (posedge i_clkt),i_clkt为逻辑中产生的时钟);

5、运算符使用

You're already familiar with bitwise operations between two values, e.g., a & b or a ^ b. Sometimes, you want to create a wide gate that operates on all of the bits of one vector, like (a[0] & a[1] & a[2] & a[3] ... ), which gets tedious if the vector is long.

The reduction operators can do AND, OR, and XOR of the bits of a vector, producing one bit of output:

& a[3:0] // AND: a[3]&a[2]&a[1]&a[0]. Equivalent to (a[3:0] == 4'hf) | b[3:0] // OR: b[3]|b[2]|b[1]|b[0]. Equivalent to (b[3:0] != 4'h0) ^ c[2:0] // XOR: c[2]^c[1]^c[0]

These are unary operators that have only one operand (similar to the NOT operators ! and ~). You can also invert the outputs of these to create NAND, NOR, and XNOR gates, e.g., (~& d[7:0]).

6、在使用DSP资源时采用同步复位,这样可以充分使用其中的register资源,对于FPGA资源耗用和性能上都有益。

而使用Block RAM中register资源与DSP类似,复位方式也需要是同步综合器才能识别

7、发现新大陆,Vivado中的时序错误都处理了之后编译速度会很快很快很快很快,结论:编译慢都是在检查时序?!。

8、遇到3个microblaze烧写后只有一个能跑起来的问题,另2个在SDK中Debug是正常的,只是elf遍进bit文件烧写进FPGA后无法运行,待解决(2019年4月27日)--原因已找到,MB已运行,只是双口一直在被CPU占用,MB端无法写入握手信息。

9、代码风格不好的module,多次例化很容易被优化!!!!!!!你以为Verilog是C吗?

10、紫光同创CPLD 生成sbit文件时选择压缩,83K-->68K,启动时间缩短1.3ms(6.3-->5ms).

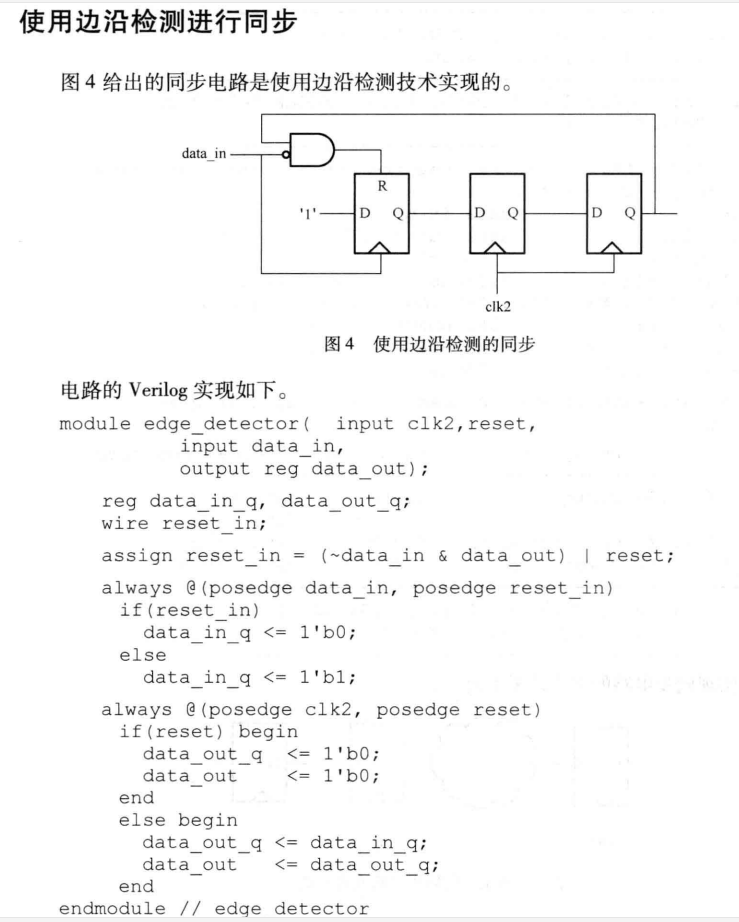

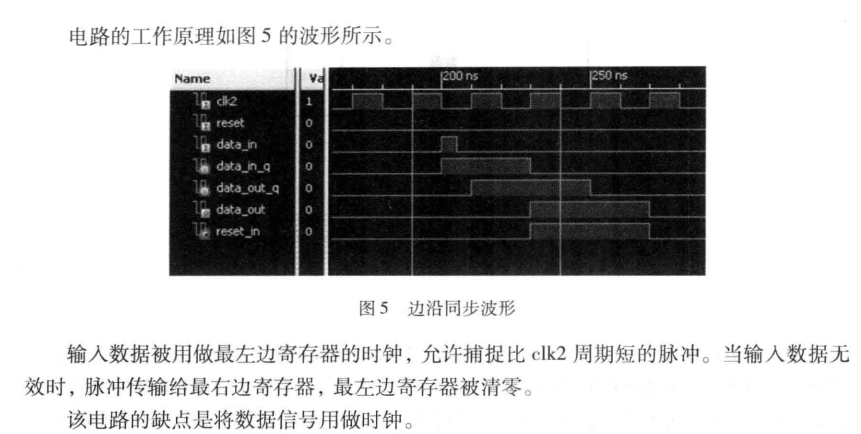

11、低速时钟同步不足一个时钟周期的信号