在给标志信号命名时,标志位命名为...._sig表示,,比如shift_done_sig 表示。。。的标志位

在程序中怎么写输出标志位

两种方法:

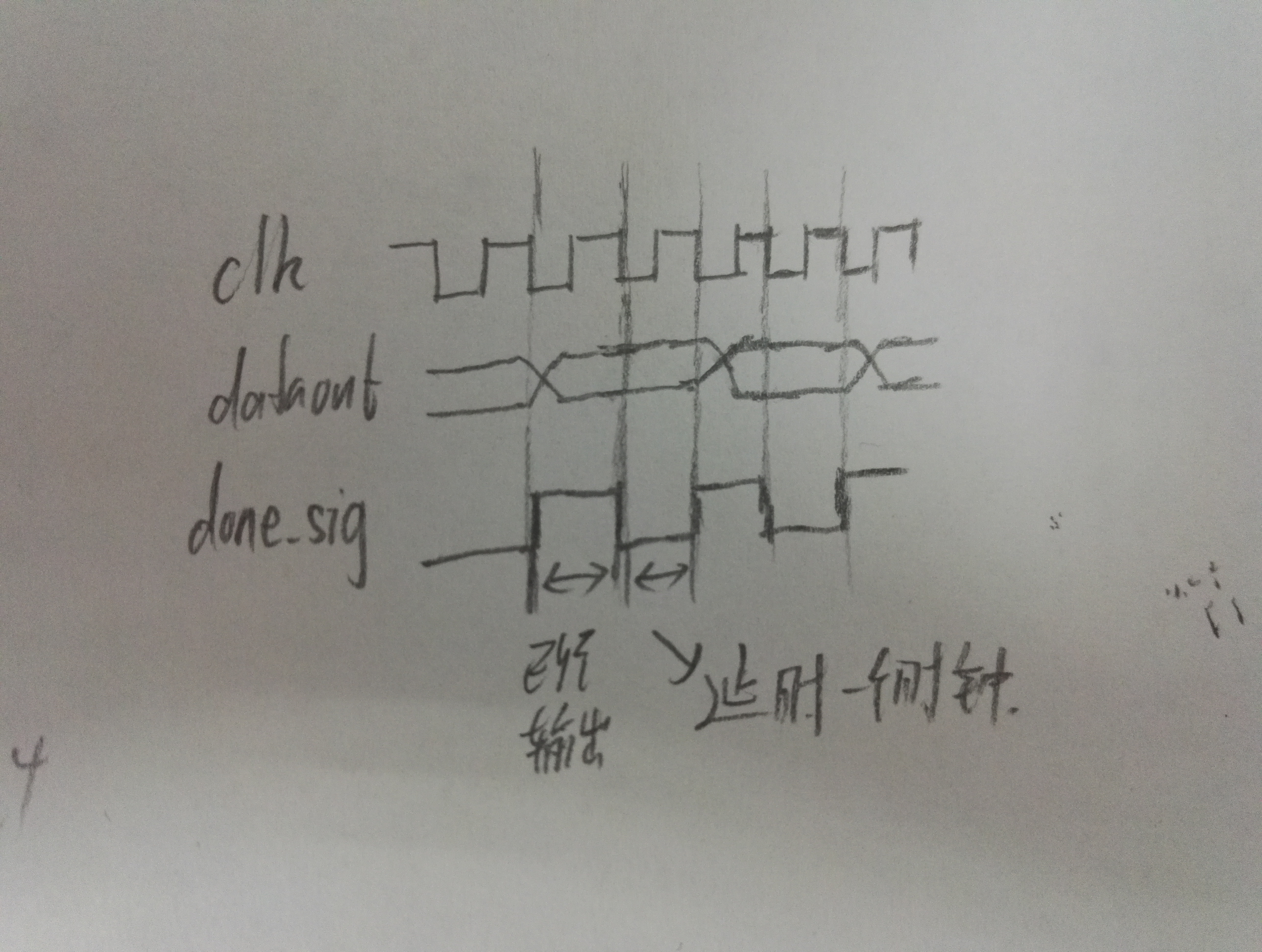

1.先不带标志位仿真,判断输入到输出需要几个时钟

然后如果立刻输出的话那就只能延长输出时间去空出一段时间给标志位电平变化的时间,通过寄存器在时序模块中不断使用非阻塞赋值来延时。在延时的这段时间标志位可以赋值为低,最后输出数据的那个时钟赋值为高,这样就产生了标志位高低电平变换,可给后面的模块拿来判断前一个模块是否完成输出。

2.还有一种方法 如果状态很多的话可以是使用状态机,在每一个状态中可以去定义标志位状态,比如在中值滤波中不断排序就可以使用状态机。