注:以下内容学习于韦东山老师arm裸机第一期视频教程

一. 2440时钟简介

1.1 2440是一个SOC(system on chip)系统,不仅有很多CPU,还有很多外设,在2440芯片手册有系统框架图如下:

2440框架图中,不仅有CPU,而且有很多外设,其中外设分为两部分,一部分是AHB总线,一部分是APB总线

1.2 AHB总线

1.2.1 LCD控制器

1.2.2 USB控制器

1.2.3 NAND控制器

1.2.4 内存控制器

1.2.5 摄像头接口

1.2.6 中断控制器

1.2.7 电源管理等等

1.3 APB总线

1.3.1 UART

1.3.2 USB device

1.3.3 I2C

1.3.4 GPIO

1.3.5 RTC

1.3.6 ADC

1.3.7 定时器等等

1.4 因此引入了三个时钟,FLCK,HCLK,PCLK

cpu工作与FCLK,最大工作频率400MHZ

AHB总线工作于HCLK,最大工作频率136MHZ

APB总线工作与PCLK,最大工作频率68MHZ

二.时钟的获取

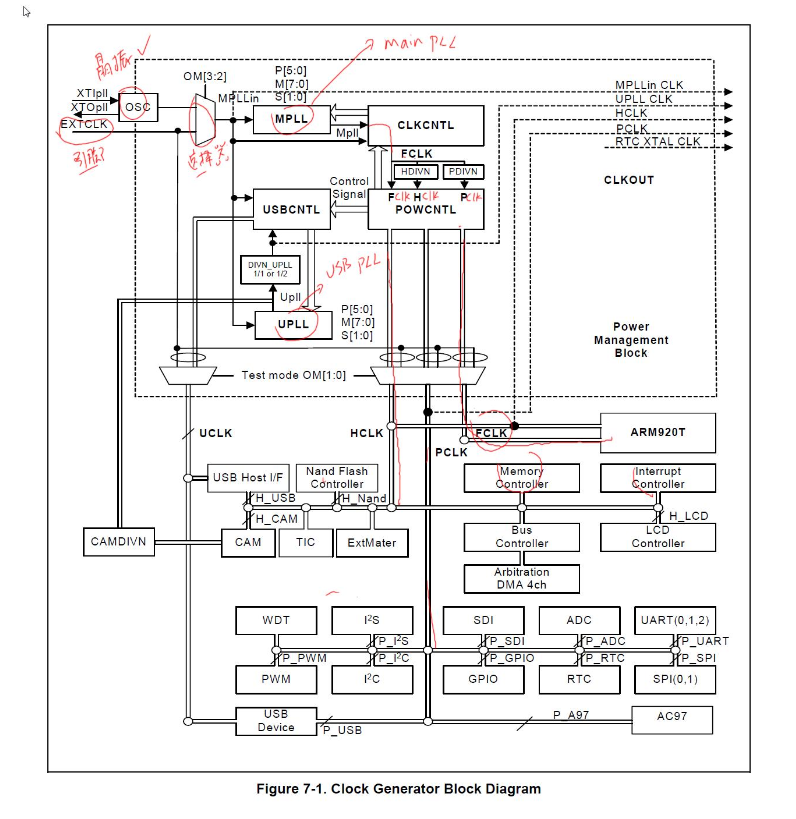

2.1 2440时钟体系框图如下

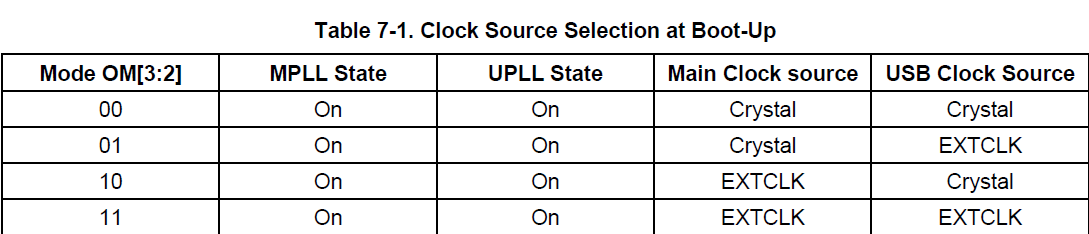

2.2 时钟源的选择

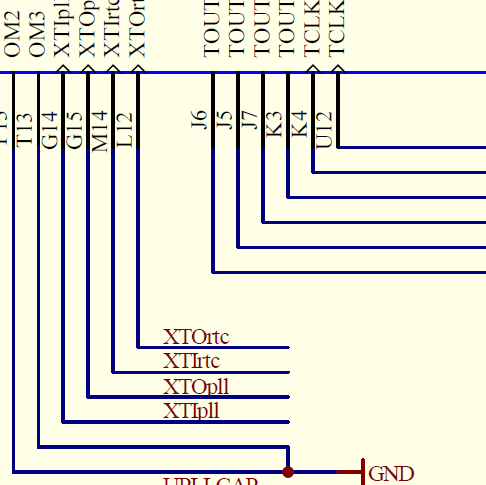

从图中看出,时钟源有两个分别是外部晶振和引脚,通过OM[3:2]来选择,模式选择如下图

在2440的原理图上,可以看到OM3,OM2都接到了GND上,因此会选择使用外部晶振作为输入

2.3 时钟体系流程

12MHZ晶振通过MPLL锁相环得到FLCK,CPU直接使用FCLK,FCLK通过PDIV分频得到PCLK提供给APB总线上的设备使用,

FCLK通过HDIV分频得到HCLK提供给AHB总线上使用

12MHZ晶振也会经过UPLL锁相环提供给USB使用

三.程序的编写

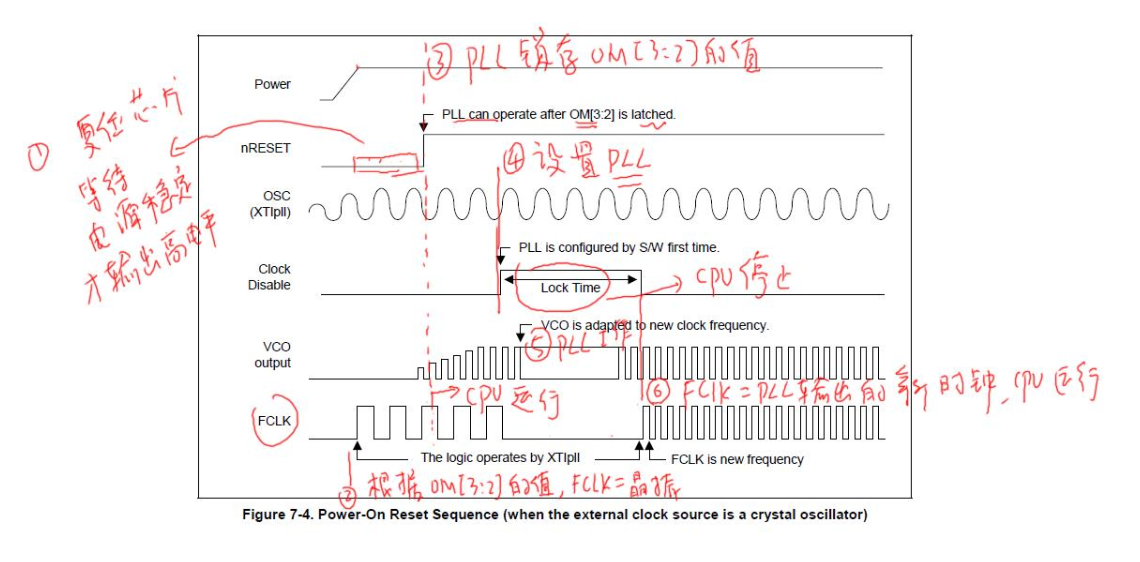

3.1 时序图如下:

注:一旦设置PLL,就会锁定LOCK TIME 直到PLL输出稳定,然后CPU开始工作于新的频率FCLK

3.2 流程分析

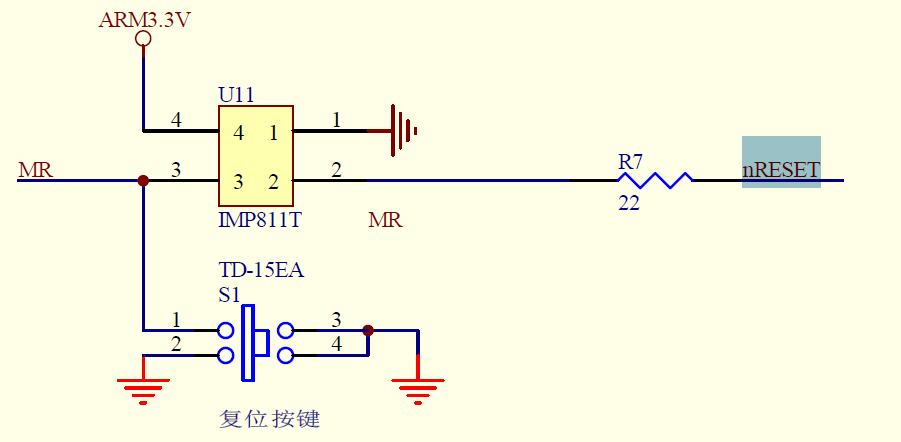

3.2.1 一上电,复位引脚会维持一段时间(等待电源稳定),通过复位芯片来维持,如下:

3.2.2 根据OM[3:2]的值FCLK等于晶振的12M

3.2.3 PLL锁存OM[3:2]的值,同时CPU开始运行(复位引脚被拉高)

3.2.4 设置PLL

3.2.5 在CPU停止运行一段时间设置PLL

3.2.6 设置完成后FLCK等于PLL输出的新的频率

3.3 寄存器的设置(目的FCLK=400MZH, HCLK=100MZH, PCLK=50MHZ)

3.3.1 设置LOCKTIME寄存器,决定MPLL和UPLL的LOCKTIME

设置为默认值即可

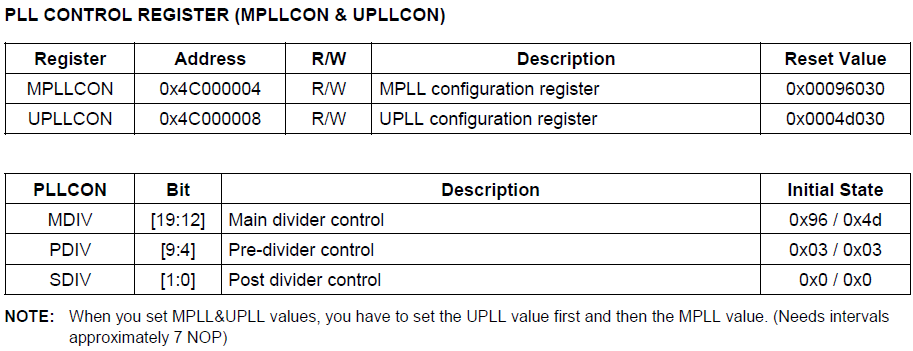

3.3.2 设置MPLLCON/UPLLCON寄存器,决定FCLKi,如下图

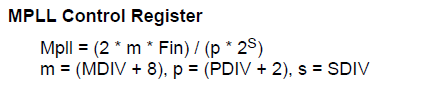

其中公式如下图:

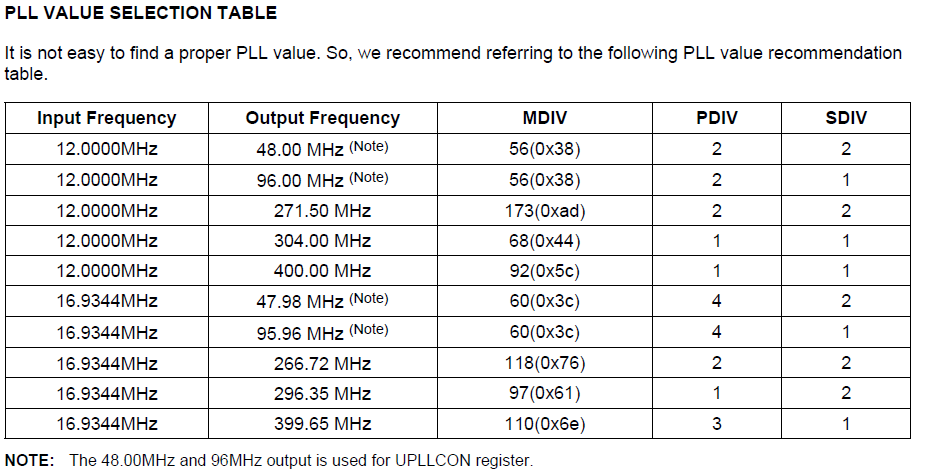

参考设置值如下,我们选择MDIV=92, PDIV = 1, SDIV=1即可设置FCLK = 400MHZ:

MPLLCON = (92 << 12) | (1 << 4) | (1 << 0);

3.3.3 设置CLKCON寄存器(关掉用不到的设备)

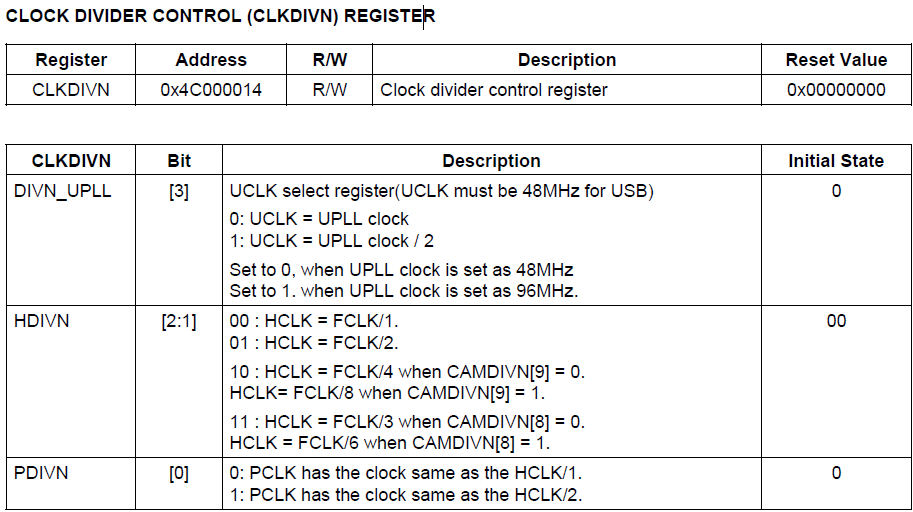

3.3.4 设置CLKDIVN寄存器,决定HCLK,PCLK,如下图:

首先要设置bit[2:1]为10,这时HCLK=FCLK/4=100MHZ,但是需要CAMDIVN[9]=0(默认值就是0)

设置bit[0]为1,这时PCLK=HCLK/2=50MHZ

bit[3]取默认值

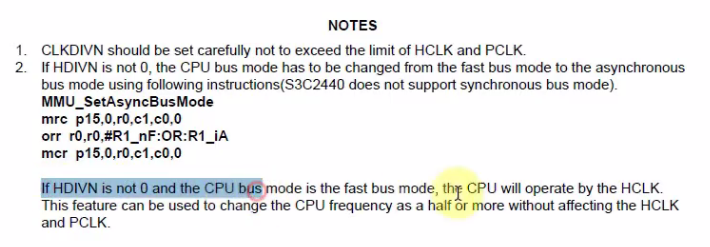

3.3.5 如果HDIVN不等于0,CPU必须设置为异步模式,CPU会工作于HCLK,如下图

对于此处的汇编命令 orr r0,r0,#R1_nF:OR:R1_iA ,查阅相关资料大概了解了一下:【它扯到了协处理器P15的C1寄存器】可以参考以下地址了解协处理器P15(https://www.cnblogs.com/lifexy/p/7203786.html)

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000;R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

3.3.6 提高系统时钟代码如下(FCLK=400MHZ,HCLK=100MHZ,PCLK=50MHZ):

.text

.global _start

_start:

/* 1.关闭看门狗 */

ldr r0, =0x53000000

ldr r1, =0

str r1, [r0]

/* 2.设置时钟 */

/* 2.1 设置LOCKTIME(0x4C000000)=0xFFFFFFFF */

ldr r0, =0x4C000000

ldr r1, =0xFFFFFFFF

str r1, [r0]

/* 2.2 设置CLKDIVN(0x4C000014) = 0x5 FCLK : HCLK : PCLK = 400m : 100m : 50m*/

ldr r0, =0x4C000014

ldr r1, =0x5

str r1, [r0]

/* 2.3 设置CPU处于异步模式 */

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000 /* #R1_nF:OR:R1_iA */

mcr p15,0,r0,c1,c0,0

/* 2.4 设置MPLLCON(0x4C000004)=(92<<12) | (1 << 4) | (1 << 0)

* m = MDIV + 8 = 100

* p = PDIV + 2 = 3

* s = SDIV = 1

* Mpll = (2 * m * Fin) / (p * 2 ^ s)= (2 * 100 * 12) / (3 * 2 ^ 1) = 400MHZ

*/

ldr r0, =0x4C000004

ldr r1, =(92<<12) | (1 << 4) | (1 << 0)

str r1, [r0]

/* 一旦设置PLL, 就会锁定lock time直到PLL输出稳定

* 然后CPU工作于新的频率FCLK

*/

/* 3.设置栈

* 自动分辨NOR启动或者NAND启动

* 向0地址写入0,在读出来,如果写入则是NAND,否则是NOR

*/

ldr r0, =0

ldr r1, [r0] /* 读出原来的值备份 */

str r0, [r0] /* 向0地址写入0 */

ldr r2, [r0] /* 再次读出来 */

cmp r1, r2

ldr sp, =0x40000000 + 4096 /* nor启动 */

moveq sp, #4096 /* nand启动 */

streq r1, [r0] /* 恢复原来的值 */

bl main

halt:

b halt