Avalon 总线广泛应用于外设和软核或者硬核交互,其时序简单明了,也非常适合用来作为划分模块的接口信号。本文结合quartus 关于 avalon 总线英文原版做简单介绍,重点理解时序即可。欢迎大家一起交流,Q群:912014800。

1.Avalon的时钟和复位

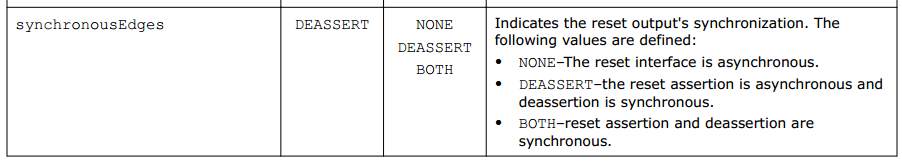

这里没什么好讲的,时钟信号略,而对于复位信号,可能有三个选择:

NONE: 复位是异步信号

DEASERT : 复位发生异步,复位释放同步

BOTH: 复位释放和发生都是同步信号

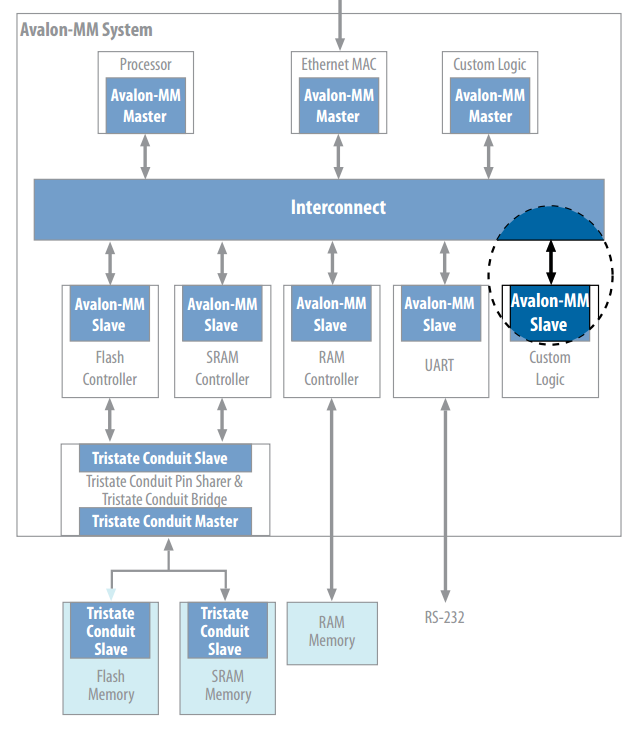

2.avalon M-M接口

这个接口比较重要,这个接口一般用于读写,可用在主从之间的元件上。全名,Avalon Memory-Mapped,阿瓦隆内存映射接口。

先看一个图:

如上图所示,Avalon MM mastet 通过内部桥连接Avalon MM slave,就是主连接从,其次下方有很多设备,比如uart来讲,对于Avalon mm slave来讲,一端连接到桥上,另一端连接到真实的串口。其他外设均类似。

那么这个接口的时序是什么样子的呢?其实不同的外设,其时序也少许差别,不过大同小异,以下举几个例子说明该接口的时序:

E1:

如上所示:发出读请求read和地址address的同时需要看等待信号waitquest是不是高,若是高,则表示需要等待,若是低,则表示可以进行读操作。

之后过一定的时钟节拍,会返回读数据readdata和readdatavalid读数据信号。(比较简单,写也是如此,当然这只是我们比较熟悉的情况。)

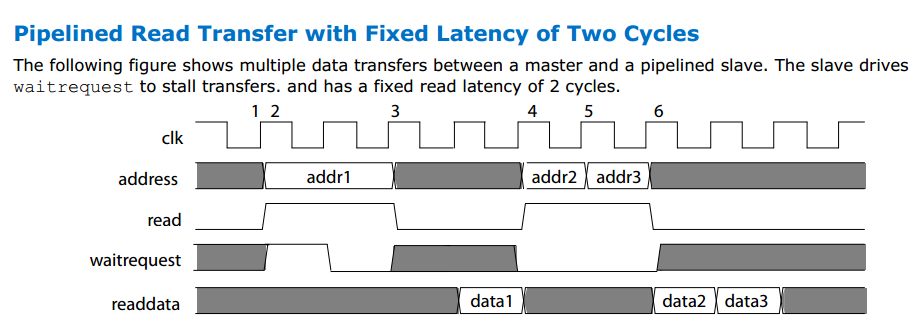

E2:基于以上基础,请看下图,改图表示读请求有效之后,固定两个clk的延迟出读数据,可自行理解。

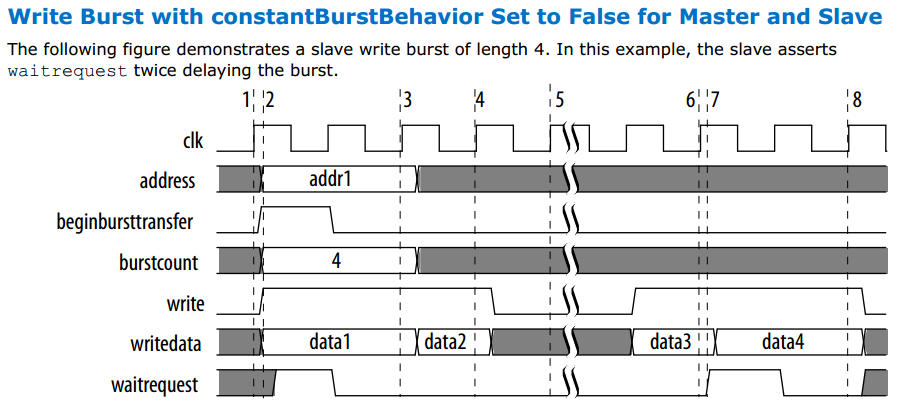

E3: 写突发操作

如上所示,在发出第一个写请求有效的同时(waitquest=0),会有burstcount=4和beginbursttransfer=1,这里burstcount表示此次写突发操作写几个

数,而beginbursttransfer表示第一个数,其他信号定义和之前类似,此处不再赘述,上图表示写突发操作为4个长度,这里需要注意的是,第一个数据在第一次waitquest=0,写第一个数据。

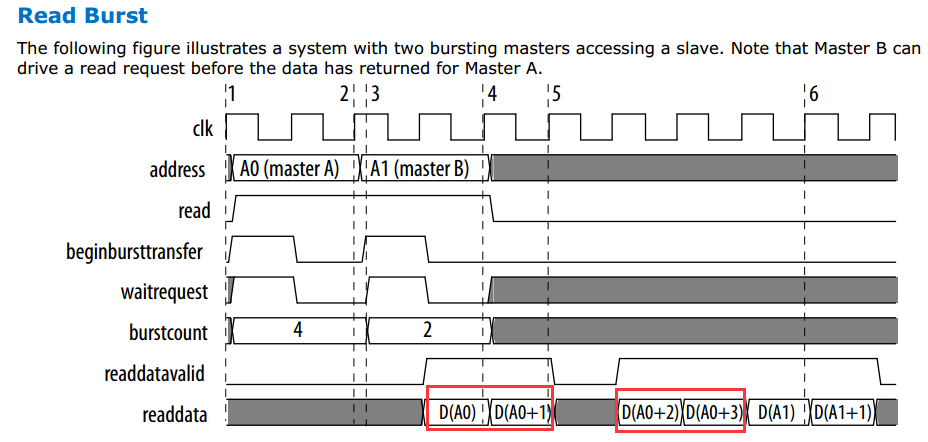

E4:读突发操作:和写类似。

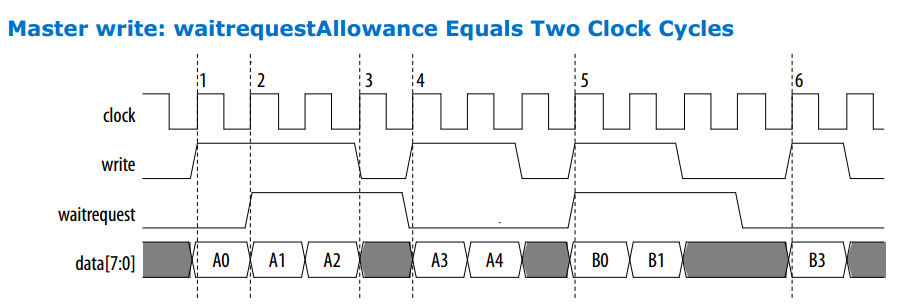

E5:写容忍两个:

如上所示:即使waitquest信号等于1,由于设置可以容忍两个写数据,因此A1 和A2仍然可以写道slave里面。

就介绍这么多吧,还有一些信号没有介绍,笔者也没有遇到过,到时候在补充吧。

3.Avalon 中断接口

中断接口相对简单一些,当发生什么事件时,拉高该信号即可,但是有时候可能会有几个中断同时来,那么就需要一个优先级。

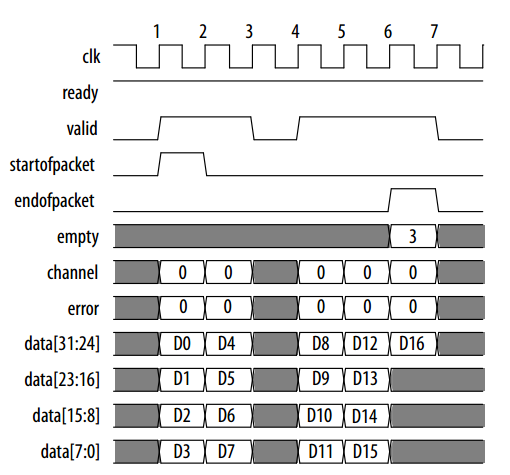

4.AvalonStreaming Interfaces ,简称Avalon ST接口

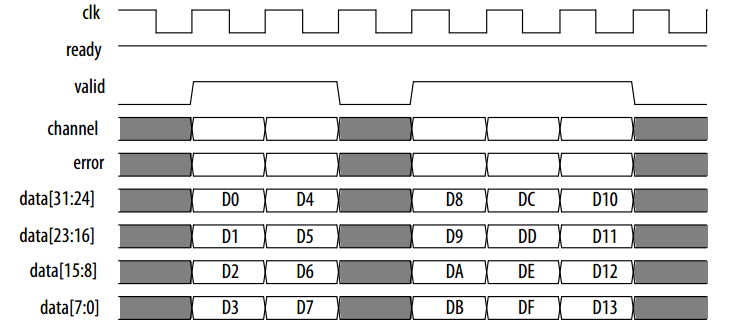

E1:当ready信号准备好后,便可以传输数据,其中通过valid信号来指示信号的正确性,通过error和channel来选择那个通道以及是否错误。

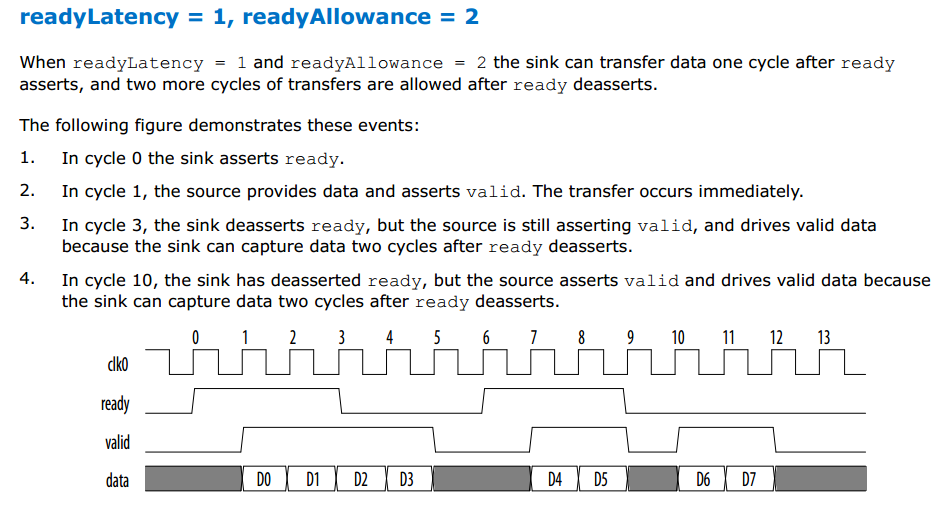

E2:读准备好延迟=1,读准备允许=2

如上所示:单ready=1时,由于有一个clk的延迟,因此需要等待一个clk后在传输数据,由于其ready的容忍是2,因此即使ready已经为0了,

user仍然可以传输两个数据D2 和 D3.

E3:包传输,包传输就是在数据传输的过程中,加入起始(start of packet)和结束指示信号(end of packet),其中也可以加入ready信号,

empty信号(有几个空,也就是无效),channel和错误信号,如下所示。

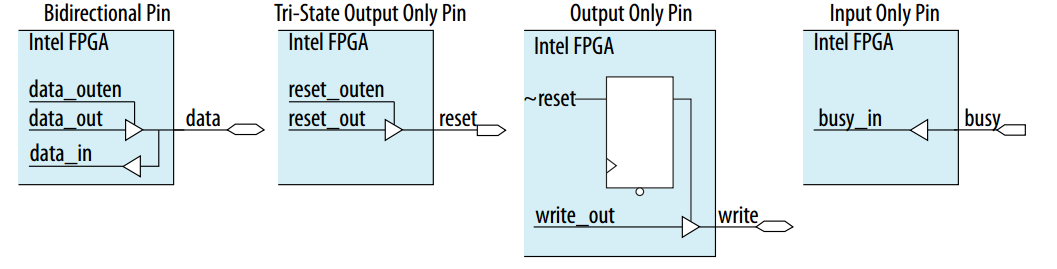

5.Avalon conduit 接口

用来导出作为和外部连接的接口或者给其他模块用。比如和外部sdram连接,或者和外部串口相连接。主要分为两类,比如给其他模块用的内部信号

和与外部真实物理器件相连接的信号。

6. Avalon 三态 conduit 接口,这里笔者也没怎么用过。。

总结:熟悉avalon MM和avalon ST总线的一些时序,很多IP核对user的接口都是基于avalon总线的,比如sdram ,ddr2,ddr3,uart,mac,方便user从另一个角度理解和使用IP核,实际使用IP时,可以参考仿真,快速熟悉接口时序,从而将该IP核使用起来。本文并没有将上述图中的信号的定义列出,如需要熟悉,请参考官方文档。