本文通过Avalon-MM Master Templates实现读取ddr2中的图像数据(800*480*16bit),然后通过TFT 5.0寸LCD显示出来。本文旨在阐述清楚思路以及记录自己在实现过程中的一些经验。

需要知识:NIOS + Verilog + 工具[Qsys]。

一.效果展示:

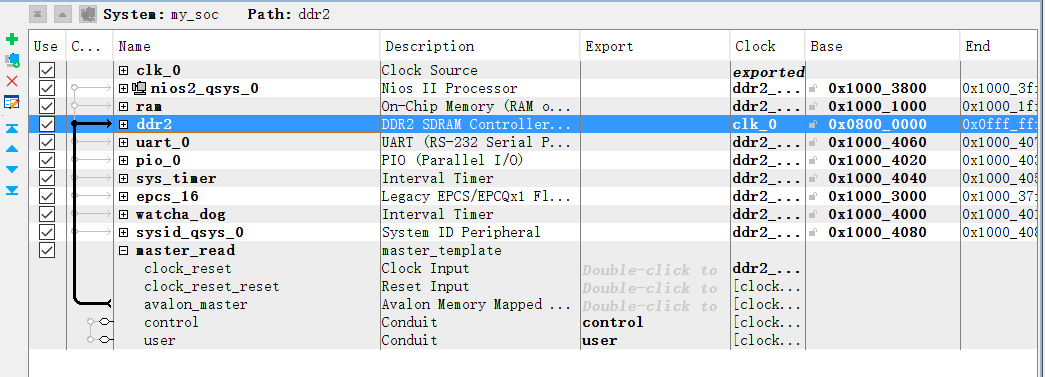

二.结构说明:

通过master_read 连接到ddr2,直接读取ddr2的数据。NIOS中负责写数据到DDR2,NIOS和MASTER_READ共享内存,关于mater_read的配置请参考之前的调试记录。我们的思路是在NIOS中用C直接操作内存,然后通过master_read读取数据送给TFT(此部分verilog实现),屏幕刷新率60hz。

三.图像转换说明

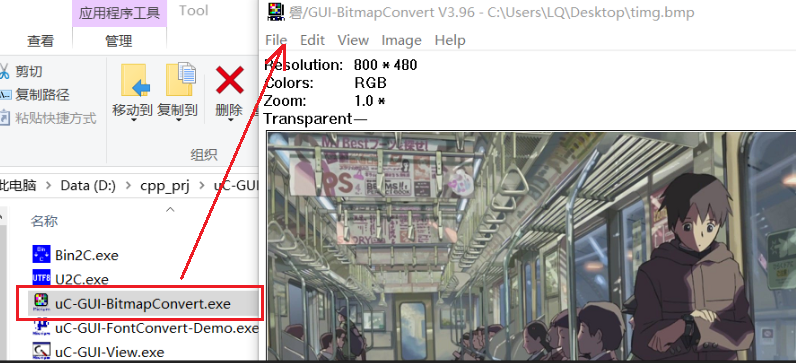

由于在NIOS是通过直接操作内存显示图片的,因此需要将图片转化为数组,具体如下:

1.打开uc_gui自带的工具,打开图片,(注意图像的分辨率,要提前改好)

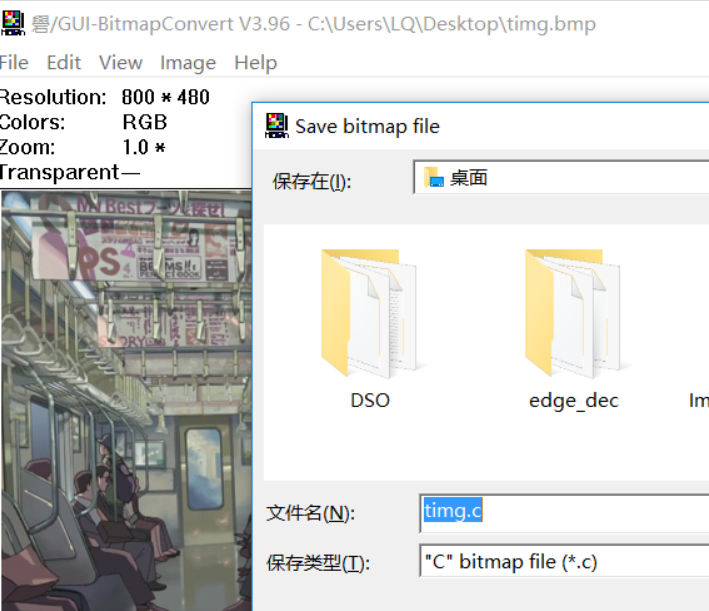

2.保存图片

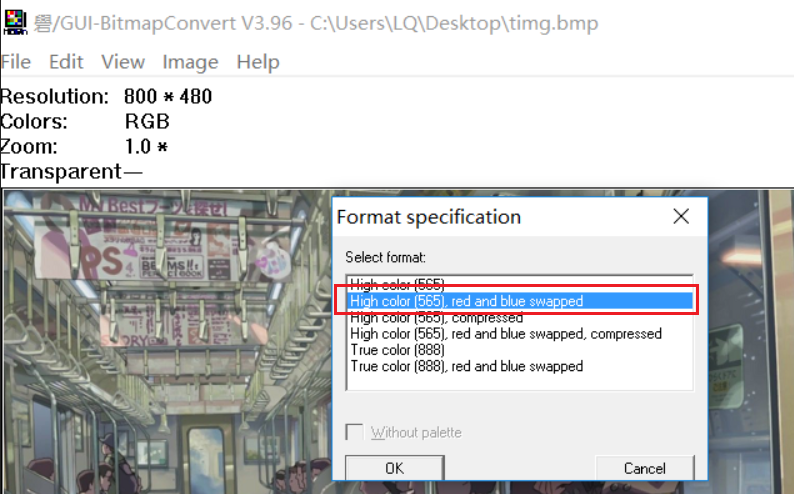

3.点击保存后出现如下框,存储的应该注意的地方情况红色框,交换红色和蓝色,(注:我用的是屏幕参数是RGB565,800*480 LCD,根据自己屏幕修改即可)。

四.部分调试波形记录

我在调试过中发现一个很奇怪的问题:如下

如上图的紫色框,笔者发现:使第一个数据输出0x1234,但是实际抓到的0x1234总共持续了4个clk,前面三个clk的数据应该是丢弃的,因此,笔者使用计数器在每次读数据前先读三次(修bug),然后图像就可以正常显示了。

五.总结

本文展示了一个通过NIOS实现数据流处理的例子,需要的可以参考。这样的好处,成功绕过操作DDR2/3等缓存器件,减小开发难度,减小开发周期,缺点是牺牲了一点点的速度优势,毕竟verilog是纯硬件再跑。。。欢迎大家一起交流,Q群:912014800。